电子设计领域的单片机/CPLD自动化控制

可编程逻辑

描述

自20世纪80年代单片机引入我国以来,学习和应用单片机的热潮始终不减,特别是MCS51系列。这是由单片机的特点决定的。实际上,从单片机/CPLD应用通用数字集成电路系统,到广泛应用单片机,是我国电子设计在智能化应用水平上质的飞跃。据统计分析,单片机的销量单片机/CPLD到目前为止依然逐年递增,而且在很长一段的时间内,单片机依然会是电子设计的主角(虽然这一地址已经受到了CPLD的挑战)。

1 纯单片机系统优缺点

①大量单片机/CPLD的外围芯片和接口电路使得单片机应用系统的设计变得简单而且快捷,新型单片机的上市和高级语言的支持(如C51)进一步延长了单片机的寿命。

②长期稳定的发展和使单片机性价比非常高,而且单片机/CPLD积累了大量的资料并拥有了大量的工程技术为员。这一点是CPLD目前难以达到的。

但是,单片机的缺点也有目共睹:

①低速。即使是高速度单片机也只能工作在μs级,这是由单片机串行工作的特点所决定的。

②低可靠性。虽然单片机/CPLD目前有很多器件与设计在一定程序上解决了部分问题,如看门狗的广泛应用,但在某些情况下瞬间的复位也会造成严重后果。

2 纯CPLD设计的优缺点

即使单纯单片机/CPLD的单片机结构能完成的功能,在某些情况下也宁可使用纯数字电路完成。而当前开始流行的CPLD,则不但克服了单片机的缺点,而且由于可采用VHDL语言编程,进一步单片机/CPLD打破了软硬件工程师的界限,加速了产品的开发过程,使纯数字电路的设计变得简单。人们甚至在讨论用C作为下一代硬件描述语言。

难怪有专家指出,电子设计的单片机时代即将过去,而以PLD为核心的EDA(电子设计自动化)将是单片机/CPLD未来设计的方向。由于超大规模集成电路技术的发展,单片PLD芯片上已经可以集成上百万门,就系统规模而言,将单片机设计在内也没什么问题。美国的可编程器件厂商已经以软核和硬核嵌入两种形式(将单片机电路嵌入PLD)为设计人员提供帮助。PLD器件取代单片机是早晚的事。但是,在我国当前的普遍应用中,单纯依靠PLD器件还有点早,原因如下:

①由于历史单片机/CPLD的原因,我国的电子设计人员大部分应用的是MCS51系列单片机,还没听说哪家公司提供软核或硬核集成。而让这么多人改学其它系列单片机还需要一段时间,而且原有的程序更使人不愿改动。

②单片机价格低廉,而PLD如果增加单片机内核的话,至少在目前形势下价格会比较昂贵。

所以,由于单片机和PLD的互补性,利用单片机加PLD的结构至少在近期内将一种较好的选择。下面通过作者设计的实例,介绍MCS51+EMP703S结构体系的特点及注意事项。

3 单片机+CPLD结构体系设计实例

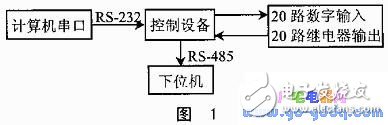

本设计用于单片机/CPLD自动化控制,设计要求如图1所示。

对于一个熟悉单片机系统设计的工程师而言,上述设计不会有技术上的困难,问题在于:

①要用两个全双工串口;

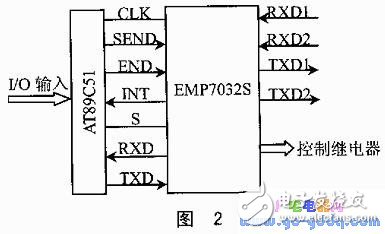

②要求比较多的输入输出口。如果用传统设计方法,势必要用比较多的芯片,电路板的设计也较麻烦,一旦设计有误,必须重新设计整个电路板,费时、费力、费钱。而采用MCS51+EMP7032S设计后,基本上做到了模块化设计,电路的修改只是编程而已。从开始设计到定型所用的时间,基本上就是制作电路板的时间。由于设计了输出信号锁存,完全避免了单片机程序跑飞和看门狗复位所引起的输出的跳变,这时设备完全至关重要。图2是设计原理电路图。

从设计的原理图可以看出,主要部分单片机/CPLD只需要两片集成电路:单片机AT89C51和CPLD——EPM7032S,并且电路板采用模块化设计,预留了扩展接口,只需要配上不同的处理模块,就可以实现数据采集、键盘扫描、显示驱动和继电器控制等许多功能。单片机和EPM7032S之间采用了类似SPI接口的通信方法。如图2所示。采用这种方法,既实现了单片机和CPLD之间的通信,又具有灵活性,并且节约了大量的端口资源。

EPM7032S有36个I/O口,除去用于和单片机通信的7个端口,还有29个端口可以使用。可满足大部分对于端口扩展设计的需求。图3是为EPM7032编写的测试程序的波形仿真图。

图3中:CLK为同步时钟;SEND为数据接收;END为SEND信号的控制端;S为位选端,用业控制串行通信端口选择;RXD、TDX为单片机和EPM7032之间的串行通信端口;RXD1、TXD1、RXD2、TDX2为串行通信扩展口。这种方案,已经过多次检验,对于节省PCB板的面积和布线难度、提高设计可靠性和提高设计效率都非常有帮助。

单片机程序

sdosend:

setb clk

setb end

mov r7,#06h

ssend:

rrc a

mov send,c

nop

nop

clr clk

nop

nop

setb clk

djnz r7,ssend

nop

nop

clr end

nop

nop

setb end

ret

VHDL 语言程序

Library ieee;

Use ieee.STd_logIC_1164.all;

Entity pldse1 is

Port

(

so,clk,send :in std_logic

);

end pldse1;

architecture io1 of pldse 1 is

begin

process(cs)

begin

if(cs=‘0’)then

casep qout is

when “000000”=》

when “000001”=》

when “000010”=》

··················

when “000100”=》

when “000101”=》

when others=》null;

end case;

else null;

end if;

end procESS;

process(clk)

begin

if(clk‘event and clk=’0‘)then

qout《=data &qout(5 downto 1)

else null;

end if;

end process;

end io 1;

通过程序单片机/CPLD可以看出,利用CLK和SEND线发送控制信号;利用END作为结束位,无论什么情况,如果没有结束位的下降沿脉冲,PLD的输出端口不会改变,这样可确保输出信号的稳定。这种输出锁存使单片机在死机复位时依然不影响继电器原输出。PLD在接收到单片机的控制信号后首先暂存,直到收到END的下降沿脉冲时再把数据输出,作出相应的置高低电平的动作。

由上述设计可以看出,单片机和PLD在使用上有很强的互补性:在逻辑运算、智能控制方面,单片机具有不可替代的优越性;而在高速稳定等方面,PLD无疑是首选。因此,在目前的电子设计中,充分利用单片机+PLD结构将起到事半功倍的效果。

-

单片机在工业自动化中的应用2024-11-01 2646

-

电子设计自动化(EDA)是什么2021-07-29 2210

-

现代PCB设计人员的电子设计自动化2020-09-14 2987

-

电子设计自动化技术的概况及应用2020-07-14 3510

-

基于单片机的工厂自动化应用2019-07-16 3378

-

电子教案《新编电子设计自动化项目教程》2018-10-11 4241

-

电子设计自动化EDA绪论2016-12-11 867

-

单片机的主要应用范围和领域2013-12-23 4217

-

自动化的大神们进来指导指导。。2012-08-21 3053

-

基于单片机+CPLD的多路精确延时控制系统设计2010-12-16 779

-

单片机 的应用领域2010-09-06 5685

-

电子设计自动化SYNAPTICAD ALLPRODUCTS V9.92009-10-28 5803

-

单片机+CPLD结构体系在电子设计中的应用2009-05-14 496

-

电子设计自动化实验指导书2008-09-21 766

全部0条评论

快来发表一下你的评论吧 !