MS4553S——用于开漏模式和推拉模式的 2bit 双向电平转换器

电子说

描述

产品简述

MS4553S是一款双向电平转换器,可以用作混合电压的数字信

号系统中。其使用两个独立构架的电源供电,A端供电电压范围是

1.65V到5.5V,B端供电电压范围是2.3V到5.5V。可用在电压为

1.8V、2.5V、3.3V和5V的信号转换系统中。当OE端为低电平时,所

有IO端口为高阻态,降低了静态功耗。当VCCA上电后,OE端内部

集成了下拉电流源。为了确保在上电或下电过程中,端口保持高阻

特性,OE端应通过下拉电阻接地,下拉电阻的阻值由驱动电流源

的能力决定。

MS4553S采用SOT23-8封装,工作温度范围是-40°C到+120°C。

主要特点

■无需方向控制信号

■数据速率:推拉模式为20Mbps,开漏模式为2Mbps

■A端电压范围1.65V到5.5V,B端电压范围是2.3V到5.5V(VCCA≤VCCB)

■VCC隔离:如果任何一个电源拉到地,则端口呈现高阻态

■支持掉电模式

应用

■ I 2C/SMBus(系统管理总线)

■ UART(通用异步收发传输器)

■ GPIO(通用输入/输出)

产品规格分类

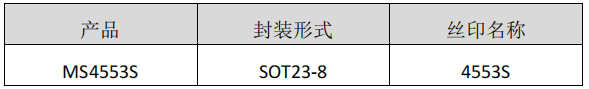

管脚图

如有需求请联系——三亚微科技 王子文(16620966594)

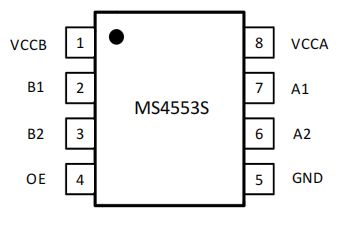

管脚说明

内部框图

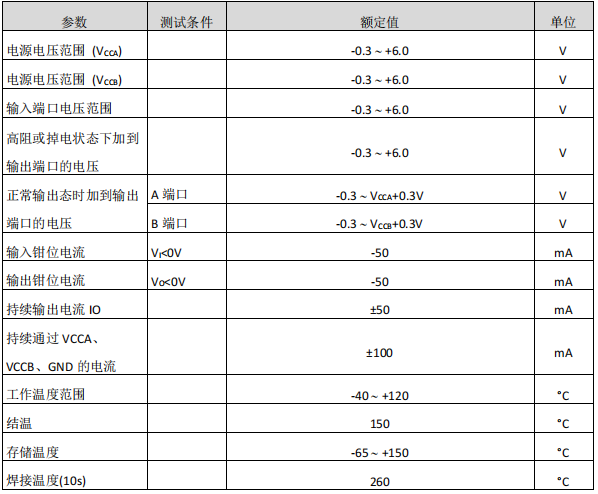

极限参数

芯片使用中,任何超过极限参数的应用方式会对器件造成永久的损坏,芯片长时间处于极限工作

状态可能会影响器件的可靠性。极限参数只是由一系列极端测试得出,并不代表芯片可以正常工作在

此极限条件下。

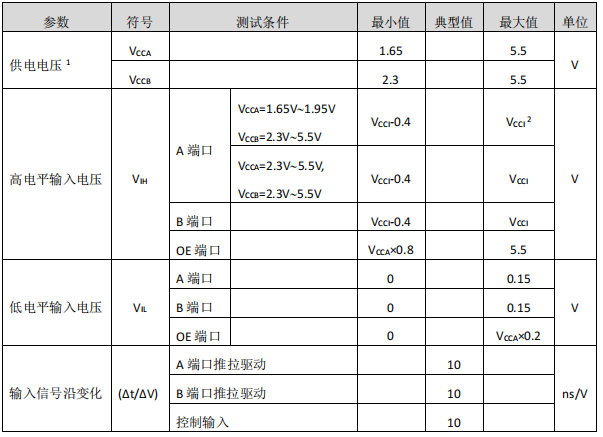

推荐工作条件

VCCA=1.65V-5.5V,VCCB=2.3V-5.5V,在 TA=25。C 情况下的典型值,除非另有说明。

注:

1. VCCA必须小于等于 VCCB,且 VCCA不能超过 5.5V。

2. VCCI是与输入端口相关联的 VCC。VCCO是与输出端口相关联的 VCC。

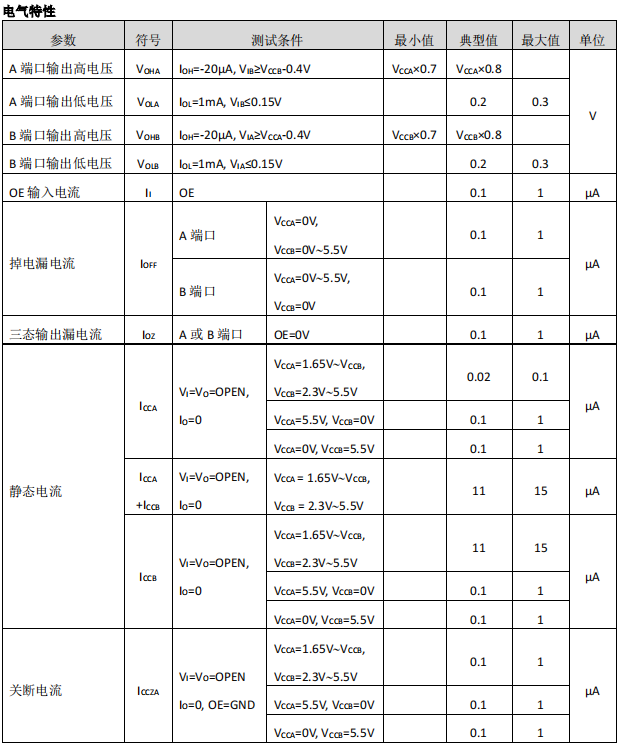

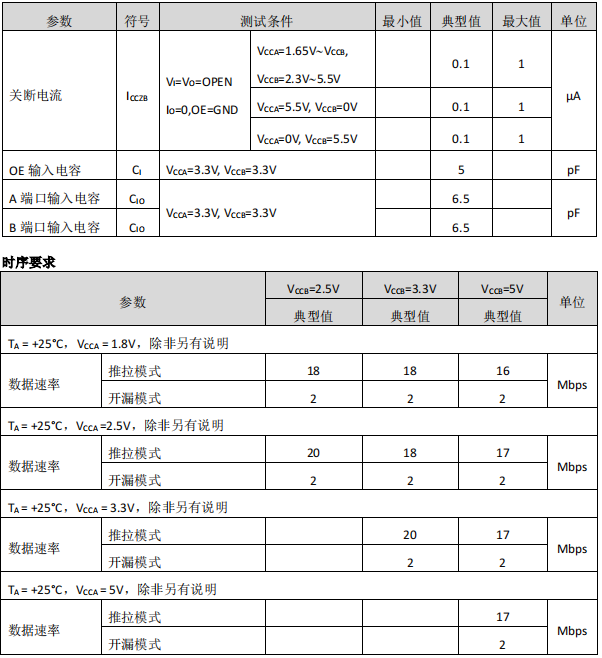

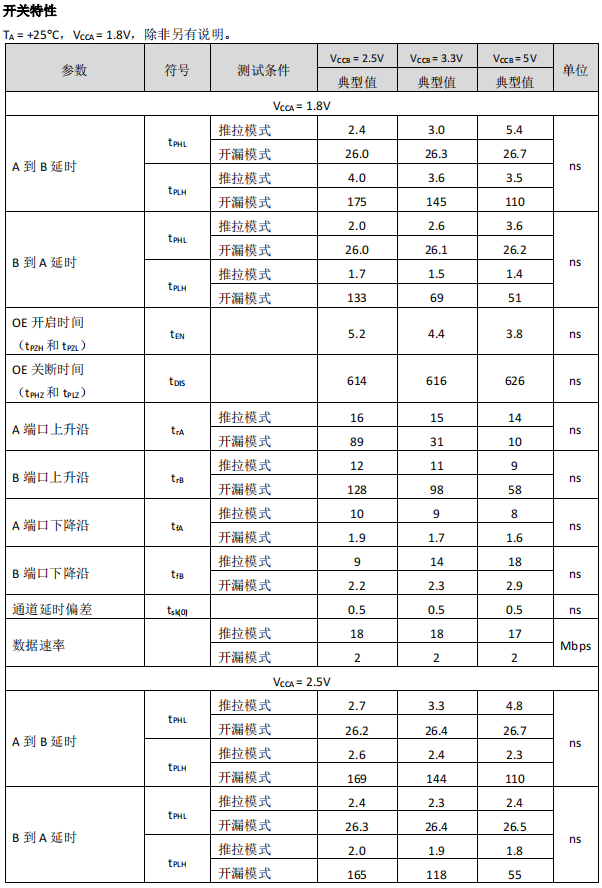

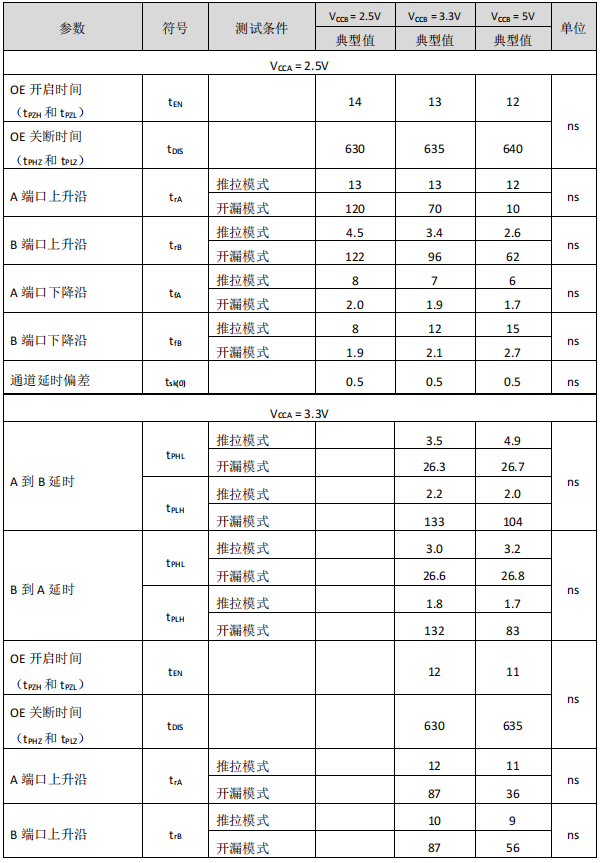

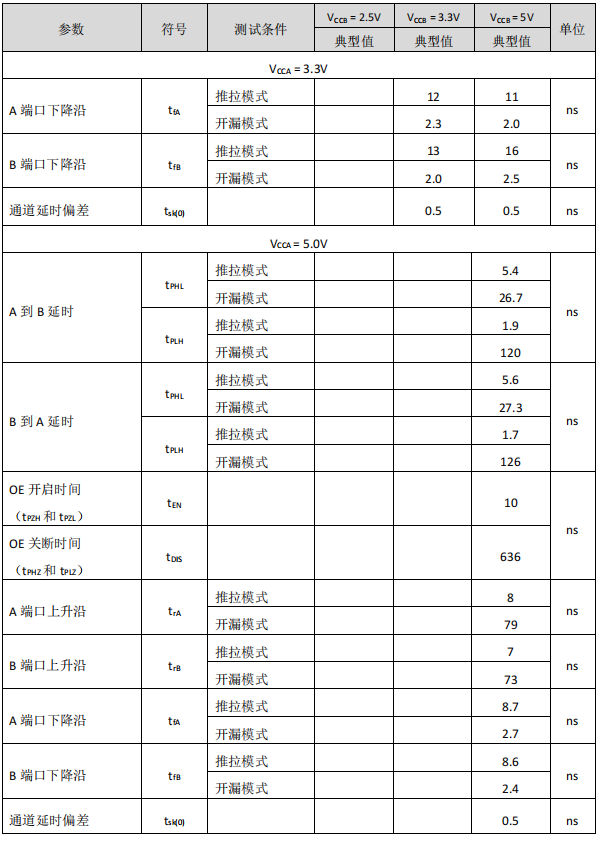

电气参数

VCCA=1.65V-5.5V,VCCB=2.3V-5.5V,在 TA=25。C 情况下的典型值,除非另有说明。

如有需求请联系——三亚微科技 王子文(16620966594)

如有需求请联系——三亚微科技 王子文(16620966594)

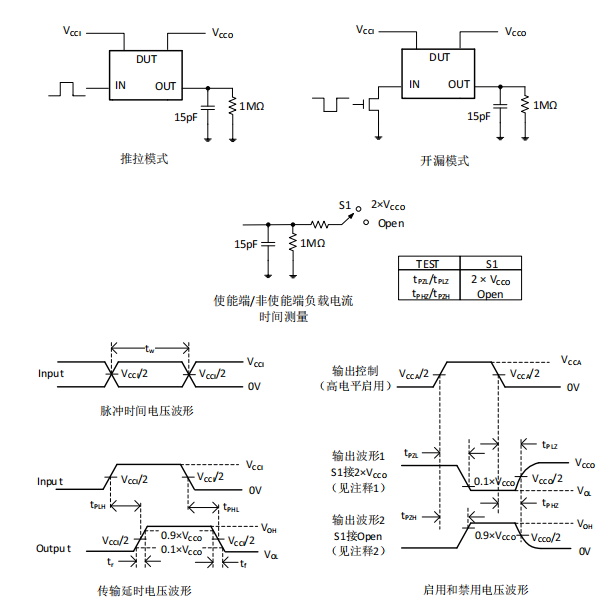

参数测试信息

注:1. CL包括探针和夹电容。

2. 波形 1 用于具有内部条件的输出,使输出为低电平,除非输出控制端关断。波形 2 用于具有内部条

件的输出,使输出为高电平,除非输出控制端关断。

3. 所有的输入脉冲由具有以下特性的发生器提供:PRR≤10MHz, ZO=50Ω,dv/dt ≥1V/ns。

4. 输出一次测量一次,每次测量都要转换一次。

5. tPLZ、tPHZ与 tDIS相同。

6. tPZL、tPZH与 tEN相同。

7. tPLH、PHL与 tPD相同。

8. VCCI是与输入端口相关联的 VCC。

9. VCCO是与输出端口相关联的 VCC。

10. 所有参数和波形并不是适用于所有设备。

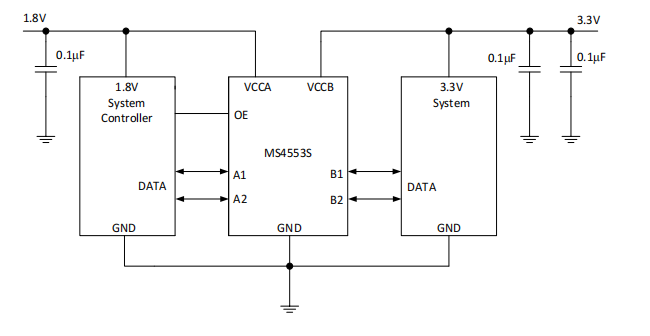

应用说明

MS4553S 可以用于桥接两个不同的电压节点,以成功连接电子系统中的逻辑门电平。它可以用在

点对点拓扑中,用于连接运行在不同接口电压下的设备或系统中。它的主要目标是用开漏模式与 I/O

口进行数据连接,例如 I 2C 和 1-Wire,数据是双向传输且不需要控制信号,也可以用推拉模式与 I/O 口

进行数据连接。

输入驱动需求

信号的下降时间(tfA, tfB)取决于外部驱动器的输出阻抗,且驱动器能够驱动 MS4553S 的数据 I/O

口。同样的,tPHL和数据速率也取决于外部驱动器的输出阻抗。tfA, tfB, tPHL的值和转换速率定义为,

假设外部驱动器的输出阻抗小于 50Ω 情况下的值。

上电

在运行期间,要保证 VCCA≤VCCB。在上电运行期间,每个电源的排序不会损坏设备,因此可以先提

升任意一个电源。

输出负载注意事项

建议使用 PCB 布线长度小的 PCB 布局,以避免过大的电容负载并确保正确的单次触发发生。PCB

信号线走线长度应保持足够短,以使每次影射的往返延迟小于单次触发持续时间。通过确保任何一次

影射都能在驱动器处看到一个低阻抗,从而改善信号完整性。设计的单次触发周期保持在接近 30ns。

可以驱动的集总负载的最大电容也直接取决于单次持续时间。对于非常大的容性负载,单次触发可以

在信号被完全驱动到正轨之前超时。通过对动态参数 ICC、负载驱动能力和最大比特率之间的权衡,设

置单次触发的持续时间为最佳状态。从 MS4553S 的输出,可以看到 PCB 走线长度和连接器都会使电容

增加,因此建议考虑使用集总负载电容,以避免重新单次触发、总线竞争、输出信号震荡或其他不利

的系统级影响。

启用和关断

MS4553S 有一个 OE 输入端口。当 OE 为低电平时,使器件关断,所有 I/O 口在高阻状态。只要

VCCA 通电,OE 就会存在一个内部的下拉电流源。关断时间(tDIS)表示 OE 变为低电平和输出为高阻状态

之间的延迟。启用时间(tEN)表示必须在 OE 被提升为高电平后,用户才允许单次触发电路运行的时间。

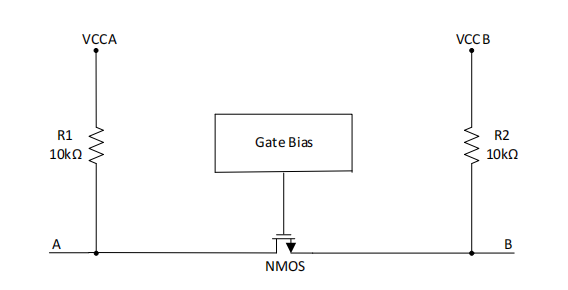

I/O 口的上拉和下拉电阻

对于 VCCA,每一个 A 端口都有一个 10kΩ 的内部上拉电阻;对于 VCCB,每一个 B 端口都有一个

10kΩ 的内部上拉电阻。如果需要一个更小的上拉电阻,必须在 I/O 口到 VCCA 或 VCCB 之间,添加一个

外部电阻。然而,加上一个阻值更小的上拉电阻将会影响 VOL电平。当 OE 为低电平时,MS4553S 内部

上拉电阻会被关断。

典型应用图

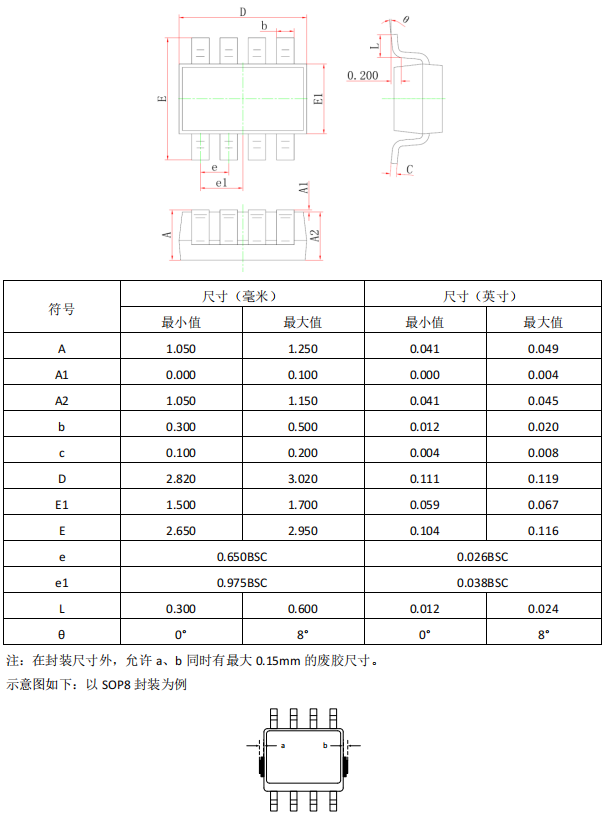

封装外形图

SOT23-8

——爱研究芯片的小王

审核编辑 黄宇

-

一款用于开漏模式和推拉模式的2bit双向电平转换器MS6212D2026-01-16 176

-

用于开漏和推拉应用的汽车4位双向电压电平转换器TXS0104E-Q1数据表2024-04-28 419

-

用于开漏模式和推拉模式的 4bit 双向电平转换器MS4554N/MS4554N12023-07-26 1104

-

用于开漏模式和推拉模式的 4bit 双向电平转换器----MS4554N/MS4554N12023-06-29 2024

-

MS6212D-用于开漏模式和推拉模式2bit双向电平转换器2023-04-25 880

-

8位双向多电压电平转换器;漏极开路;推拉-LSF01082023-02-20 524

-

4位双向多电压电平转换器;漏极开路;推拉-LSF02042023-02-17 678

-

2位双向多电压电平转换器;漏极开路;推拉-NCA93062023-02-15 561

-

2位双向多电压电平转换器;漏极开路;推拉-NCA9306_Q1002023-02-10 528

-

2位双向多电压电平转换器;漏极开路;推拉-LSF01022023-02-09 591

-

瑞盟MS4553 双向电平转换器—pin对pin兼容TXB01022022-12-07 628

-

pin对pin兼容TXB0102的双向电平转换器MS45532022-09-22 1181

-

MS6212D-用于开漏模式和推拉模式2bit双向电平转换器(颂扬恒科技-瑞盟一级代理)2022-02-21 666

-

国产双向电平转换器MS4553M,兼容PCA93062021-07-18 826

全部0条评论

快来发表一下你的评论吧 !