FPGA的引脚配置技巧 分配fpga管脚时该怎么选择

可编程逻辑

描述

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V LVTTL(default) )分别是什么意思,要怎么设置?

IO standard是根据你所要输入的电平来设置,Group是根据所分配的信号端口自动确定,而每个引脚的IO Bank本身已经确定!

另外,分配的引脚所属的IO Bank不同有关系吗?引脚的分配除了要考虑专用引脚和用户引脚的区别外,还要考虑什么因素?

一一回答,从简单到复杂。

首先说IO standard:这个是用于支持对应不同的电平标准。FPGA IO口的电压由IO bank上的VCC引入。一个bank上引入3.3V TTL电平,那么此时整个bank上输出3.3V的TTL电平。设置这个第一是为了和current strength一起计算功率。第二个是用于在IO口上加载正确的上拉/下拉电阻。只要你设置完成,Quartus会按照你的电平标准自动布线。

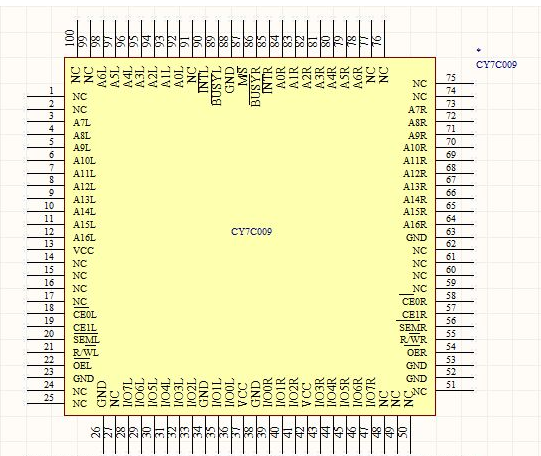

第二是IO Bank:你在quartus pin planner 的top view下右键然后点击 show IO banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。一种颜色下的IO口代表一组bank。你在吧管脚的location约束完成以后。IO Bank会自动填充完毕的。

第三是Group:Group就是你所输出的信号的名字啦。比如你有一组信号叫cnt。你对cnt的某一根赋值,那么。。这里的Group会自动填充为cnt 。

第四是Reserved:这个是对管脚内部的IO逻辑进行约束的,你在下面可以看到一些值。介绍几个吧。bidrectional:双向,tri-state:三态等等。这个约束的是FPGA在IO端的输入输出区域的逻辑。比如你选择tri-state。那么这个时候,在你IO口前部的IO区,quartus会自动给你生成一个三态门。

第五个是Vref Group:这个Group是bank内部的细分区域,因为一个bank可能多达60个脚。为了快速定位,你可以利用这个vref group来找到某个管脚。(这个是非修改属性)无法修改。

你的理解是正确的,另外,跨越IO bank的信号没有问题。只是注意跨bank的电平是否一致即可。对于跨IO bank的延迟对于FPGA而言没有多少延迟。

管脚分配呢,你可以看一下quartus里面pin planner内部那张 top view对于每个管脚的说明。大多数管脚是可以当做普通IO使用的。只是有些特殊要求的时候。只可以使用对应的IO,比如差分输入,高时钟输入等等。这个是要参照对应器件的IO 手册来决定的。而且对应的设计大多数的器件生产商都会给出参考设计。里面包括了IO的设计,pcb的设计以及内部程序端口的约束。所以具体问题具体分析。

-

浅谈如何克服FPGA I/O引脚分配挑战2024-07-22 7860

-

FPGA管脚该怎么设计?2019-09-18 2284

-

FPGA新手解惑—FPGA引脚配置技巧2019-06-17 4502

-

分配fpga管脚时该怎么选择?2019-04-03 4564

-

Quartus II中FPGA的管脚分配保存方法2018-07-03 5045

-

MIG IP核管脚分配问题2018-03-16 5487

-

FPGA管脚分配时需注意的一些事项2017-02-11 12603

-

例说FPGA连载33:PLL例化配置与LED之使用Tcl Console进行引脚分配2016-09-17 3220

-

图文解析如何分配FPGA管脚2015-01-06 4405

-

关于FPGA引脚分配的问题2013-01-06 8990

-

FPGA 管脚分配需要考虑的因素2012-08-11 5271

-

FPGA设计管脚分配2011-01-25 1548

全部0条评论

快来发表一下你的评论吧 !