关于高速接口技术简析

接口/总线/驱动

描述

1差分信号技术概况

高速差分信号有多种备选形式,这些差分技术有着相同的特点,但性能、功耗、应用场景等方面又变化多端。

差分技术

工业标准

最大数据率

VOD输出幅值

电源功耗

LVDS

TIA/EIA-644

3.125Gbps

±350mV 低

LVPECL

无

10+Gbps

±800mV

中到高

CML

无

10+Gbps

±800mV

中

M-LVDS

TIA/EIA-899

250Mbps

±550mV

低

B-LVDS

无

800Mbps

550mV

低

国际标准ANSI/TIA/EIA-644A和ANSI/TIA/EIA-899中定义了LVDS和M-LVDS技术。Current-Mode Logic电流模式逻辑和Low-Voltage Positive-Emitter-Coupled Logic低压正发射级耦合逻辑技术在业界应用广泛,由于暂缺对应的工业标准,不同厂商的实现形式和接口的差异较大,往往采用AC耦合的方式来解决门限差异和兼容性问题。

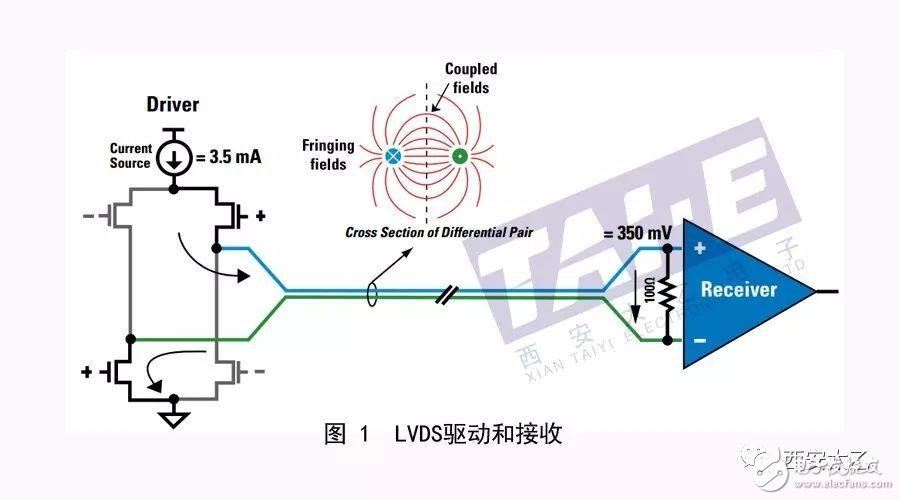

典型的LVDS驱动接收对如图1所示,驱动端使用3.5mA电流源。由于接收端输入阻抗高,绝大多数有效电流将流过100Ω端接电阻,在接收端输入处形成350mV压差。接收端阈值电压一般不超过100mV,且共模电压在0到2.4V之间都可以维持这样的激励,能够在驱动端和接收端提供很好的噪声裕量和共模漂移容忍度。当电流方向改变时,幅值不变、极性反转,由此产生了逻辑“1”和“0”。CML和LVPECL有着类似的结构,区别在于驱动电流强度和端接策略。

图2为差分信号简图。首先,电流源在不同的方向驱动逻辑“1”和“0”,始终保持打开的状态;相比于单端信号技术,可以消除晶体管频繁开关造成的开关噪声和EMI。其次,差分双线相互毗邻可提供重要的抗噪能力,两根单线吸收的交调或EMI噪声是一致的,接收端只对两个通道的差值响应,“共模”噪声会随之消除。此外,由于两条线承载的电流等幅反相,产生最小的EMI。

2LVDS低压差分信号技术

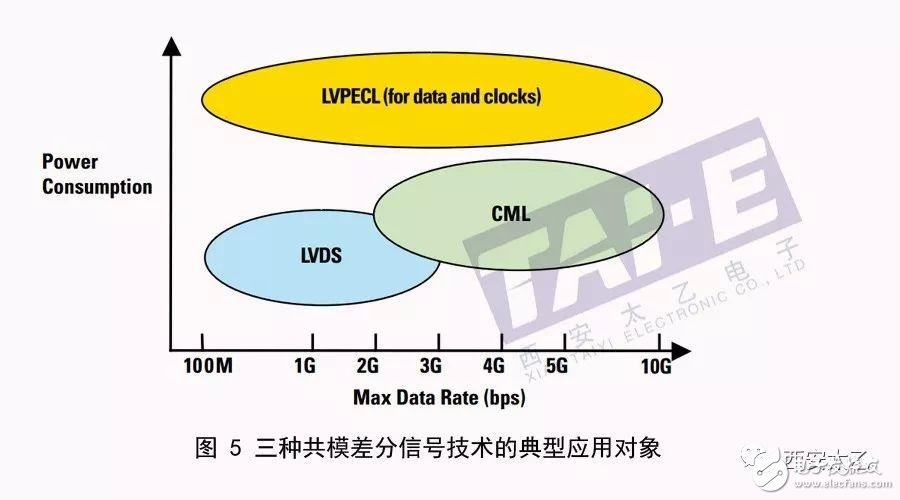

LVDS效率很高,输出幅值约350mV,在消耗较少能量的情况下,实现高达3.125Gbps数据速率;端接策略简单、低功耗和低噪声的性能使得LVDS技术在几十Mbps到3Gbps之间应用广泛。

为实现更高的数据速率,就需要使用CML或LVPECL。这两种技术通过非常快且陡的跳变沿和接近800mV的输出幅值,来提供超过10Gbps的数据速率,因此相对于LVDS会消耗更多的能量。

3CML电流模式逻辑技术

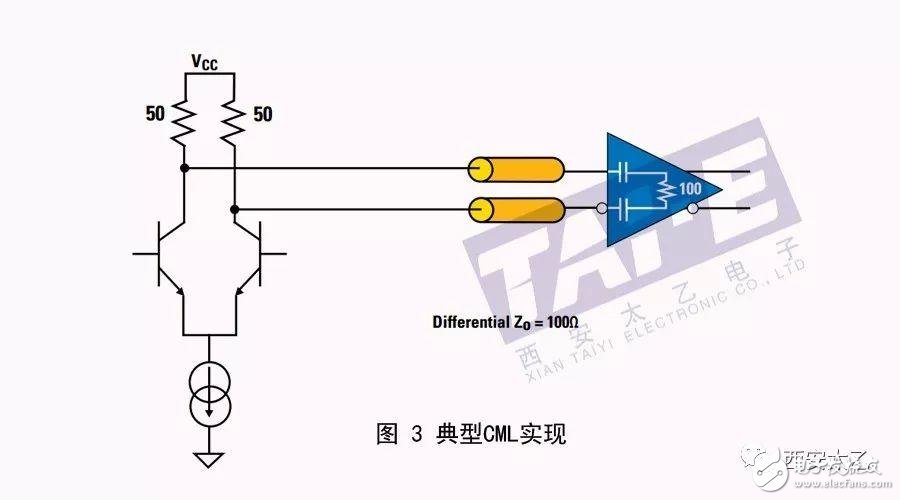

高速点对点形式的CML接口可提供超过10Gbps的数据速率。如图3所示,CML通常在驱动端和接收端均集成了端接网络,采用被动的50Ω上拉电阻连接到电源;通过AC耦合技术实现信号传输,需要传输DC平衡数据。

4LVPECL低压正发射极耦合逻辑技术

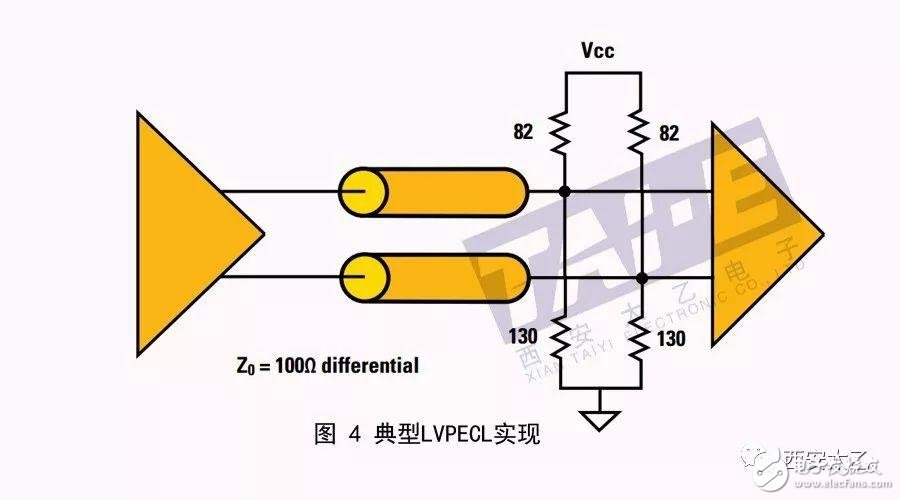

LVPECL和PECL都是20世纪60年代ECL技术的分支,ECL通常在地和-5.2V之间供电。由于需要阴轨,ECL难以与其他逻辑兼容,直到PECL作为阳轨技术引进。ECL、PECL、LVPECL都需要50Ω端接到轨端,低于多数阳轨2V。ECL驱动器为低阻抗开射极输出,约700到800mV,可产生非常快且平衡的跳变沿。LVPECL的优点在于陡峭且平衡的跳变沿、高驱动能力;缺点在于高功耗,有时需要独立的端接轨。

5选择合格的技术应用

在选择高速接口技术时,应该注意如下因素:

● 所需带宽

● 驱动电缆、背板或长线的能力

● 电源预算

● 网络拓扑

● 串行或并行数据传输方式

● 工业标准间的兼容性

● 信号条件的特殊需求

LVDS作为最常用的差分信号接口,其低功耗、弱EMI、强抗噪特性使得应用最为广泛。此外,LVDS的共模输入范围广,易于与其他差分信号技术交互操作。最新一代的LVDS工作在DC到3.125Gbps之间,器件可通过预加重和均衡化等手段使信号通过有损电缆和印制板走线。

速率大于3.125Gbps时一般使用CML信号,PCIe、SATA、HDMI等通讯标准使用与CML一致的规则来规定特定的信号细节。

介于2Gbps到3.125Gbps之间的速率,高速接口的选择取决于所需功能、性能、功耗等因素。对于相对短距的传输,CML有着最小的抖动而LVDS有着最低的电源功耗。对于长距传输,介质损耗占据主要因素地位,首当其冲要使数据速率和质量的传输条件最佳,LVDS和CML均可采用预加重、去加重、均衡化等处理技术。

- 相关推荐

- 热点推荐

- 接口技术

-

语音接口技术浅析2022-11-01 565

-

微机原理与接口技术知识总结2021-12-10 1274

-

微机接口技术实用教程2021-09-13 1914

-

浅析单片机原理及接口技术2021-09-10 1242

-

微机原理与接口技术2016-12-19 3777

-

单片机接口技术2013-06-13 2981

-

EPON技术简析2010-01-22 1140

-

WCDMA无线接口技术2009-09-18 6397

-

高速遥感卫星信号接口技术的研究与实现2009-08-14 543

-

微机接口技术课件2009-06-12 7926

全部0条评论

快来发表一下你的评论吧 !