FPGA基础知识及其工作原理与基本的功能块案例

描述

高端设计工具为少有甚是没有硬件设计技术的工程师和科学家提供现场可编程门阵列(FPGA)。无论你使用图形化设计程序,ANSI C语言还是VHDL语言,如此复杂的合成工艺会不禁让人去想FPGA真实的运作情况。在这个芯片中的程序在这些可设置硅片间到底是如何工作的。本文会使非数字化设计人员明白FPGA(现场可编程门阵列)的基础知识及其工作原理。此信息在使用高端设计工具时同样十分有用,希望可以为理解这一特别技术提供一些线索。

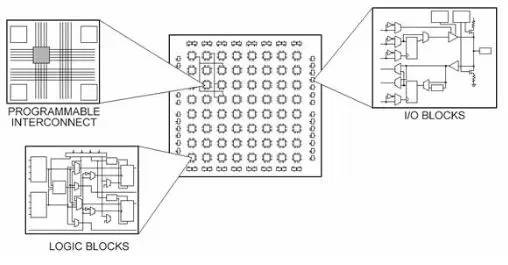

1. FPGA-现场可编程门阵列每一块FPGA芯片都是由有限多个带有可编程连接的预定义源组成来实现一种可重构数字电路。

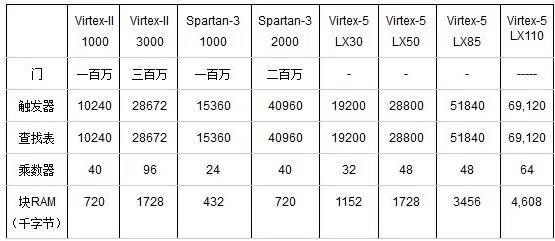

图1.FPGA不同构成FPGA芯片说明书中,包含了可编程逻辑模块的数量、固定功能逻辑模块(如乘法器)的数目及存储器资源(如嵌入式RAM)的大小。FPGA芯片中还有很多其它的部分,但是以上指标通常是为特定应用选择和比较FPGA时,最重要的参考指标。在最底层,可配置逻辑模块(如片或逻辑单元)有着两种最基本的部件:触发器和查找表(LUT)。这很重要,因为各种FPGA家族之所以各不相同,就是因为触发器和查找表组合的方式不同。例如,Virtex-II 系列的FPGA ,它的片具有两个查找表和两个触发器,而Virtex-5 FPGA的片具有4个查找表和4个触发器。查找表本身的结构也可能各不相同(4输入或6输入)。关于查找表工作原理的更多信息将在后面的章节中给出。表1中列出了在NI LabVIEW FPGA硬件目标中使用的FPGA的指标。逻辑门的数量是一种将FPGA芯片与ASIC技术进行比较的传统方法,但是它并不能真实地表述FPGA内部的独立单元的数量。这就是Xilinx公司没有在新型Virtex-5系列中指定逻辑门数量的原因之一。

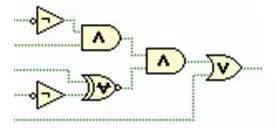

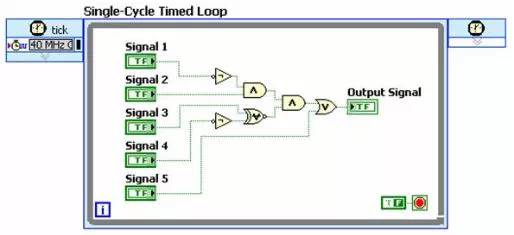

表1.不同系列FPGA源规格为了更好地理解这些规格的意义,将编码考虑为合成的数字电路模式。对任何一段合成代码,或图形化或文本形式,都有相应的电路图反映逻辑组件该如何连线。通过一段简单布尔逻辑电路了解下相应的示意图。图2表示的是传递5个布尔信号并且可图形化计算所得的二进制值的功能组。

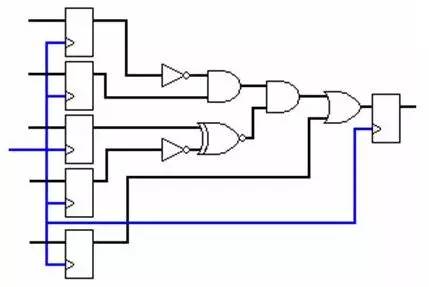

图2.载入5个信号的简单布尔逻辑在通常情况下(LabVIEW SCTL—单周期定时环路外),图2所示相应电路图同图3所示相近。

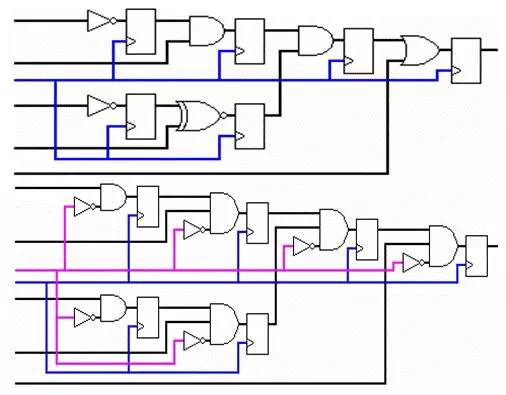

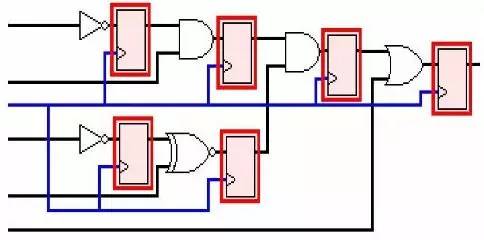

图3.为图2中布尔逻辑的相应电路图虽然很难明白,但是实际上这里创建了两个并行分支的电路。最上面的5条黑线被反馈到第一个分支,它在每个布尔操作间添加了触发器。最下面的5条黑线构成了第二个逻辑链。其中一支路在每步操作之间增加了同步寄存器,另一条逻辑链是确保执行数据流的。本电路图正常工作时总共需要12个触发器和12个查找表。上端分支和每个元件将在以后章节分析。2. 触发器

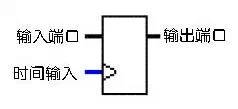

图4.触发器符号触发器是二进制移位寄存器,用于同步逻辑以及保存时钟(脉冲)周期内的逻辑状态。在每个时间(脉冲)边沿,触发器在输入时锁定1(真)或0(假)值并且保存此值直到下次时钟(脉冲)边沿。在正常情况下,LabVIEW FPGA在每次操作之间都设置一个触发器,以保证有足够的时间来执行每步操作。对此律的例外只发生在SCTL结构中写代码的情况。在这个特殊的环路结构中,触发器只放置在闭环迭代的始末段,并且由编程者考虑定时因素来决定如何放置。对SCTL内代码如何同步的更多内容将在以后章节中讨论。图5表示的是图3的上端分支,触发器由红色高亮表示。

图5.绘制由红色高亮表示出触发器的电路图3. 查找表

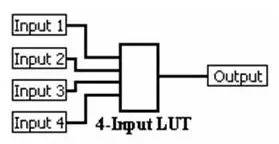

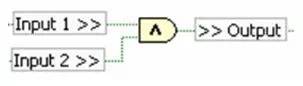

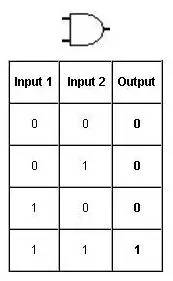

图6.双四输入查找表图6所示示意图中的其他逻辑电路通过使用少量查找表形式的随机存取存储器实现。我们可以简单地假定FPGA中系统门的数量可参考与非门(NAND)以及或非门(NOR)的数量,但实际上,所有的组合逻辑(与门、或门、与非门、异或门等)都是通过查找表存储器中的真值表来实现。真值表是输出对应于每个输入值组合的预定义表(现在卡诺图的重要性在你的头脑中可能会慢慢淡化)。以下是对数字逻辑电路课程的快速回顾:比如,图7是布尔逻辑与门操作过程。这是对数字逻辑课程的快速回顾:例如,图7中显示了布尔型AND操作。

图7.布尔型AND操作

表2.布尔与门操作的真值表

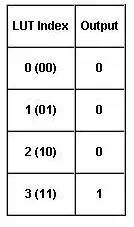

你可以认为输入值是所有输出值的数字索引,如表3所示。

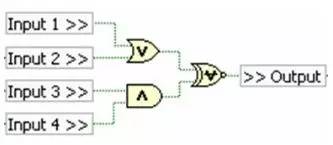

表3.布尔与门擦操作的真值查找表实现Virtex-II和Spartan-3系列FPGA芯片有着4输入查找表来实现真正的4输入信号的16种组合。图8就是一个四输入电路实现的例子。

图8.输入布尔逻辑的四信号电路

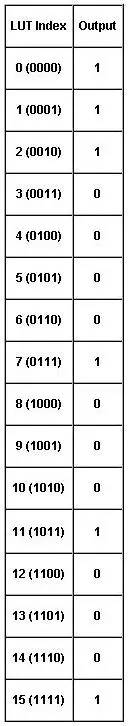

表4所示为使用双四输入查找表实现的相应的真值表。

表4.图8中所示相应真值表

Virtex-5系列的FPGA使用双六输入查找表,可以通过6个不同输入信号的64种组合来实现真值表。因为触发器之间的组合逻辑十分复杂,所以在LabVIEW FPGA中使用SCTL也越来越重要。下一节将讲述SCTL如何优化利用LabVIEW中的FPGA源。4. SCTL上几节中使用的代码例子假定代码是设置在SCTL外部,并为保证执行同步数据量也同步了附加电路。SCTL是LabVIEW FPGA中一个特殊结构,生成一个更为优化的电路图,以期望达到在一个时钟(脉冲)周期内执行完所有逻辑电路分支。例如,若设置SCTL在40MHZ运行,则所有逻辑电路分支将在25ns内执行完毕。如果在SCTL中设置前例中同样的布尔逻辑电路(如图9所示),则生成如图10所示的相应电路示意图。

图9.附有STCL的简单布尔逻辑

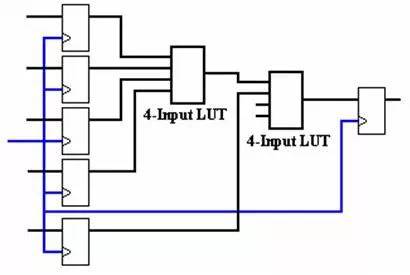

图10.图9所示布尔逻辑相应的电路图很明显,这种实现方法简单多了。在Virtex-II或Spartan-3系列FPGA中,触发器间的逻辑需要至少2个4输入查找表,如图11所示。

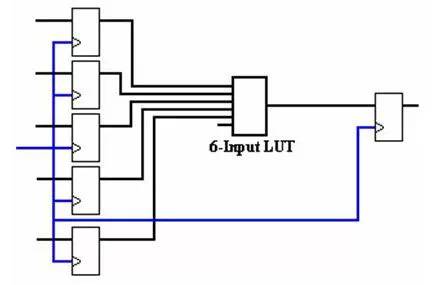

图11.图10中电路图的双四输入查找表实现由于Virtex-5系列FPGA有着6输入的查找表,用户可以在一个查找表中实现相同数量的逻辑,如图12所示。

本例中使用的SCTL(如图9所示)设置在40MHZ下运行,这意味着在任意触发器之间逻辑电路必须在25ns内完成执行。电子在电路中传播的速度决定了代码执行的最大速度。关键路线是有最长传播延迟的逻辑电路分支,它决定了该部分电路中理论最大时钟速率。Virtex-5 FPGA上的双六输入查找表不仅减少实现给定逻辑电路所需要的查找表总数,而且减少电子通过逻辑电路的传播延迟(时间)。Virtex-5系列FPGA中的6输入查找表不仅可以减少实现特定逻辑而需要的查找表的数量,而且可以降低逻辑中电流的传输延时。这意味着,您可简单地通过选择一个基于Virtex-5的硬件指标设置相同的SCTL,追求更快的时间速度。5. 乘数器和DSP片

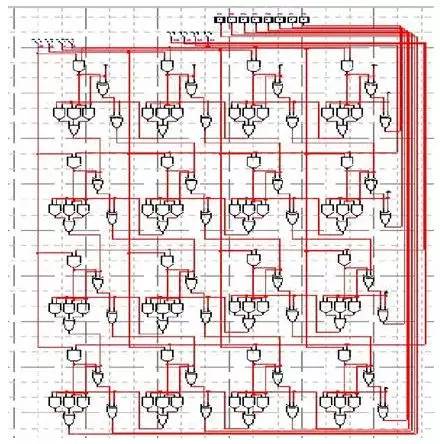

图13.乘数器功能看起来简单的两数相乘运算在数字电路中实现起来是十分复杂的,也是极为消耗资源的。为提供相关参考,图14所示是一种使用组合逻辑电路实现4×4字节乘数器的示意图。

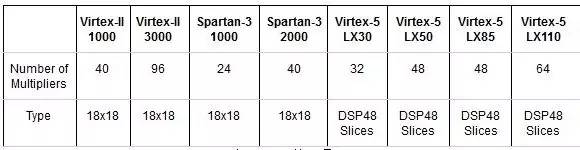

图14.两个4字节输入相乘的电路图试想两个32字节的数字相乘要通过2000多步操作才能得到结果。因此,FPGA预设了乘数器电路,在数学和信号处理应用中保存对查找表和触发器使用。Virtex-II和Spartan-3 FPGA拥有18×18bit乘法器,所以两个32字节数字相乘的运算需要三个乘法器来实现。许多信号处理算法都包括连乘运算结果的功能,因此Virtex-5等高性能FPGA都预设被称为DSP片的乘数器累加电路.这些预设处理组件,也被称为DSP48片,包括25×18bit乘数器以及加法器电路,尽管您可单独使用乘数器功能。表5所示为不同FPGA系列DSP决策。

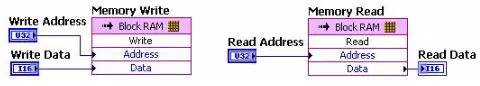

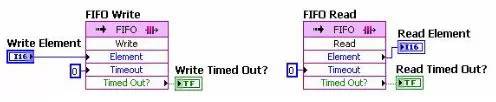

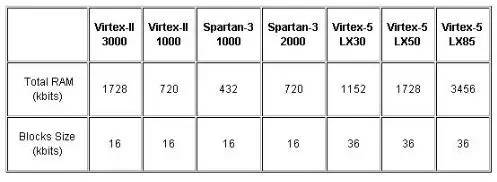

表5.不同FPGA的DSP源6. 块随机存取存储器(RAM)选择FPGA时,记忆源是另一个需要考虑的关键因素。嵌入FPGA芯片中的用户自定义随机存取存储器(RAM),对储存数据设置或平行环路之间传送数值很有帮助。基于FPGA系列,您可在16或36kb组件中设置板载RAM,或者使用触发器以数组来执行数据设置;然而,对于FPGA逻辑源来说,大型数组很快就变得十分“奢侈”。由100个32字节元素数组可消耗Virtex-II 1000 FPGA中超过30%的触发器,或者占用少于1%的嵌入式块RAM。DSP算法通常需要追踪整个数据块或是复杂等式的系数,而在没有板载存储器情况下,许多处理功能在FPGA芯片的硬件逻辑电路中都不适用。图16所示为使用块RAM读写存储器的图形化功能。

图15.用于读写存储器的块RAM函数同样,你也可以使用内存块,将一段完整周期存储为数值和索引的顺序表,为板载信号发生器存储周期性波形数据。输出信号的最终频率由检索数值的速度决定,这样您就可用此方法动态改变输出频率,而不需要输入波形中的急剧变化。

图17.用于先进先出缓冲器的块RAM功能FPGA固有的并行执行要求逻辑电路独立元件可在不用时间脉冲下驱动。在不同运行速度下的逻辑电路之间传递数据是很棘手的。使用先进先出(FIFO)缓冲器时,板载存储器可用来是传输更加平稳。如图16所示,用户可以将FIFO缓冲器配置成不同大小以确保数据在FPGA芯片的非同步部件间不会丢失。表6所示为嵌入不同FPGA系列的用户可设置快RAM。

表6.不同FPGA的记忆源7. 总结随着高端技术的发展以及新概念的深入概括,FPGA技术地采用将不断增加。然而探究FPGA其中奥秘,感叹这硅片中在方框图间汇编出的变化,也是十分重要的。在发展阶段,如果您懂得如何利用和优化资源,比较和选择触发器、查找表、乘数器和块RAM等硬件指标是十分有帮助的。 这些基本的功能块并不是包含所有资源的完整清单,而且这篇白皮书并没有包含对所有FPGA部件的讨论。

- 相关推荐

- 热点推荐

- FPGA

-

FPGA的基础知识及其工作原理2023-01-09 2184

-

什么是FB功能块?为什么要使用FB功能块?如何制作一个FB功能块?2023-11-09 6643

-

FPGA的基础知识点及工作原理是什么2021-04-30 1414

-

浅析TwinCAT TC3_Controller_Toolbox功能块2021-09-01 2552

-

如何去使用TwinCAT的功能块2021-10-08 2792

-

基于EPA的PID功能块的设计及实现2009-09-26 780

-

腾控MODBUS主站功能块通迅详解2017-10-11 1260

-

FPGA(现场可编程门阵列)的基础知识及其工作原理2017-11-18 18375

-

西门子PLC系统功能块和系统功能2020-12-23 12811

-

CPM功能块使用入门2021-05-09 784

-

调用功能块(FB或SFB)2022-04-20 5167

-

简单位置控制功能块讲解2023-03-08 2399

-

步进电机基础知识:类型、用途和工作原理2023-08-02 2379

-

Freelance函数和功能块使用指南 V9.12023-08-09 461

-

FPGA基础知识及设计和执行FPGA应用所需的工具2024-11-11 2431

全部0条评论

快来发表一下你的评论吧 !