224G 高速互联对 PCB 及覆铜板需求及激光锡球植球机的助力(上)

电子说

描述

一、224G 高速互联技术概述和背景

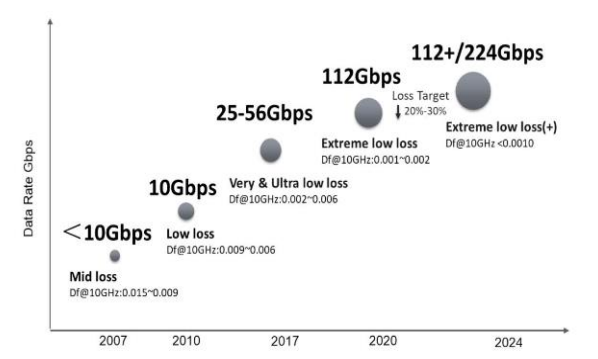

带宽需求连年暴涨,单一通道带宽 224Gbps 技术将加速超大规模云数据中心平台向 800G演进,成为数据中心连接、企业和运营商市场的一项重要技术。

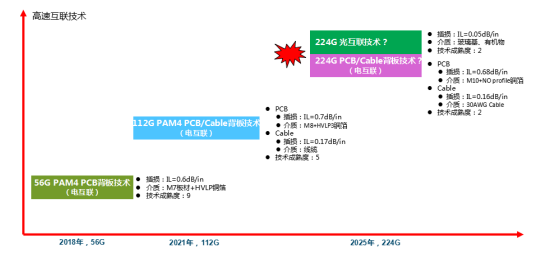

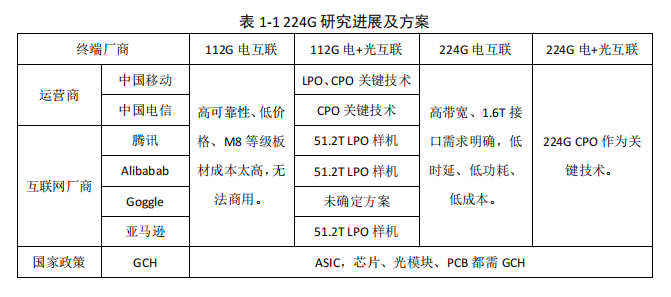

112G 已批量商用,224G 高速互联进入预研阶段,各芯片厂商 Marvel、博通、英伟达等已启动 224G 高速互联技术研究。研究方案包含光电互联以及 PCB/Cable 技术等。见下图 1-1所示。

在 28GHz 时,12dB 的板级损耗导致 Megtron6 材料有大约为 5 英寸的覆盖范围,而Megtron7 材料的范围约为 10 英寸。这意味着在大型交换 SOC 和光学模块之间驱动近一英尺的电路板。通过使用 PAM4 调制将符号速率扩展到 200Gbps,同样的 30 毫米封装在 112GBd符号速率下将消耗大约 12dB 的损耗。这为电路板留下了大约三分之一的损耗预算。假设将相同的均衡水平应用于 224G“芯片到模块”,将导致交换和光模块之间可用的 Megtron6 材料不到1英寸。更贵的Megtron7材料在两个设备之间实现1.2英寸的距离。显然,从在112Gbps时可以容忍一英尺的间隔,到 224Gbps 时仅为一英寸。使用光学器件构建系统显然会因这些类型的路由限制而变得笨拙。这是业界成功将设计扩展到 224Gbps 必须克服的挑战。

支持 800GbE 模块的 112Gbps 已逐渐成熟,224Gbps PAM4 已处于开发阶段,预计将速度再次提高一倍,最终支持每个模块高达 1.6Tbps 或 3.2Tbps。图 1-2 高速 224G 高速链接设计。224G 研究进展及方案组合见表 1-1。

二、224G 高速互联技术特点

2.1、224G 高速互联设计

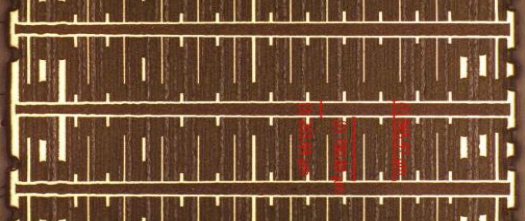

对于 224G 设计,激光孔的高度会更高,因为会使用比 112G 设计更厚的电介质来降低走线的 IL/mm,显然 224G 的阻抗波动和 IL&RL 会差很多。

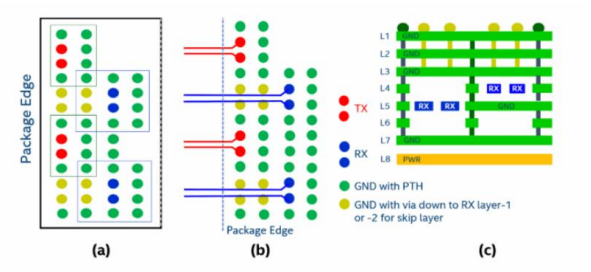

通过并联增加更多的激光过孔以增加信号路径的截面积来降低寄生电感,同时球垫/焊球与返回平面之间的寄生电容不增加。采用同轴 GSGSG 设计优化信号返回路径。通过多次芯板(MLC)叠层来减薄基板 core 厚度,从而缩短 PTH 的高度来进一步减小寄生电感。

PCB BGA 区域与封装 die bump 区域的功能相似,球间距是 FCBGA 芯片的关键参数,大型 FCBGA 芯片的传统球间距为 1.0mm,可以满足 SIPI 和 PCBA 的可靠性要求。但对于 224Gbps信号,需要使用 0.8mm 或更小的球距来增加信道带宽。但是,基于目前大型 FCBGA 芯片的技术,0.8mm 或更小的球距不利于 PCBA 的可靠性,PCBA 厂商的焊接经验也较少,这意味着球间距越小,PCBA 风险越高。

通过增加信号孔与回流孔的耦合来改善带宽。带宽提高到了 84Ghz 左右,回损也有明显的降低。

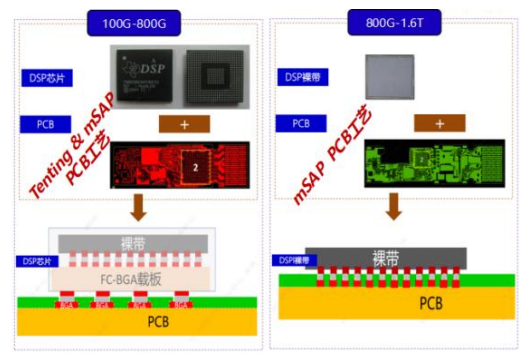

2.2、224G 芯片功耗及组装

224G 芯片功耗增长,意味着供电电源的电流安培数增长,对 PCB 厚铜、PCB 导热技术提出更高挑战。

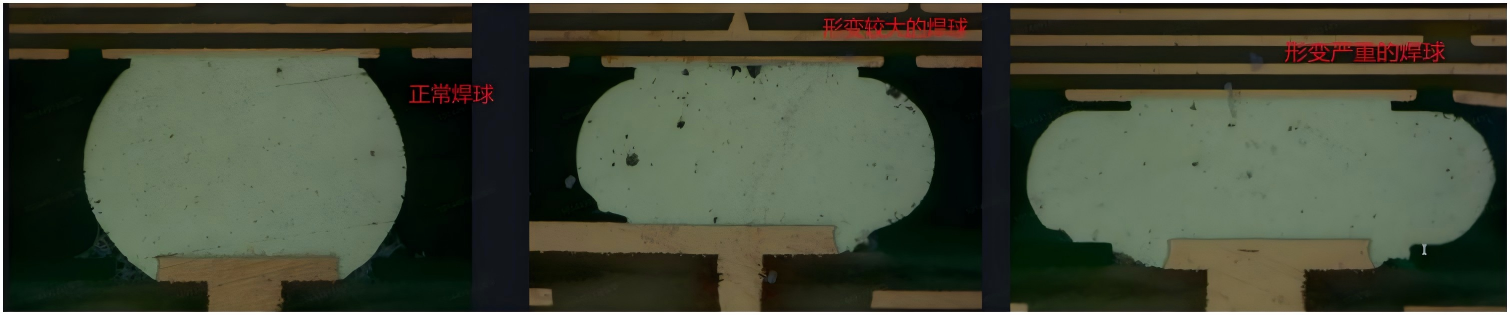

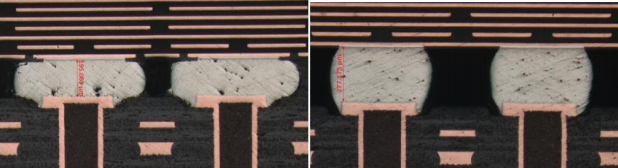

随着交换芯片 Serdes 从 56Gbps 演变到 224Gbps,传输速率的不断提升对芯片的封装、组装也提出了相应要求,最直观的要求就是提高速率、降低损耗。从业界研究看,焊球形状(高度、直径与外形轮廓等)与一致性会对 224G 及以上高速 SI 阻抗有显著影响,普通鼓型焊点并非最优,圆柱形焊点反而可以获得更好的效果。针对不同的焊球形状和对应尺寸进行建模仿真,结果如下图 2-3 所示,不同的焊球形状阻抗从正常的 83 Ohm 降到 76 Ohm,极端恶化情况下会跌到 66 Ohm。

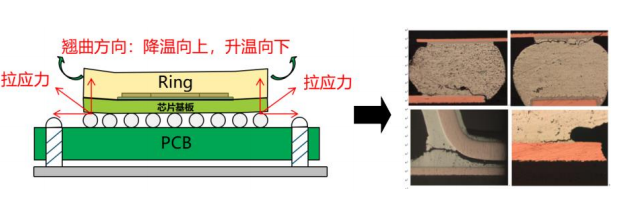

BGA 的焊球形状最好是圆柱形,而目前 BGA 芯片尺寸越来越大的情况下 Warpage 也越来越大,难以保证焊球高度及形貌,如图所示压扁的焊球形貌会使高速性能劣化。目前 224G技术预研发现阻抗劣化已成为最大的瓶颈之一,因此有必要展开相关技术研究以攻克“焊形状影响高速 Serdes 阻抗”这一技术难题。解决方案包括叠层优化降低 PCB 的 CTE,开发 Low CTE 板材减少 PCB 翘曲等。

2.3、焊点可靠性

大尺寸BGA芯片焊点可靠性一直是产品痛点,且随着尺寸增大焊点可靠性呈下降趋势,目前大尺寸芯片存在焊点可靠性风险。

影响焊点长期可靠性的最重要因素是,焊点在温度变化过程中的失效。在不断的升降温过程中,由于各种材料的 CTE 不同(常规高速板材的 PCB 的 X/Y CTE 约 19-23ppm/℃,SSP4芯片的 CTE 约 12.8-14.7ppm/℃),焊点反复的应力应变将导致焊点中裂纹的萌生和扩展最终导致焊点的失效。因此需要接近芯片 CTE 的 Low CTE 高速板材。224G 需要的 PCB 板材 CTE 值为,CTE(X,Y)≦13ppm/℃。

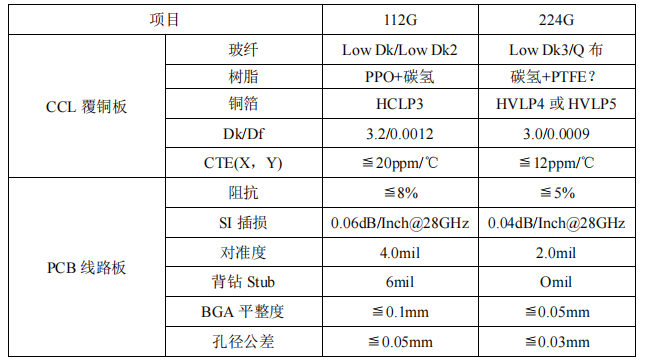

三、224G 互联技术对 PCB 及覆铜板需求

3.1、224G 高速互联传输目标及要求

224G 高速互联旨在实现超高速的数据传输,以满足当下及未来海量数据在各类应用场景中的快速交互需求,如在超大规模云数据中心平台中,助力其向 800G 乃至更高传输容量演进,为数据中心连接、企业和运营商市场提供高效稳定的数据传输通道。其对信号完整性、传输损耗、带宽等方面都有着极为严苛的要求,例如要求极低的插入损耗、良好的回波损耗控制以及足够宽的有效带宽,以此保障高速信号能够在 PCB 及整个链路中稳定、准确地传输,避免信号失真、衰减等问题影响数据传输质量。

224G 将在 112G 基础上线路损耗下降 30%,并要求 PCB 具有良好可加工性。

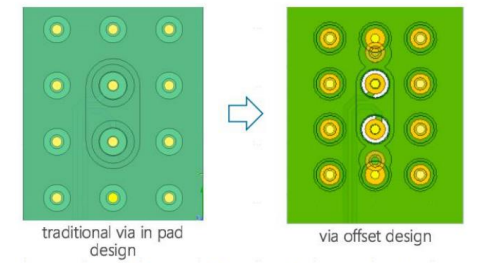

3.2、PCB 布局更密,孔径更小

要满足 PCB 扇出插损和串扰等指标,224G 产品 PCB 采用极限密集隔离孔(孔壁间距 0.20mm)互联工艺设计,最小孔径 0.15mm,布局有 0.4QFN、0.5BGA 等小器件。这样的设计布局是为了在有限的 PCB 空间内尽可能增加布线密度,缩短信号传输路径,减少信号传输延迟以及降低信号间的相互干扰。更小的孔径和更紧密的布局有助于优化 PCB 的电气性能,使其能够适配 224G 高速互联所要求的高频高速信号传输特性,但同时也对 PCB 的制造工艺和加工精度提出了前所未有的挑战,需要先进的设备和精湛的技术来确保每一个孔的加工精度以及各器件布局的准确性。

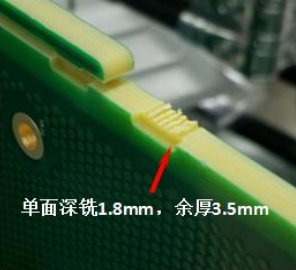

3.3、PCB 尺寸更大,纵横比更高,涨缩要更小

PCB 尺寸预计超过 900mm,PCB 厚度达到 6.0mm,PCB 纵横比超过 30:1,直径最小 0.15mm(如图 3-2 所示)。随着高速互联技术向 224G 迈进,更大尺寸的 PCB 能够承载更多的电子元件和复杂的电路设计,以满足日益增长的功能集成需求。

然而,大尺寸与高纵横比的 PCB 在制造过程中极易出现涨缩问题,这会严重影响各层线路之间的对准精度以及孔与线路的连接准确性,进而破坏信号传输的完整性。因此,必须严格控制 PCB 在加工及后续使用过程中的涨缩情况,这需要从 PCB 原材料的选择、制造工艺的优化以及生产环境的精准控制等多方面入手,确保 PCB 的尺寸稳定性达到 224G 高速互联技术的高标准要求。

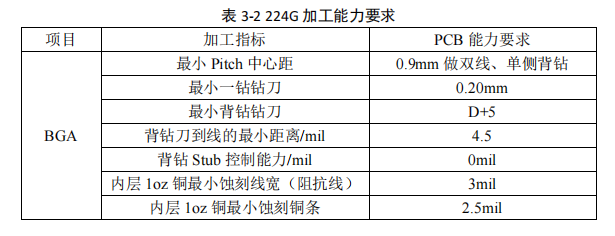

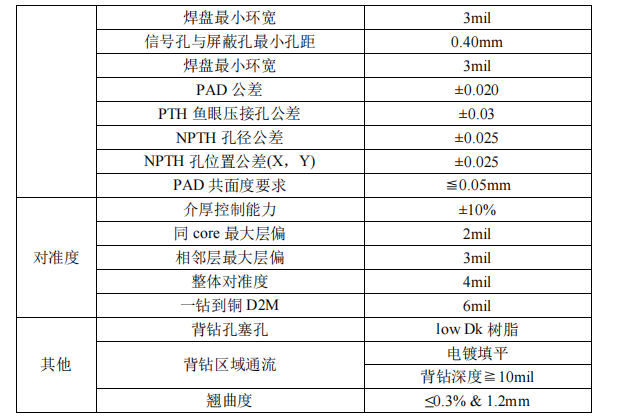

3.4、PCB 板厂 224G 加工能力

从降低插入损耗、损耗公差、背钻 STUB、对位层偏、阻抗公差控制、最小线宽/线距、最大板厚、最大板尺寸、钻孔厚径比、背钻直径、新型棕化药水引入、低损油墨、特殊工艺等各方面满足 224G Serders 单板设计需求,并保证良率(具体见表 3-2)。PCB 板厂需要全面升级其加工能力,在各个工艺环节都要达到更高的精度和稳定性。例如,在阻抗公差控制方面,要确保阻抗值在极小的允许误差范围内波动,以保障高速信号传输的稳定性;对于最小线宽/线距的把控,需借助高精度的制造设备和精细的工艺操作,实现极窄线宽和紧密线距的加工,满足高密度布线要求。新型棕化药水和低损油墨的引入,则有助于提升 PCB 的表面性能和信号传输质量,降低信号在 PCB 表面传输时的损耗。总之,PCB 板厂的 224G 加工能力是保障 224G 高速互联技术得以落地应用的关键环节,需要不断地技术创新和工艺优化来满足日益增长的高性能 PCB 制造需求。

(未完接下篇)

审核编辑 黄宇

-

如何利用BGA芯片激光锡球进行植锡2020-12-21 9344

-

激光锡球焊接原理及上锡工艺介绍2022-10-20 6500

-

激光锡球喷射焊接机的工艺介绍2023-11-03 2443

-

激光锡球焊接机植球工艺在半导体行业的崛起2024-10-24 2137

-

224G 高速互联对 PCB 及覆铜板需求及激光锡球植球机的助力(下)2024-12-03 1417

-

深度解析激光锡焊中铅与无铅锡球的差异及大研智造解决方案2025-03-27 2586

-

紫宸激光锡球焊锡机:点亮芯片0.07mm激光植球新征程2025-11-19 1096

全部0条评论

快来发表一下你的评论吧 !