不太了解FPGA的功能管脚?干货,值得收藏

可编程逻辑

描述

FPGA的管脚主要包括:用户I/O(User I/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应FPGA的芯片手册。

下面以ALTEra公司的Cyclone系列FPGA为例,介绍FPGA的各种功能管脚。

(1)用户I/O。

I/Onum(LVDSnumn):可用作输入或输出,或者双向口,同时可作为LVDS差分对的负端。其中num表示管脚序号。

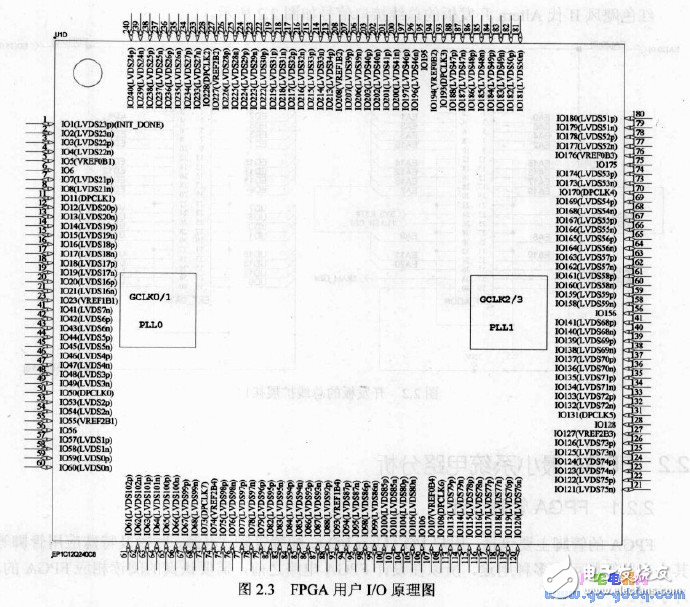

一般在绘制FPGA原理图时,将同一种功能和用途的管脚放在一个框图中,如图2.3所示是用户I/O的原理图。

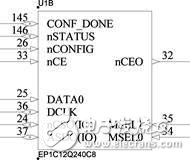

(2)配置管脚。

MSEL[1..0]:用于选择配置模式。FPGA有多种配置模式,比如主动、被动、快速、正常、串行、并行等,可以此管脚进行选择。

DATA0:FPGA串行数据输入,连接至配置器件的串行数据输出管脚。

DCLK:FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O):FPGA片选信号输出,连接至配置器件的nCS管脚。

ASDO(I/O):FPGA串行数据输出,连接至配置器件的ASDI管脚。

nCEO:下载链器件使能输出。在一条下载链(Chain)中,当第一个器件配置完成后,此信号将使能下一个器件开始进行配置。下载链的最后一个器件的nCEO应悬空。

图2.3 FPGA用户I/O原理图

nCE:下载链器件使能输入,连接至上一个器件的nCEO。下载链第一个器件的nCE接地。

nCONFIG:用户模式配置起始信号。

nSTATUS:配置状态信号。

CONF_DONE:配置结束信号。

如图2.4所示是FPGA配置管脚原理图。

图2.4 FPGA配置管脚原理图

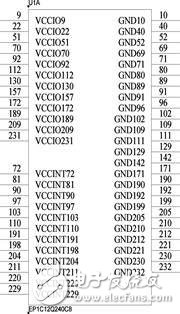

(3)电源管脚。

VCCINT:内核电压。通常与FPGA芯片所采用的工艺有关,例如130nm工艺为1.5V,90nm工艺为1.2V。

VCCIO:端口电压。一般为3.3V,还可以支持选择多种电压,如5V、1.8V、1.5V等。

VREF:参考电压。

GND:信号地。

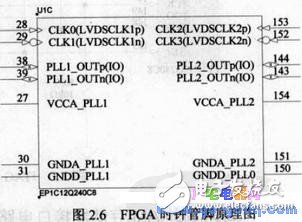

(4)时钟管脚。

VCC_PLL:锁相环管脚电压,直接连VCCIO。

VCCA_PLL:锁相环模拟电压,一般通过滤波器接到VCCINT上。

GNDA_PLL:锁相环模拟地。

GNDD_PLL:锁相环数字地。

CLKnum(LVDSCLKnump):锁相环时钟输入。支持LVDS时钟输入,p接正端,num表示PLL序号。

CLKnum(LVDSCLKnumn):锁相环时钟输入。支持LVDS时钟输入,n接负端,num表示PLL序号。

PLLnum_OUTp(I/O):锁相环时钟输出。支持LVDS时钟输入,p接正端,num表示PLL序号。

PLLnum_OUTn(I/O):锁相环时钟输出。支持LVDS时钟输入,n接负端,num表示PLL序号。

如图2.6所示是FPGA时钟管脚原理图。

图2.5 FPGA电源管脚原理图 图2.6 FPGA时钟管脚原理图

另外,FPGA的管脚中,有一些是全局时钟,这些管脚在FPGA中已经做好了时钟树。使用这些管脚作为关键时钟或信号的布线可以获得最佳性能。

(5)特殊管脚。

VCCPD:用于选择驱动电压。

VCCSEL:用于控制配置管脚和锁相环相关的输入缓冲电压。

PORSEL:上电复位选项。

NIOPULLUP:用于控制配置时所使用的用户I/O的内部上拉电阻是否工作。

TEMPDIODEn/p:用于关联温度敏感二极管。

-

pcb布线经验 (值得收藏)2009-05-12 4142

-

ARM经典300问,值得下载收藏2011-08-26 6550

-

值得工程师收藏的74系列资料大全2011-11-27 5676

-

值得收藏的电子技术网站最新汇总表!2012-11-20 3207

-

VCO设计相关资料值得收藏2017-03-24 3328

-

FPGA干货合集,菜鸟起飞必收藏!2020-05-11 4571

-

100条FPGA经验2015-11-11 649

-

一文介绍蓝牙透传模块AT指令集,绝对干货值得收藏!2018-01-04 2275

-

连接电路图的技巧,值得收藏2018-11-16 22085

-

如何学习好传感器知识,行业干货值得收藏2018-11-21 9622

-

【CC2530授课笔记】课程列表汇总 【超级干货】【建议收藏】2021-11-29 670

-

汇总常见单片机原厂代码仓库,值得收藏2021-12-03 793

-

142道linux面试题,值得收藏2022-06-16 628

-

「实用干货」7条实用的PCB布线规则,可收藏2023-02-01 1835

-

【干货】推荐收藏!电力电子FPGA实时仿真技术浅析2022-06-14 1664

全部0条评论

快来发表一下你的评论吧 !