选择PLL频率合成器时,你必须考虑的键性能参数解说

接口/时钟/PLL

49人已加入

描述

利用频率合成器,你可以产生单一参考频率的各种不同倍数的输出频率。其主要应用是为RF信号 的上变频和下变频产生本振(LO)信号。

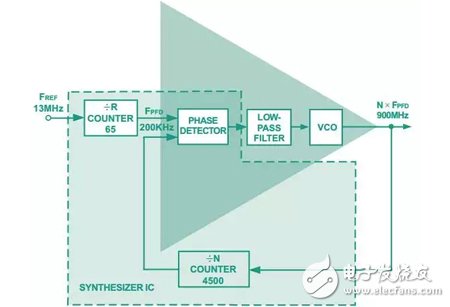

频率合成器在锁相环(PLL)中工作,其中鉴频鉴相器(PFD)将反馈频率与基准频率的某一分频形式相比较(如下图)。PFD的输出电流脉冲经过滤波和积分,产生一个电压。此电压驱动一个外部电压控制振荡器(VCO)提高或降低输出频率,从而驱动PFD的平均输出接近零。

锁相坏(PLL)框图

那么,选择PLL频率合成器时有哪些关键性能参数需要考虑呢?

1、相位噪声

对于给定功率水平的载波频率,频率合成器的相位噪声为载波功率与规定频率偏移(对于频率合成器通常为1 kHz)处1-Hz带宽上的功率之比。带内(或近载波)相位噪声主要取决于频率合成器,单位为dBc/Hz;VCO噪声贡献在闭环中被高通滤波滤除。

2、参考杂散

是内部计数器和以PFD频率工作的电荷泵所产生的在离散偏移频率上出现的频率成分。电荷泵产生的不匹配高低电流、电荷泵泄漏以及电源去祸不充分均会增加这种杂散。杂散音会混合在所需信号之上,降低接收机的灵敏度。

3、锁定时间

PLL的锁定时间是指它从一个指定频率跳跃到给定频率公差内的另一个指定频率所需的时间。跳跃大小一般由PLL在所分配的频带内工作时必须完成的最大跳跃决定。GSM-900的步进大小为45 MHz,GSM-1800的步进大小为95 MHz。要求的频率公差分别为90 Hz和180 HzPLL必须在不到1.5个时隙内完成所需的频率步进,每个时隙为577μs。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

-

关于相位锁定环(PLL)频率合成器的设计和分析2023-10-26 3008

-

pll频率合成器工作原理与pll频率合成器的原理图解释2023-02-24 11307

-

UG-161:PLL频率合成器评估板2021-03-20 899

-

PLL频率合成器应该如何选择2020-10-12 1018

-

什么是PLL频率合成器?2019-09-17 5255

-

如何利用FPGA设计PLL频率合成器?2019-07-30 4438

-

详解频率合成器高性能架构的实现2019-07-08 2439

-

MAX2902与外部频率合成器结合使用为频率规划和信道设置提供了最大灵活性2019-06-26 1686

-

基于FPGA与PLL频率合成技术设计的整数/半整数频率合成器2019-01-07 4080

-

这些关键性能参数,让你正确选择PLL频率合成器2018-05-29 6207

-

DDS-PLL组合跳频频率合成器2016-07-20 1060

-

PLL频率合成器的噪声基底测量2010-04-07 686

-

DDS PLL短波频率合成器设计2009-09-07 505

-

采用PLL的频率合成器电路图2009-07-20 1341

全部0条评论

快来发表一下你的评论吧 !