CPLD的优势 FPGA的产生

可编程逻辑

1397人已加入

描述

CPLD相对于老的PLD器件的最大进步在于它能够在单个器件中容纳大量的逻辑。理论上,可以不断在CPLD中加入LAB,继续增加逻辑数量。但是,这样做需要有额外的PI布线,实现所有这些LAB的连接,其连接数量会呈指数增长,直到芯片管芯的连线数量超过逻辑数量,这限制了容量的扩展。

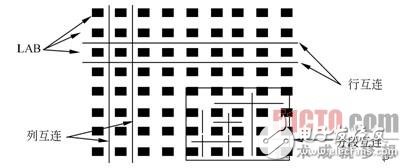

解决方法是把LAB排列在网格中,从而产生了现场可编程门阵列FPGA的概念,LAB都被排列在大型阵列中,器件可以现场编程或者重新编程,和CPLD一样。没有采用中心全局器件互连,而是把布线放置在LAB之间的空格上,就像大城市的街道。这种布线被排列成行列互连的形式。它可以跨过器件的整个长度和宽度,或者器件的一小部分,只覆盖行列中的几个LAB,如图1.9所示。

图1.9 FPGA互连结构图

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD宏单元相似,但更容易配置,有更丰富的特性来提高性能,减少逻辑资源的浪费。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CPLD和FPGA的区别是什么2023-07-03 11364

-

常用FPGA/CPLD设计思想与技巧2023-05-18 1151

-

FPGA与CPLD的区别是什么2021-09-22 2804

-

Altera FPGA CPLD学习笔记2021-09-18 1691

-

CPLD/FPGA的基本知识2021-03-30 1458

-

CPLD和FPGA的基本结构2020-09-25 14769

-

FPGA教程之CPLD与FPGA的基础知识说明2019-02-27 1719

-

CPLD和FPGA两者的区别2018-05-24 51123

-

关于CPLD和FPGA的区别2017-09-18 1169

-

FPGA/CPLD的设计思想2016-02-17 836

-

FPGA/CPLD与单片机相比有哪些优势?2012-02-27 16170

-

FPGA/CPLD设计思想与技巧2010-11-04 863

-

altera fpga/cpld设计2009-07-10 878

-

Altera FPGA/CPLD设计(高级篇)2009-02-12 4621

全部0条评论

快来发表一下你的评论吧 !