FPGA的多通道数据采集传输系统

描述

一、系统总体方案设计

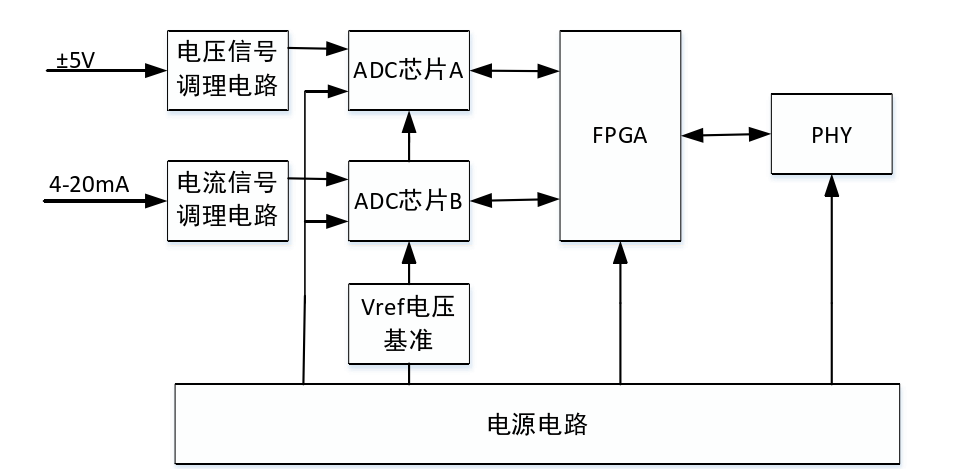

为了满足油田增压站对数据采集的需求,我们设计了一套基于FPGA的多通道数据采集与传输系统。系统以FPGA作为主控制器,利用外部ADC芯片完成模拟信号的采集,通过以太网实现与上位机的人机交互。

需求分析:油田增压站的环境复杂,采集信号类型多样,包括温度、压力、流量等模拟信号。系统需要实现对多通道信号的实时采集与传输,并具备较高的采集精度和稳定性。

系统架构:系统主要由FPGA、ADC芯片、以太网模块和上位机软件组成。FPGA负责系统的核心控制,包括信号采集、数据处理和数据传输。外部ADC芯片将模拟信号转换为数字信号。通过以太网模块,数据传输至上位机进行处理和显示。

系统的总体设计流程如下:首先,外部传感器将模拟信号输入到ADC芯片中,FPGA通过SPI通信协议读取ADC的数字信号,对数据进行滤波和组帧处理后,通过以太网发送至上位机。上位机软件将接收到的数据进行解析和可视化显示。

二、硬件电路设计与FPGA内部逻辑设计

1. 硬件电路设计

硬件电路设计是实现多通道数据采集传输的基础,包括关键芯片的选型、原理图设计和PCB布板。

关键芯片选型:

FPGA:选择一款具有足够I/O口、内存和处理能力的FPGA芯片。Altera Cyclone系列或Xilinx Spartan系列是常用的选择,具有丰富的外围接口资源和较高的性价比。

ADC芯片:选择支持多通道输入和高采样速率的ADC芯片,如TI公司的ADS1256或Analog Devices的AD7606。这些芯片支持多通道同步采样,具备较高的分辨率(24位)和采样精度。

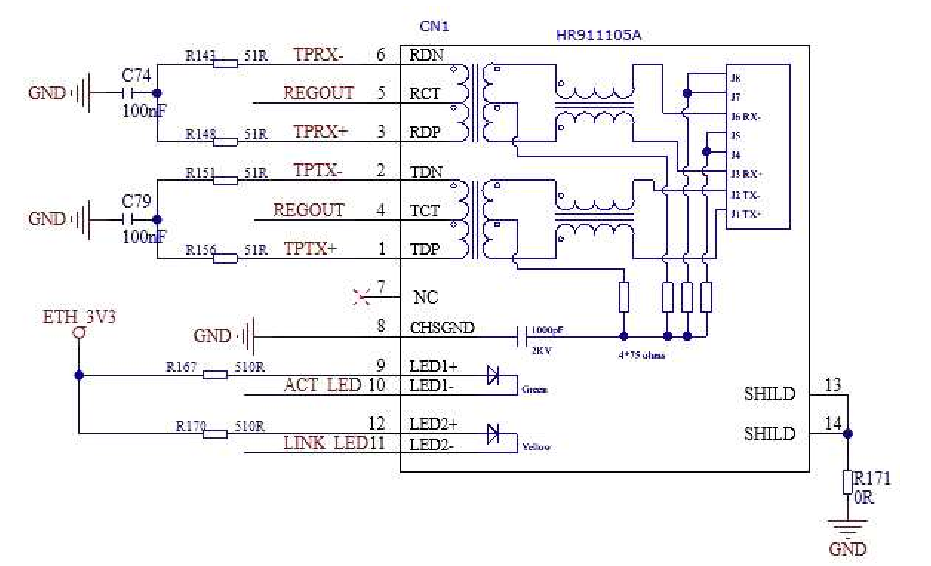

以太网模块:选用常见的以太网PHY芯片,如Wiznet的W5500或Microchip的ENC28J60,实现以太网通信。

电路设计:

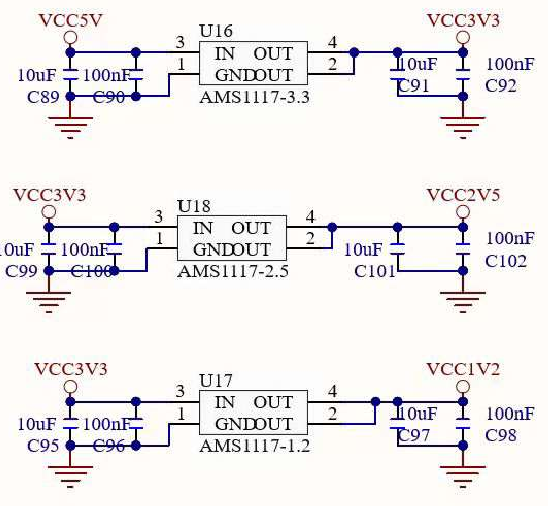

原理图设计:根据功能需求绘制系统的原理图,包括FPGA与ADC芯片的SPI接口电路、FPGA与以太网模块的接口电路,以及电源管理和信号调理电路等。

PCB设计:完成原理图设计后,进行PCB布局布线,确保高速信号传输的完整性和系统的稳定性。注意地线和电源的布置,避免噪声干扰。

2. FPGA内部逻辑设计

FPGA内部逻辑设计是整个系统的核心,包括SPI通信模块、数字滤波模块和数据传输模块。

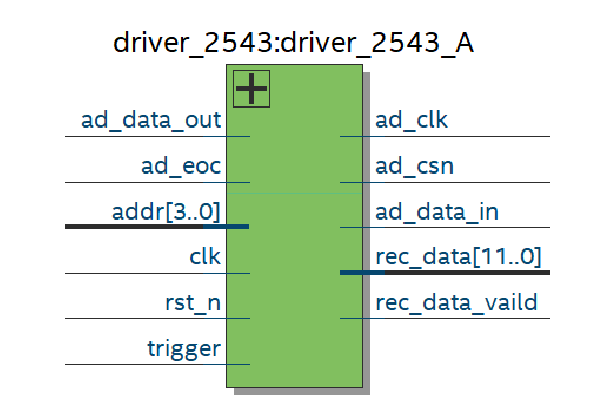

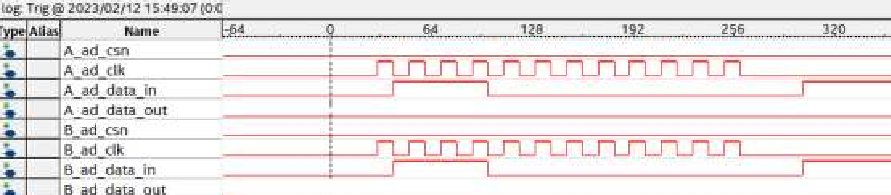

SPI通信模块:FPGA通过SPI协议与ADC芯片通信,完成多通道数据的采集。设计一个支持SPI主机模式的模块,用于控制ADC芯片的工作模式和数据读取。该模块包括SPI时钟的生成、数据的发送与接收,以及片选信号的控制。

数字滤波模块:为了减少现场高频噪声对采集数据的影响,在FPGA中实现了一个FIR数字滤波器。该滤波器对从ADC采集到的信号进行滤波处理,消除高频噪声,确保数据的准确性。FIR滤波器的设计需要根据系统的采样率和信号特性选择合适的滤波器系数,确保在不失真信号的情况下消除噪声。

数据组帧与传输模块:为了方便上位机识别采样数据来自具体的设备和通道,对采集到的数据进行自定义组帧处理。每帧数据中包括通道标识、数据值和校验信息等。组帧完成后,FPGA通过以太网模块将数据发送至上位机。数据传输模块采用UDP协议实现,确保数据的实时性和可靠性。

三、上位机软件设计

为了实现数据的实时显示和控制下位机的采集功能,设计了基于LabVIEW的上位机软件。其主要功能包括:

数据采集控制:上位机通过以太网发送命令,控制FPGA实现数据采集的启停。LabVIEW提供了丰富的网络通信控件,可以方便地实现与下位机的交互。

数据解析与显示:接收FPGA传输的数据,对数据进行解析,包括提取通道标识和采样值。将解析后的数据转换为波形曲线,并在上位机界面进行实时显示。LabVIEW具有强大的图形化界面设计功能,能够直观地呈现采集到的信号。

数据存储与分析:除了实时显示外,上位机还可以将采集到的数据存储在本地文件中,供后续分析和处理。LabVIEW支持多种数据存储格式,如文本文件、Excel文件等。

四、系统测试与性能验证

为了验证数据采集传输系统的功能完整性和可靠性,搭建了测试平台对系统进行了全面测试。测试包括以太网数据传输的可靠性、采集数据的精度和系统整体功能。

以太网数据传输测试:测试以太网模块的传输性能,验证数据在传输过程中是否存在丢包或延迟等问题。实验结果表明,系统的数据传输稳定,丢包率低于0.1%,传输延迟在可接受范围内。

数据采样精度测试:对系统的采样精度进行测试,使用标准信号源向系统输入已知信号,采集后与原始信号进行对比。实验结果显示,系统的采样误差在±0.1%以内,达到了设计要求的精度。

系统整体功能测试:包括从信号采集、数据传输到上位机显示的完整流程测试。实验中,上位机软件能够准确控制FPGA的采集启停,并实时显示采集到的信号波形。系统整体运行稳定,满足数据采集、传输与显示的功能需求。

// SPI通信模块

module spi_master (

input clk,

input rst_n,

input start,

input [7:0] data_in,

output reg miso,

output reg sclk,

output reg cs_n,

output reg [7:0] data_out,

output reg done

);

reg [2:0] bit_cnt;

reg [7:0] shift_reg;

reg state;

// SPI时钟产生

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

sclk <= 1;

end else begin

sclk <= ~sclk;

end

end

// SPI状态机

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cs_n <= 1;

bit_cnt <= 3'b0;

state <= 0;

done <= 0;

end else begin

case (state)

0: begin

if (start) begin

cs_n <= 0;

shift_reg <= data_in;

bit_cnt <= 3'b111;

state <= 1;

end

end

1: begin

if (bit_cnt == 3'b000) begin

state <= 2;

end else begin

sclk <= ~sclk;

if (sclk) begin

miso <= shift_reg[7];

shift_reg <= {shift_reg[6:0], 1'b0};

bit_cnt <= bit_cnt - 1;

end

end

end

2: begin

cs_n <= 1;

data_out <= shift_reg;

done <= 1;

state

-

多通道数据采集串扰问题怎么解决2024-07-02 3994

-

多通道数据采集系统的优缺点2024-07-01 3747

-

旋转环境下基于FPGA的多通道数据采集系统设计2023-08-08 2413

-

多通道位移数据采集系统2019-12-31 2342

-

如何使用FPGA进行多通道同步数据采集系统的设计2018-12-18 1619

-

如何使用FPGA进行超多通道高速数据采集系统的构成和设计过程资料概述2018-10-16 1505

-

基于FPGA和USB接口的多通道数据采集系统2011-12-28 785

-

基于FPGA的多通道同步数据采集存储系统2010-12-27 1207

-

基于CVI的多通道数据采集系统2009-12-31 1231

-

基于FPGA的多通道数据采集系统设计2009-10-25 1774

-

基于PCI总线多通道数据采集系统的设计2009-10-22 1632

全部0条评论

快来发表一下你的评论吧 !