人工智能应用中的异构集成技术

描述

引言

2022年ChatGPT的推出推动了人工智能应用的快速发展,促使高性能计算系统需求不断增长。随着传统晶体管缩放速度放缓,半导体行业已转向通过异构集成实现系统级缩放。异构集成技术可将不同类型的芯片(chiplet)组合到统一封装中,提供更好的性能、更低的互连延迟和更高的能源效率,这些对于数据密集型人工智能工作负载都非常重要[1]。

现有异构集成技术

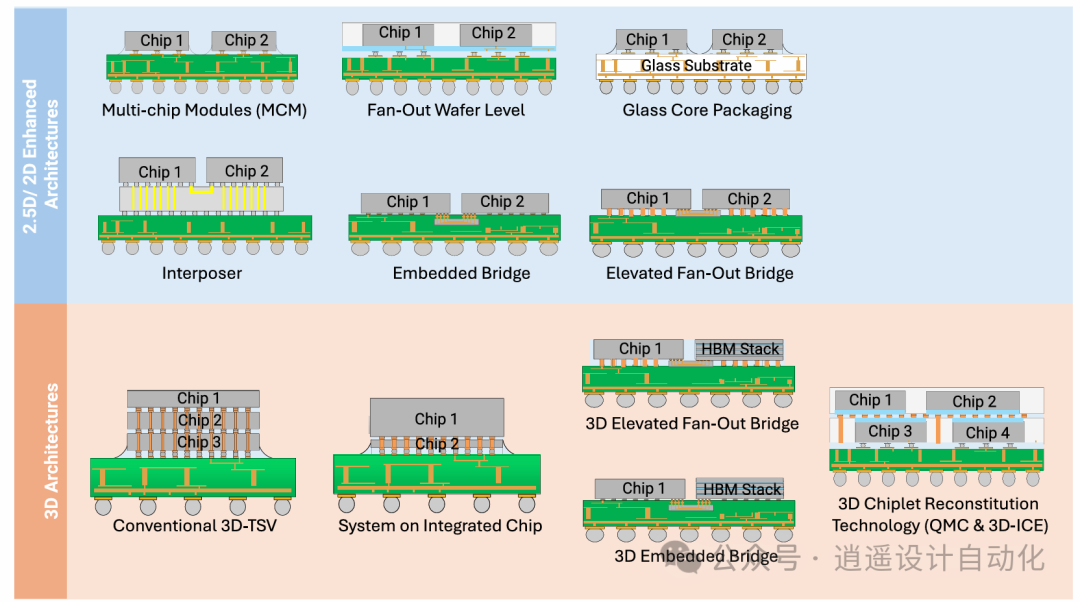

图1展示了异构集成技术的全面发展概况,从2D到3D架构的演进,包括MCM、中介层和先进的3D集成方法。

多种异构集成技术已经出现,以满足不同的系统要求:

多芯片模块(MCM):作为最早的2D集成方法之一,MCM将chiplet横向放置在有机基板上以减少线长。虽然实施简单,但由于使用传统有机基板和粗糙的焊料基连接技术,MCM在互连密度方面存在限制。

中介层架构:为克服MCM的局限性,采用玻璃或硅中介层的2.5D架构可实现更高的互连密度。通过硅通孔(TSV)技术和细间距微凸点,可以在堆叠芯片之间实现更高的连接密度。但是,为大型人工智能系统扩展中介层的成本较高。

桥接基解决方案:英特尔的嵌入式多芯片互连桥(EMIB)等技术在封装基板中使用局部硅桥实现细间距布线。这种方法无需TSV,同时能实现芯片间的高密度连接。

晶圆级封装:晶圆级封装技术通过扇出芯片I/O信号提供高互连密度和减少延迟。但在热管理和热膨胀系数(CTE)失配方面存在挑战。

三维集成

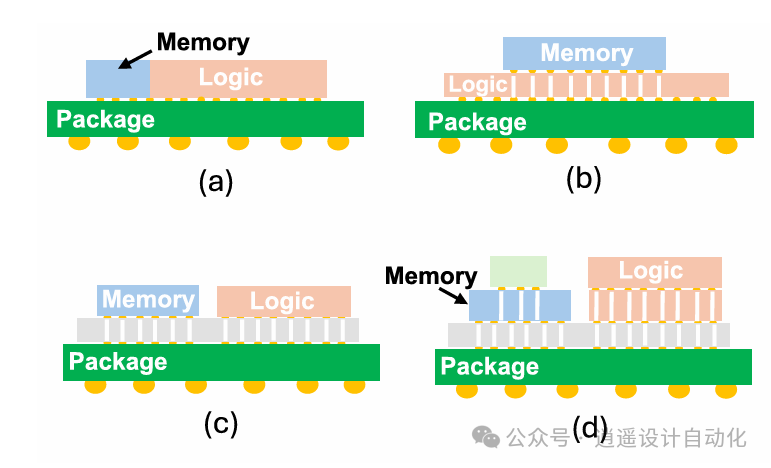

图2说明了不同的3D集成方法,展示了从传统2D SoC到结合逻辑和存储器集成的各种3D架构的演进。

3D集成是下一代人工智能系统的重要发展方向。使用TSV技术和混合键合等先进键合技术,3D堆叠实现了超高的集成密度和带宽。台积电等公司通过系统级集成芯片(SoIC)技术已经展示了支持超过20 Tbps带宽的系统。

3D集成的主要优势:

与传统方法相比,键合密度显著提高

降低电气寄生效应和功耗

更高的金属布线密度

通过更薄的键合层改善热性能

但仍面临一些挑战:

更多堆叠管芯增加了assembly复杂性

热管理更加困难

混合键合对表面处理要求严格

制造成本较高

人工智能硬件的工业应用

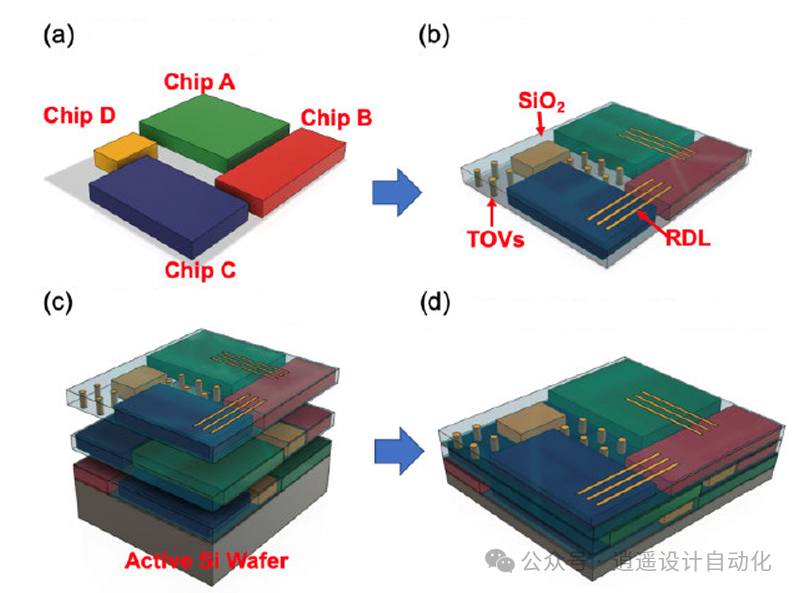

图3演示了3D-ICE技术工艺流程,展示了使用二氧化硅封装和晶圆键合集成多个chiplet的步骤。

主要半导体公司已在人工智能加速器产品中采用异构集成:

Cerebras:WSE-3晶圆级引擎使用台积电5nm技术,在单个晶圆上集成4万亿晶体管。

系统可训练具有24万亿参数的模型。

NVIDIA:GB200 Grace Blackwell使用台积电的CoWoS-L封装技术组合两个GPU和一个CPU。

目标是处理超过十万亿参数的大型语言模型,具有384GB内存。

AMD:MI300X封装同时使用中介层技术和3D堆叠,结合GPU chiplet、I/O管芯和192GB HBM内存。

英特尔:Gaudi-3加速器采用EMIB技术集成计算管芯和128GB HBM内存。

新兴玻璃封装技术

玻璃封装由于以下优势,在人工智能应用中备受关注:

通过低介电常数实现优异的信号完整性

支持高密度互连

出色的尺寸稳定性

灵活的基板格式选项

与光电集成的兼容性

玻璃的光滑表面使其能够实现非常精细的线条和间距,而其Si-O表面结构促进了与各种材料的良好粘附。玻璃核心封装还可以通过铜结构和先进的热界面材料整合热管理解决方案。

结论

异构集成技术已超越传统缩放限制,推进人工智能硬件能力的发展。从2.5D中介层到先进的3D堆叠和新兴的玻璃封装解决方案,这些方法实现了下一代人工智能系统所需的高带宽、低延迟和能源效率。在热管理和制造成本等方面仍存在挑战,但异构集成技术的持续创新将满足人工智能应用不断增长的需求。

参考文献

[1] M. Manley et al., "Heterogeneous Integration Technologies for Artificial Intelligence Applications," IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, vol. 10, pp. 89-97, 2024, doi: 10.1109/JXCDC.2024.3484958.

-

人工智能是什么?2015-09-16 6401

-

人工智能技术—AI2015-10-21 9747

-

人工智能传感技术2016-06-03 34917

-

百度人工智能大神离职,人工智能的出路在哪?2017-03-23 7978

-

人工智能就业前景2018-03-29 8387

-

「深圳云栖大会」大数据时代以及人工智能推动下的阿里云异构计算2018-04-04 1818

-

解读人工智能的未来2018-11-14 4856

-

人工智能技术及算法设计指南2019-02-12 5146

-

人工智能医生未来或上线,人工智能医疗市场规模持续增长2019-02-24 5819

-

人工智能:超越炒作2019-05-29 4976

-

异构计算在人工智能什么作用?2019-08-07 3677

-

路径规划用到的人工智能技术2021-07-20 2373

-

人工智能芯片是人工智能发展的2021-07-27 6629

-

物联网人工智能是什么?2021-09-09 5296

-

《移动终端人工智能技术与应用开发》人工智能的发展与AI技术的进步2023-02-17 2323

全部0条评论

快来发表一下你的评论吧 !