通过Xilinx FFT IP核的使用实现OFDM

可编程逻辑

描述

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109。关于OFDM理论背景,可参考如下博文:给"小白"图示讲解OFDM的原理 - CSDN博

https://blog.csdn.net/madongchunqiu/article/details/18614233/

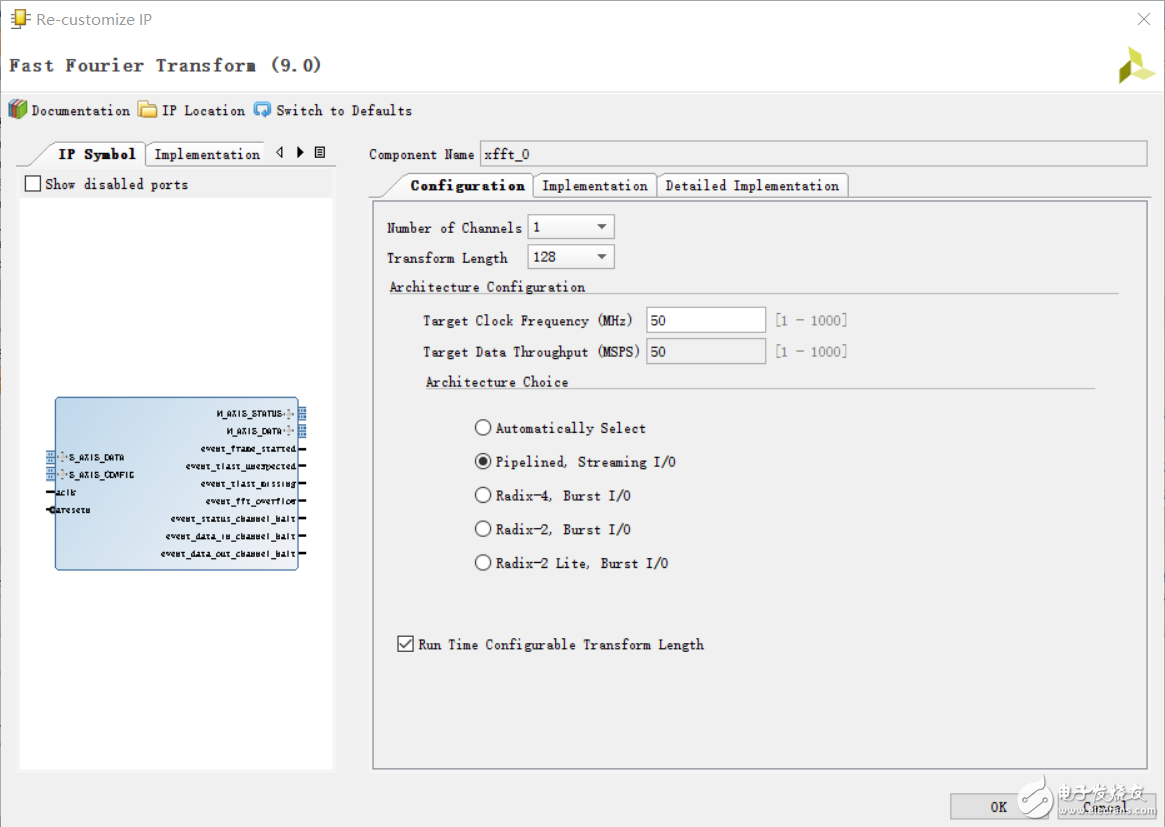

我们直接来看看FFT IP核配置界面:

由于OFDM接收机中大多是数据串并转换后的连续低速并行数据流输入FFT,故这里采用流水线结构。之后根据OFDM子载波数选择变换长度。该IP核仅支持50MHZ采样率数据的流水线处理,如果数高速通信场合,可以再次将数据串并转换用多个FFT IP核并行运算,也就是FPGA设计中常用的“面积换速度”。

第二页中比较重要的是选择数据格式和缩减 截断处理。此IP核支持浮点运算,但随之会消耗大量的硬件资源,且延迟也较大,所以多采用定点运算方式。定点运算中固定的bit位宽很容易出现数据溢出,在蝶形运算过程中仅保留高位而整体右移可把计算过程中增加的位宽去除掉,最后再左移即可,显然这种做法是在牺牲计算精度来降低硬件资源。设置Scaling Options为Scaled则在FFT IP核配置通道可以自定义缩减因子。当设置缩减位宽后,选中本页左下角的OVFLO溢出信号,仿真过程中可以通过溢出信号确定合适的缩减因子。

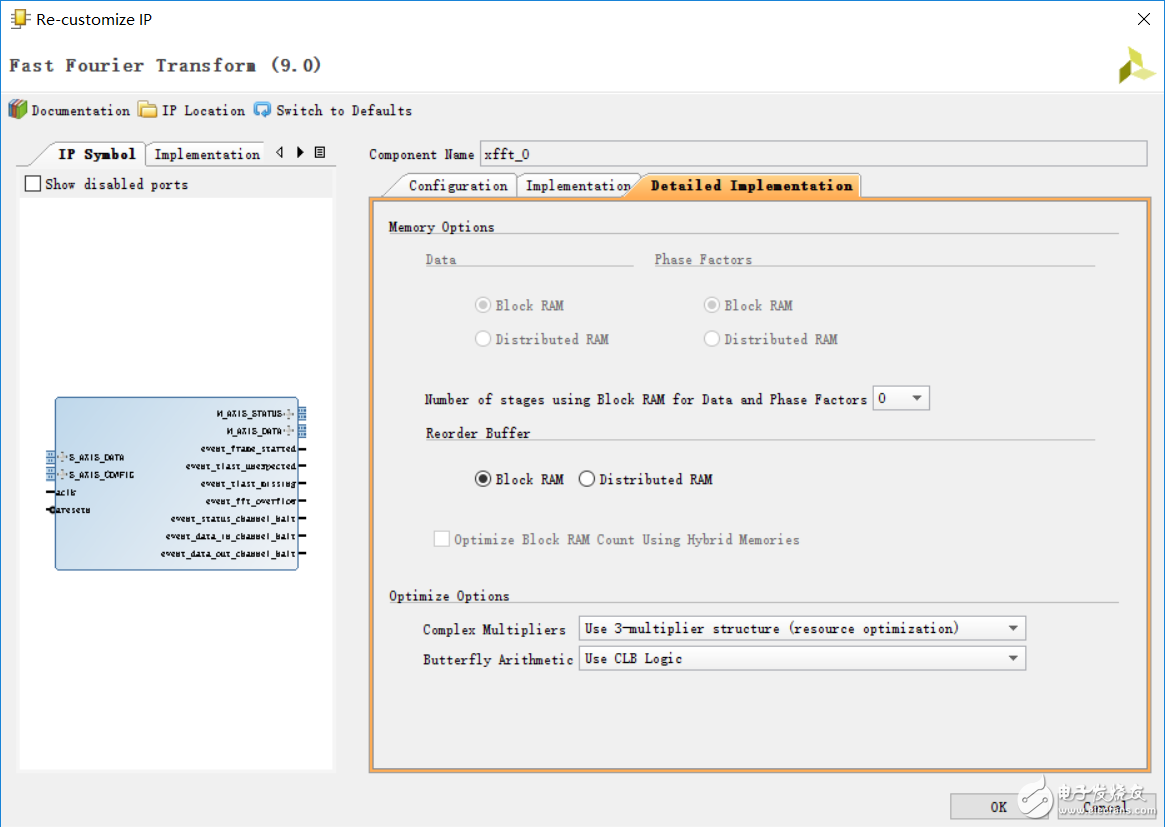

第三页主要是设置底层资源,对功能没有多大影响。存储部分可以用BRAM和DRAM两种资源,这里普及下:两者主要的区别在于BRAM是FPGA内部专用的硬件存储资源,用不用都在那里(你见或者不见,我就在那里,不来不去。。。好像在哪里见过),而DRAM是利用SLICEM中的LUT搭建出来的,相当于是BRAM的补充。在存储量较小时,DRAM可能会表现出更好的功耗和速率优势。正如官方文档介绍的,在变换长度小于1024,即占用存储资源少的情况下可使用DRAM。而下面的Optimize Options则可以权衡使用CLB和DSP Slices。

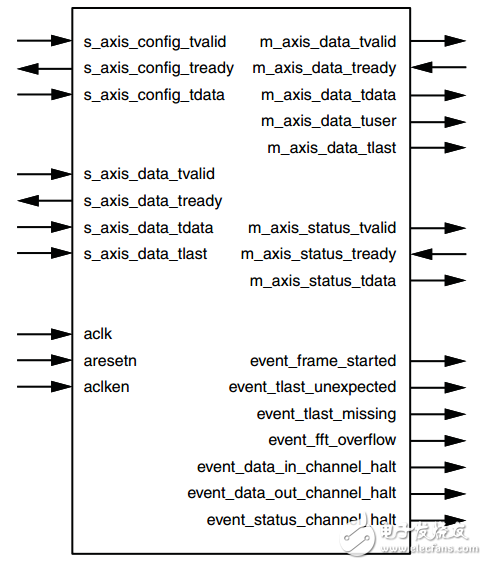

接口和配置可以说是所有IP核使用的重中之重。

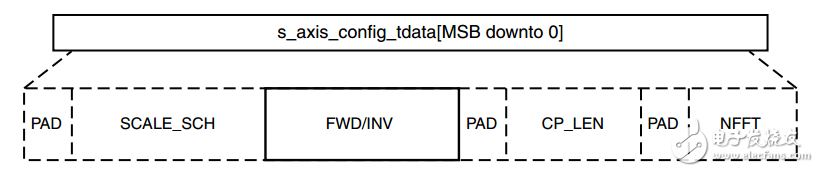

AXI总线的统一封装给IP核调用带来了很多方便,各部分功能通道相互分开结构非常清晰。每个通道的data以字节为单位的packet传输信息,如config通道信息如下:

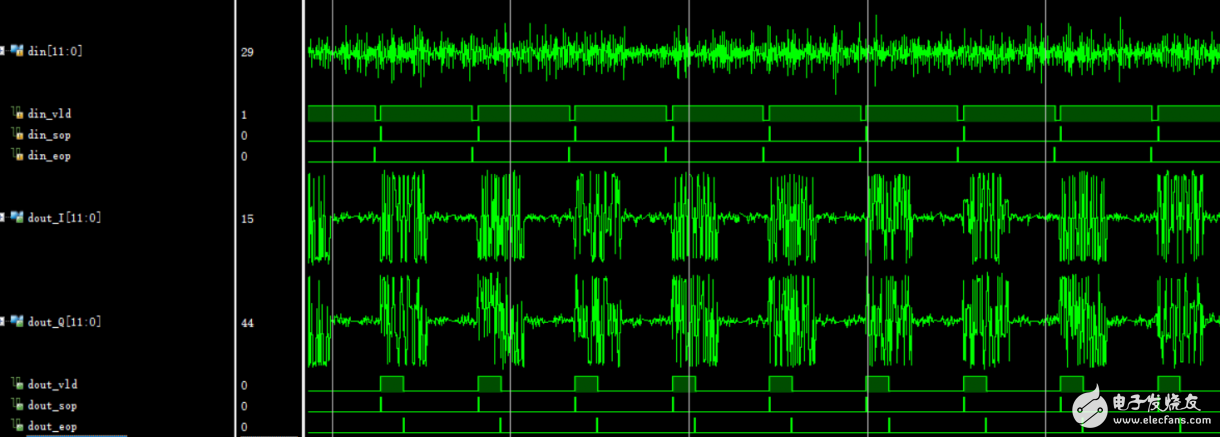

在这一通道中要在数据进入前设置好变换方式和缩减因子,此处配置为正变换,缩减因子[1 1 1 1]。给大家看下OFDM接收机工程中FFT运算部分的仿真波形图:

din是DD-OFDM ADC 接收数据,只有一路实部信号。dout_I,dout_Q分别是FFT运算后复数中的实部和虚部。显然FFT运算后得到了信号的不同频率成分,下面的dout_vld负责提取赫比特对称中数据载波。希望本文能起到抛砖引玉的作用,欢迎交流~

-

Vivado中FFT IP核的使用教程2024-11-06 6404

-

如何申请xilinx IP核的license2024-10-25 2742

-

从Xilinx FFT IP核到FPGA实现OFDM2023-07-10 2291

-

Xilinx FFT IP介绍与仿真测试2022-03-30 4578

-

【Mill】Xilinx ip FFT变换,为什么你的matlab数据无法严格比对?——无线通信连载2020-02-16 5551

-

基于FPGA的FFT和IFFT IP核应用实例2019-08-10 6167

-

xilinx FFT ip核仿真的误差太大?2018-07-10 4893

-

可配置FFT IP核的实现及基础教程2017-11-18 14210

-

xilinx FPGA的FFT IP核的调用2016-12-25 6544

-

Xilinx 的IP:1024点FFT快速傅立叶变换2016-06-07 1326

-

基于Xilinx_FPGA_IP核的FFT算法的设计与实现2016-05-24 956

-

adc采样后数据无法实现ofdm(fft)解调2013-08-14 4962

全部0条评论

快来发表一下你的评论吧 !