选择最适合您的系统需要的内存选项

描述

随着边缘和端点对更高功能和智能的需求不断增长,这些设备对更强处理能力和更大内存的需求也在增长。应用程序的功能更加丰富,用户要求其产品中内置更高级别的功能,包括复杂的图形和用户界面、学习算法、网络连接和高级安全性。目前,机器学习实现了语音和视觉AI功能,可帮助设备在边缘做出智能决策,并在无需人工干预的情况下触发操作。复杂的软件框架是这些解决方案的重要组成部分。

虽然处理能力是所有这些类型应用程序的关键,但它们也推动了对代码和数据的快速、可靠、低功耗和非易失性存储的需求。在开发嵌入式系统时,设计人员的内存选择会显著影响性能、成本、设计复杂性和功耗。需要新的架构来满足对更高性能、更大内存和更低功耗的不断变化的需求,同时保持低成本。需要与内存制造商密切合作,以确保满足性能要求的解决方案经过全面验证。我们来看看各种内存架构选项及其最佳使用案例。

内部闪存或外部存储器

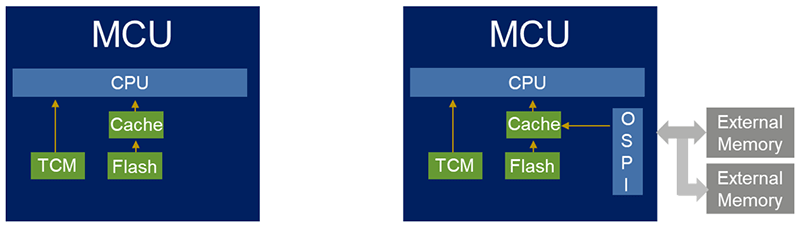

传统上,中低性能应用中使用的通用MCU将嵌入式闪存(通常为<2MB)作为代码的首选非易失性存储。这些集成MCU非常适合工业或楼宇自动化、医疗、家用电器或智能家居等不同细分市场中的大多数中低端物联网应用。嵌入式闪存具有许多优势,包括更低的延迟、更低的功耗和更高的性能,并提供了集成度更高的方案,适用于简化、空间有限的应用以及低复杂的设计。从安全角度来看,它消除了外部的攻击面。因此,具有集成嵌入式闪存的MCU仍然是大多数性能和功能需求较低的应用的首选解决方案。

但是嵌入式闪存是有成本的,超过一定的内存密度(如2MB),成本开始变得高昂。嵌入式闪存成本高昂,并增加了MCU晶圆加工的复杂性和成本。嵌入闪存所需的额外制造步骤会显著增加硅的成本。

此外,MCU制造商越来越多地转向更先进、更精细的工艺几何结构,如28/22nm或更低,以便扩展到更高的性能并在片上集成更多功能。现在,通常可以看到速度在 400MHz至1GHz范围内的MCU,这些MCU支持高级图形、模拟、连接和安全功能,以及高级安全性,以防止数据/IP被盗和篡改。虽然这解决了性能需求,但在这些设备上嵌入内存成为一个挑战,因为嵌入式闪存在较低的工艺几何形状上不能很好地扩展,而且闪存单元不能有效地缩小到40nm以下。所有这些都使其在较低的工艺几何形状中可行性降低或成本更高。

外部存储器

设计人员正在考虑新的架构来缩小这一差距,并越来越多地将外部闪存用于要求更高、性能更高的应用。对更复杂用例(如高端图形、音频处理或机器学习)的支持驱动了这一需求,而独立内存价格的急剧下降推动了这一趋势。使用外部存储器可以扩展嵌入式系统中的代码和数据空间,因为外部闪存基本上是MCU存储器映射的一部分,可以直接读取并用于数据记录或软件存储和执行。

对于物联网产品制造商来说,将外部闪存用于其高性能应用具有多项优势,包括在存储器大小选择方面提供灵活性,以及使其设计面向未来。随着开发人员添加更多功能,需要更大内存,将较小容量的内存换成引脚兼容的更大容量的内存是一个相当普遍的做法。它还允许他们为各种设计采用统一的平台方法。

当然,也有缺点,例如访问外部存储器所涉及的额外延迟(通过使用Quad/Octal存储器及仔细使用缓存来减轻)、略高的功率以及外部存储器的额外成本。它还增加了电路板设计的复杂性,需要在PCB上进行额外的布线并注意信号完整性。

对于MCU制造商来说,将MCU与存储器分离,使他们能够转向更先进的工艺节点,以获得更高的性能、更高的功能和能效,并降低其器件成本。现在,大多数制造商都集成了四通道或八通道SPI接口,并支持就地执行(XiP)功能,允许与这些NOR闪存器件无缝连接。一些MCU支持动态解密(DOTF),它允许将加密图像存储在外部闪存中并安全地导入执行。该解决方案提供当今边缘应用所需的高性能、低功耗和高级安全性。

图1. 存储器拓扑–具有内部和外部闪存的MCU

外部存储器和环节措施的挑战

当然,外部存储器也存在挑战,包括对与外部闪存相关的延迟及其对整体性能的影响的担忧。通过使用四通道或八通道SPI接口,可以在一定程度上减轻这种带宽限制,该接口允许通过4条或8条并行线路传输数据,而不是使用常规SPI的单线传输数据。使用双倍数据速率(DDR),通过在时钟的上升沿和下降沿发送数据,可以将吞吐量增加一倍。外部闪存制造商还内置了对突发读取模式的支持,以便更快地访问数据,并且可以使用缓存来减轻一些延迟影响,但需要仔细管理软件以最佳方式使用缓存。系统设计人员还可以通过将代码传输到内部SRAM并在SRAM外执行以获得最高性能来缓解一些延迟问题。

还有担心使用外部闪存会带来更高的功耗,因此内存制造商特别注意优化这些设备的电流消耗。外部存储器存在一些安全风险,因为它增加了外部的攻击面,从而造成了可被黑客利用并需要保护的漏洞。这要求MCU制造商向Quad/Octal SPI接口添加加密/解密功能,以便可以安全地存储和引入加密代码。

将外部闪存与RA MCU配合使用

瑞萨的RA系列MCU集成了嵌入式闪存以及与外部存储器的多个存储器接口,以提供最大的灵活性和性能。它们支持四通道或八通道SPI接口,通过使用4条或8条数据线而不是通常的SPI接口线来提高数据吞吐量。这可以显著提高性能,尤其是在需要快速内存访问(如图形、音频或数据记录)的应用程序中。

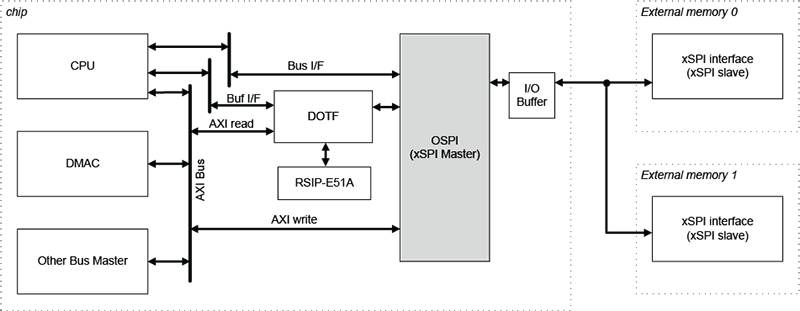

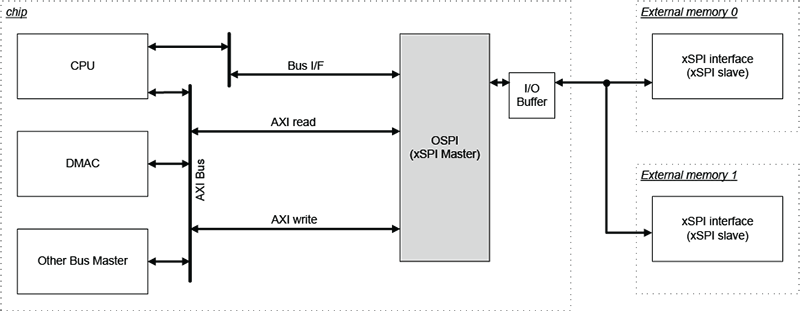

所有RA8系列MCU都包括一个符合eXpanded串行外设接口(xSPI)的八通道SPI接口。xSPI协议指定了非易失性存储设备的接口,并实现了高数据吞吐量、低信号数以及与传统SPI设备的有限向后兼容性。使用片选可以将两个外部存储器件连接到八通道SPI接口,如下所示,为设计人员提供了更大的灵活性。一些RA8 MCU还支持动态解密(DOTF),允许安全地导入存储在外部闪存中的加密图像进行执行。图2和图3显示了RA8 MCU上的八通道SPI接口,支持和不支持DOTF。

图2. Octal SPI支持DOTF

图3. Octal SPI不支持DOTF

Octal SPI接口的一些功能:

协议–xSPI,符合

- JEDEC标准JESD251(Profile 1.0和2.0)

- JESD251-1和JESD252

支持的存储器类型–八通道闪存和八通道RAM、HyperFlash和HyperRAM

数据吞吐量–高达每秒200MB

数据传输/接收–可以使用片选与最多2个从站通信,而不是并发

支持就地执行(XiP)操作

支持的模式

- 带SDR/DDR的1/4/8针(1S-1S-1S、4S-4D-4D、8D-8D-8D)

- 带SDR的2/4针(1S-2S-2S、2S-2S-2S、1S-4S-4S、4S-4S-4S)

内存映射

- 每个CS最多支持256MB地址空间

- 预取功能,用于低延迟的突发读取

- 出色的缓冲区,用于高吞吐量的突发写入

安全性–支持DOTF(在某些RA8 MCU上可用)

除了内部闪存和外部存储器接口外,RA8 MCU还包括紧密耦合存储器(TCM)和I/D缓存,有助于优化性能。TCM是零等待状态内存,在所有片上内存中具有最低的延迟;它可以用于代码的最关键部分。

使用RA8系列MCU上提供的各种存储器和存储器接口,可以实现多种灵活的存储器配置。代码可以存储在内部嵌入式闪存中并从内部嵌入式闪存执行,从而实现简单、低延迟、高度安全且节能的系统。然而,这不是一个可扩展的解决方案,任何超出嵌入式闪存大小的代码大小增加都需要通过外部存储器来解决。

在第二种配置中,代码存储在外部flash中并在外部flash执行。这是XiP功能,也是最灵活和可扩展的选项。随着代码大小的增加,外部存储器可以简单地换成引脚兼容、密度更高的器件,无需重新设计电路板即可轻松升级。这是以略高的功耗和更大的延迟为代价的,这可能会对整体性能产生影响。

代码也可以存储在外部闪存中,并引入内部SRAM或TCM执行。这提供了最高性能,因为代码是通过快速SRAM执行的,但是根据SRAM大小对代码大小有限制,如果代码大小超过可用的SRAM或TCM,则会增加软件复杂性。唤醒时间也可能增加,因为SRAM关闭时丢失的代码需要在每次重启时重新加载。

结论

在内存选项选择方面,没有单一的正确答案。虽然大多数中低端IoT应用程序可以使用内部闪存,但许多高性能应用程序需要使用外部闪存。内存选择必须基于几个考虑因素-应用程序要求、所需的内存大小、预期性能、系统架构、功耗目标、安全问题和未来的产品/平台计划等。

两种解决选项都有优点和缺点:

| 内部闪存 | 外部闪存 |

| 提供简单性 | 灵活性 |

| 紧密集成 | 内部扩展 |

| 高度安全的解决方案 | 可扩展性 |

| 适用于广泛的应用 | 非常适合新兴的loT和边缘AI应用 |

通过了解这些权衡,开发人员可以做出符合其项目目标的明智决策。

在每个器件产品页面上获取有关RA8 MCU系列上可用的灵活存储器选项的所有详细信息,以及数据表、样品和评估套件。

-

PROTEL新手最适合的教程我是受益匪浅希望对你有用2013-04-21 39682

-

请问任何人都有过IO标准最适合LPDDR内存的经验吗?2019-06-05 2038

-

嵌入式设计中,如何评估最适合应用的 RTOS?2019-07-26 4417

-

示波器的反应特性指的是什么?如何来选择最适合的示波器呢?2021-04-15 1640

-

如何挑选最适合的PXI/PXIe系统?2021-05-08 2194

-

MOSFET或IGBT哪一种驱动器最适合您的应用呢2021-11-08 3426

-

如何选择最适合自己的笔记本电脑2010-02-04 791

-

如何选择最适合的视频会议系统2010-02-21 979

-

什么手机最适合玩手机游戏?选骁龙痛快赢2018-09-07 1384

-

如何选择你的公司最适合最需求的MES制造执行系统2018-11-20 1076

-

最适合linux系统的笔记本2019-03-04 19438

-

如何才能购买到一个最适合您的数字货币钱包2019-03-18 3359

-

苹果13最适合买的配置2021-09-13 7254

-

如何在众多型号中选择最适合的SMT贴片机2023-05-15 2103

-

如何选择最适合你的UV LED固化机?2024-05-18 1379

全部0条评论

快来发表一下你的评论吧 !