一种适用于RFIC的抗击穿LDMOS设计文档

RF/无线

描述

LDMOS (Lateral Diffused MetalOxide Semiconductor Transistor,横向扩散金属氧化物半导体)以其高功率增益、高效率及低成本等优点,被广泛应用于移动通信基站、雷达、导航等领域。射频大功率 LDMOS由于具有P、L波段以上的工作频率和高的性价比,已成为3G手机基站射频放大器的首选器件。

随着IC集成度的提高及器件特征尺寸的减小,栅氧化层厚度越来越薄,其栅的耐压能力显著下降,击穿电压是射频LDMOS器件可靠性的一个重要参数,它不仅决定了其输出功率,还决定了器件的耐压能力,因此必须要采取措施以提高器件的击穿电压。

本文将在基本LDMOS的基础上,通过器件结构的改进来提高LDMOS的抗击穿能力。

1、LDMOS耐压特性

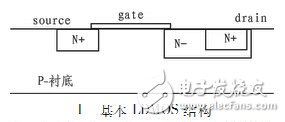

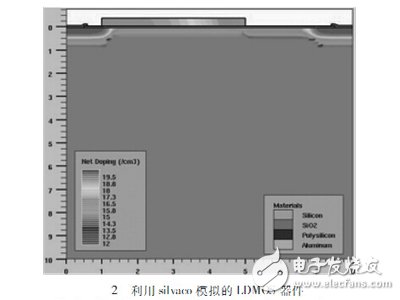

如图1所示,LDMOS最主要的结构特点是采用双扩散技术,在同一窗口进行磷扩散,沟道长度由两种扩散的横向结深决定。LDMOS中产生的击穿形式有栅绝缘层击穿和漏源击穿。

LDMOS高压器件是多子导电器件,由于漂移区将漏区与沟道隔离,Vds绝大部分降落在漂移区上,基本上没有沟道调制,所以当Vds增大时,输出电阻不下降。并且栅电极和漏区不重迭,从而提高了漏源击穿电压。

影响LDMOS耐压性能的因素很多,本文将从埋层、漂移区掺杂浓度、衬底掺杂浓度3方面进行分析各参数对其耐压性能的影响。

1.1、影响LDMOS耐压性能的主要参数

1.1.1、埋层

在 P衬底用离子注入法注入N型埋藏层(NBL),一方面,NBL与P衬底以及N+掺杂区形成寄生三极管,当有电压加在LDMOS器件的漏极时,可利用寄生三 极管形成电流放电路径,并且添加的N型埋层可以增加杂质的掺杂浓度,减小其内部电阻,从而更利于释放电流。另一方面,NBL可以降低沟道附近的等位线曲率 提高击穿电压,其电中性作用使漂移区的优化浓度提高,导通电阻降低,改善了漏极击穿特性。

1.1.2、漂移区掺杂浓度

漂移区 是LDMOS和MOS器件结构的主要差异之一,也正是由于低掺杂漂移区的存在使LDMOS击穿电压比传统MOS高很多。漂移区长度、深度和浓度对击穿电压 的影响很大,一般说来,漂移区长度越长,LDMOS击穿电压越高,但是当漂移区长度增加到一定值时,其击穿电压随着漂移区长度的变化逐渐变缓。击穿电压随 漂移区浓度的增大先增大后减小。

1.1.3、衬底掺杂浓度

衬底掺杂浓度的大小对击穿电压影响较大。由于pn结一边或者两边掺 杂浓度较低时,雪崩击穿是pn结主要的击穿机制,LDMOS的一次击穿是主要集中在漏极处的雪崩击穿,在一定范嗣内,衬底浓度越小,与漏极形成的反向PN 结的势垒宽度越宽,碰撞倍增次数越多,雪崩击穿也就越容易发生,击穿电压就越低。

1.2、提高LDMOS击穿电压现有的技术

目前,利用器件结构上的改进,进而提高LDMOS击穿电压的方法主要有:RESURF技术、漂移区变掺杂、加电阻场极板、内场限环等技术。

RESURF 技术:其基本原理是选择适当的漂移区掺杂浓度和厚度,控制漂移区表面的二维电场,使击穿发生在体内从而达到高击穿电压的目的。通过降低漂移区掺杂,在沟道 和漂移区结的电场尚未达到临界电场之前,利用P-衬底和N-漂移区的pn结将漂移区耗尽,增大了耗尽区边界的曲率半径,从而提高了击穿电压。

漂移区变掺杂:通过表面掺杂浓度的阶梯变化,在漂移区中部引入新的电场峰值,提高漂移区中部电场,且较高的掺杂位于表面,降低导通电阻的同时改善表面电场分布。

加电阻场极板:在漂移区上方形成电阻场板,电阻场板产生均匀分布的垂直电场施加于漂移区中,与水平电场交叠,使漂移区电场分布也均匀化,降低了电场强度,从而提高了击穿电压。

内场限环技术:在N-漂移区中插入P型区域,在漂移区内形成内场限坏时,内场限坏耗尽区的电场与表面电场方向相反,增大了栅场耗尽区的有效曲率半径,从而提高了器件耐压。

总体而言,RESURF技术无需增加额外的工艺,但须对衬底掺杂浓度、N阱掺杂浓度和N阱的厚度以及区域进行控制,精确度要求较高。漂移区变掺杂技术和加电 阻场极板工艺步骤较复杂,不利于电路的集成。内场限环技术需受到漂移区宽度及深度的限制,一般适用于漂移区较深,且浓度较高的LDMOS器件中。

2、LDMOS抗击穿设计

LDMOS器件的击穿电压主要集中在漏极处,此处的电场较集中,电场越集中,器件越容易击穿,因此,为了提高器件的击穿电压,可减弱其电场强度。

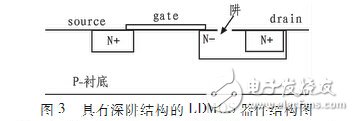

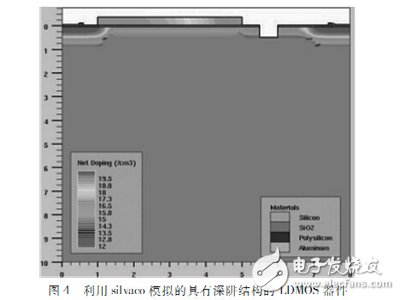

LDMOS器件工作时,栅极的末端存在一个峰值电场,为了减小其表面电场强度,可在漂移区引入阱结构。图3为具有阱结构的LDMOS结构图,图4为其相应的silvaco模拟仿真图。

阱结构可以是一个无任何介质的深槽,深槽的作用主要是从物理结构上改变器件的电场强度分布,减弱栅极末端的电场集中。为了进一步改善器件的电场分布,可在阱 结构中填充低介电常数的绝缘介质。阱中低介电常数的介质一方面截断器件的曲面结,消除电场集中:另一方面抑制了平面工艺的横向扩散,可承受更高的峰值电场。

Si、SiC、SiO2、GaAs的相对介电常数分别为11.6、10.0、3.9、13.1。相对而言,SiO2具有低的介电常数,适合填充在LDMOS的深阱结构中。

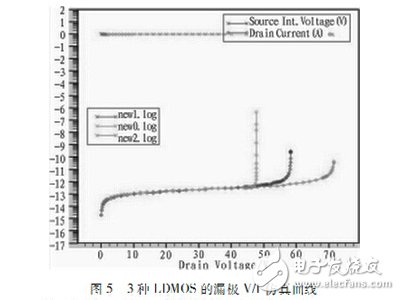

保持LDMOS器件掺杂浓度、栅长、阱宽等参数不变,如图5所示。new0.Log、new1.Log、new2.Log分别代表基本LDMOS、有深槽的 LDMOS以及完全填入SiO2的深阱的LDMOS漏极V/I仿真曲线。本文采用的深阱结构其阱宽和阱深都为0.5μm,从图5中可以看出,由于深槽的作 用,LDMOS击穿电压提高了10 V,当进一步在深槽中填入SiO2时,其击穿电压可再次提高12 V。通过对比分析可以说明,采用阱结构技术可以明显提高器件的抗击穿能力。

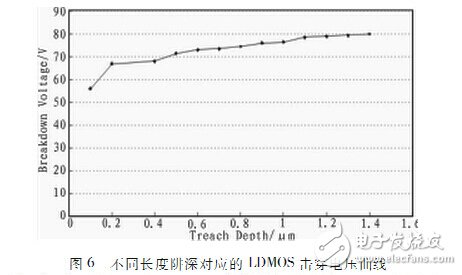

通 过进一步仿真实验发现,器件耐压性能与阱宽及阱深的尺寸有关。保持漂移区长度不变,阱宽为固定值0.5μm,图6为不同长度阱深对应的器件击穿电压曲线。 从图6中可以看出,随着阱深的加大,器件的抗击穿能力加强,这是由于阱深越大,耗尽区俞难越过阱区,且体硅中承受的最大电场的范围越大,LDMOS的耐压 就越高。

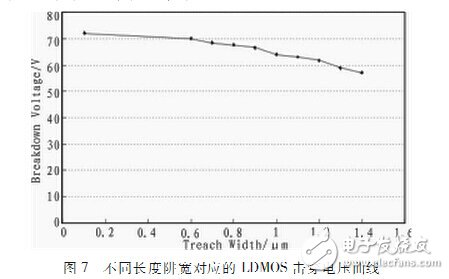

同样,保持漂移区长度不变,阱深为固定值0.5μm,图7为不同长度阱宽对应的器件击穿电压曲线。击穿电压随着阱宽的增加反而减小,这是因为阱宽的增加使得漂移区长度减小,总的耐压也就随之减小。

选择适当的阱宽及阱深,在阱中掺杂低介电常数介质,如SiO2,通过优化器件的结构参数可以得到击穿电压的最大值。

采用此深阱结构最大的优点是工艺方法简单有效,并且可利用深阱的宽度和深度以及深阱中填入何种介质或填入介质的多少来控制LDMOS的击穿电压,在实际工艺操作过程中可控性强。

3、结论

LDMOS 击穿电压易发生在栅极末端,器件衬底上添加埋层可以降低沟道附近的等位线曲率从而提高其击穿电压。漂移区将漏区与沟道隔离,抑制了器件的沟道调制,在一定 掺杂范围内,漂移区浓度越低,击穿电压越高。衬底浓度越低,雪崩击穿越容易发生,击穿电压就越低。本文采用的深阱结构主要为了减小栅极末端的电场强度,消 除电场集中,进而提高其抗击穿能力。

另外,由于栅极界面存在电荷,栅末端的峰值电场随栅长的增加而增加,为了抑制峰值电场集中导致器件的击穿,栅长不宜较长。漂移区长度可适当加大,阱深可尽量取较大值,结合器件掺杂浓度,最终可使射频LDMOS的抗击穿能力达到最优。

文 中设计的LDMOS器件主要是在耐压特性上做了改进,相对于RESURF技术、漂移区变掺杂、加电阻场极板、内场限环等技术而言,具有工艺简单,可控性强 的优点。其较高的抗击穿能力可适用于射频集成电路,如移动通信基站。当然,若将此器件应用于基站,还需要考虑射频LDMOS的其它电学特性,使器件的各个 参数达到作为基站功率放大器的要求。

-

一种适用于嵌入式系统的模块动态加载技术2021-12-20 1340

-

适用于开关电源的一种分布结构变压器设计2021-09-24 929

-

求大佬分享一款适用于激光及MRI的宽带LDMOS晶体管2021-06-08 1873

-

一种适用于模拟/数字混合信号环境的接地技术2021-04-25 1486

-

如何使用深阱工艺提高LDMOS的抗击穿能力2020-09-25 1634

-

如何利用RFIC设计抗击穿LDMOS?2019-07-31 3170

-

一种适用于RFIC的抗击穿LDMOS设计2017-12-05 479

-

一种适用于RFIC的抗击穿LDMOS设计2017-11-23 970

-

LDMOS耐压特性与射频集成电路的抗击穿LDMOS设计2017-10-13 2506

-

一种适用于医学领域的频率可调滤波器2017-01-07 780

-

一种适用于多规格定子绕组制作的绝缘内圈2017-01-02 678

-

一种适用于射频集成电路的抗击穿LDMOS设计2013-05-06 1243

全部0条评论

快来发表一下你的评论吧 !