带通滤波器电路图大全(三款带通滤波器电路设计原理图详解)

应用电子电路

描述

带通滤波器电路图设计(一)

传统的带通滤波器设计方法中涉及了很多复杂的理论分析和计算。针对上述缺点,介绍一种使用EDA软件进行带通滤波器的设计方案,详细阐述了使用FilterPro软件进行有源带通滤波器电路的设计步骤,然后给出了在Proteus中对所设计的滤波器进行仿真分析和测试的方法。测试结果表明,使用该方法设计的带通滤波器具有性能稳定。设计难度小等优点,也为滤波器的设计提供了一个新的思路。

带通滤波器是一种仅允许特定频率通过,同时对其余频率的信号进行有效抑制的电路。由于它对信号具有选择性,故而被广泛地应用现在电子设计中。但是,带通滤波器的种类繁多,各个类型的设计差异也很大,这就导致了在传统滤波器的设计方法中不可避免地要进行大量的理论计算与分析,不但损失了宝贵的时间,同时也提升了电路的设计门槛。为了解决上述弊端,本文介绍了一种使用FilterPro和Proteus相结合的有源带通滤波器的设计方案,随着EDA技术的不断发展,这种方法的优势也将越来越明显。

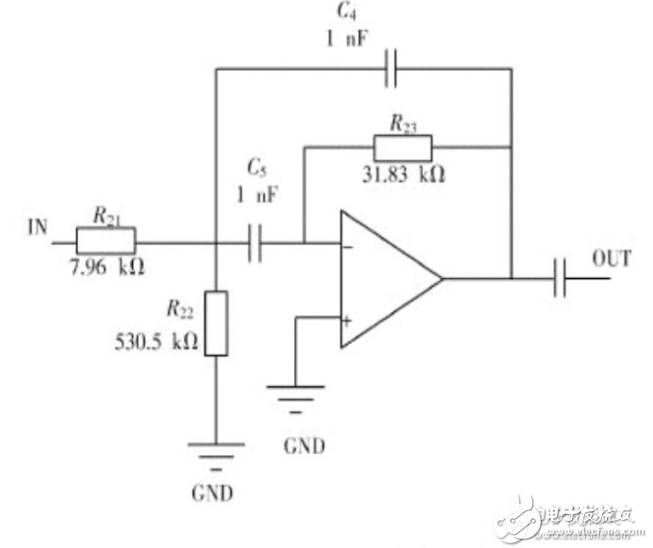

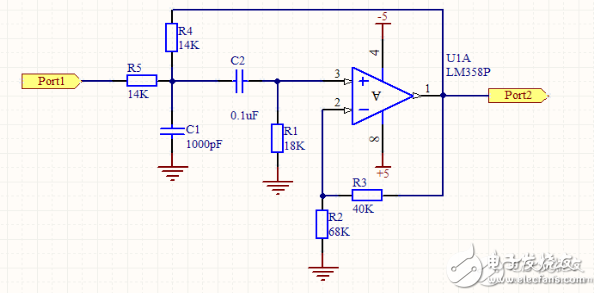

图1 使用理想运放的带通滤波器

电路原理图如图1所示。然后可在Proteus中搭建电路进行仿真分析,前面已经提到,FilterPro生成的滤波器中的运放使用的理想运放模型,所以仿真时需要先用理想运放进行分析,然后再进行替换。

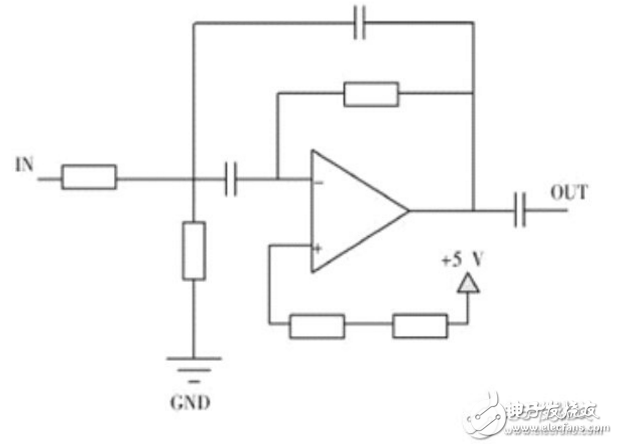

图2 实际搭建的滤波器电路

设计中运放选择TI产品典型的通用双放LM358,LM358里面包括两个高增益、独立的、内部频率补偿的双运放,适用于电压范围很宽的单电源,而且也适用于双电源工作方式,特点方面具有低输入偏置电流、低输入失调电压和失调电流,它的共模输入电压范围较宽,差模输入电压范围等于电源电压范围,单电源供电电压3-32V,双电源供电±1.5-±16V,单位增益带宽为1MHz,适用于一般的带通滤波器的设计,同时具有低功耗的功能,对于设计阶数相对高一些的带通滤波器的话,可以选用TI的四运放LM324,其性能与LM358大体相同,应用起来节省空间。对于运放的要求此设计不是特别高,只要运放的频率满足低通的截止频率即可,如果精确度要求高的话那么首先运放的供电电压要足够稳定,或者选择精密运放,如TLC274A,否则通用的即可,例如推荐TI的LM224四运放。

巴特沃斯带通滤波器幅频响应在通带中具有最平幅度特性,但是从通带到阻带衰减较慢,如果对于过渡带要求稍高,可以增加阶数来实现,否则改选用切比雪夫滤波电路。

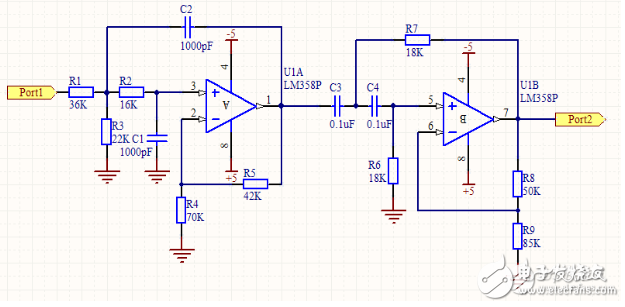

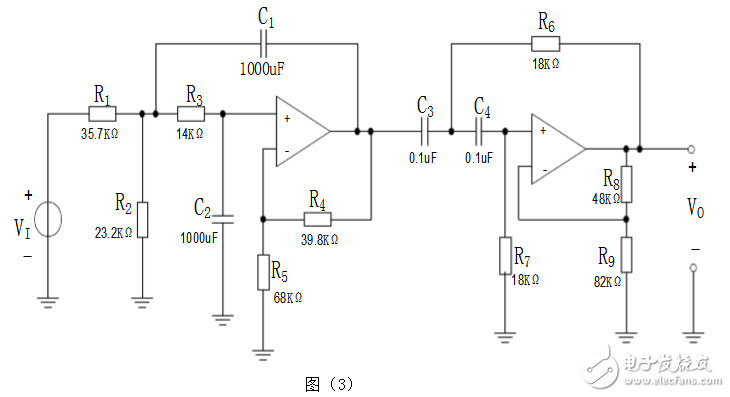

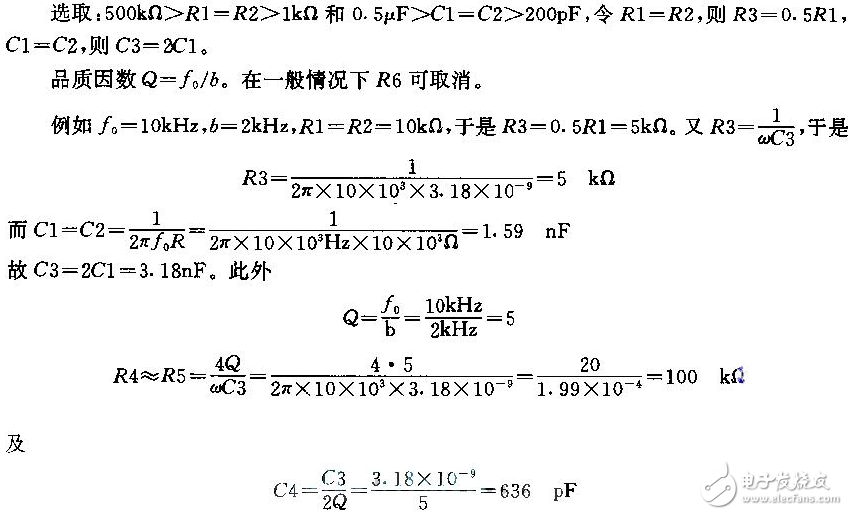

下面讨论设计两种带通滤波器,其一为二阶低通滤波器和二阶高通滤波器组成的四阶带通滤波器,如下图:

图 3 四阶带通滤波器

参数选择与计算:

对于低通滤波器的设计,电容一般选取1000pF,对于高通滤波器的设计,电容一般选取0.1uF,然后根据公式R=1/2Πfc计算得出与电容相组合的电阻值,即得到此图中R2、R6和R7,为了消除运放的失调电流造成的误差,尽量是运放同相输入端与反向输入端对地的直流电阻基本相等,同时巴特沃斯滤波器阶数与增益有一定的关系(见表1),根据这两个条件可以列出两个等式:30=R4*R5/(R4+R5),R5=R4(A-1),36=R8*R9/(R8+R9),R8=R9(A-1)由此可以解出R4、R5、R8、R9,原则是根据现实情况稍调整电阻值保持在一定限度内即可,不要相差太大,注意频率不要超过运放的标定频率。

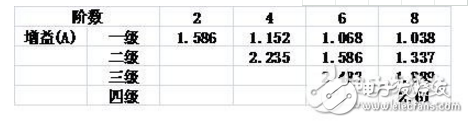

表1巴特沃斯低通、高通电路阶数与增益的关系

其二是二阶有源带通滤波器,只用一个放大区间,如下图:

图4 二阶带通滤波器

带通滤波器电路图设计(二)

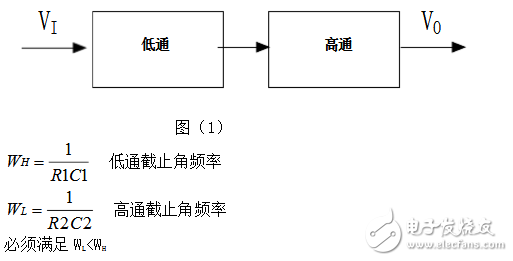

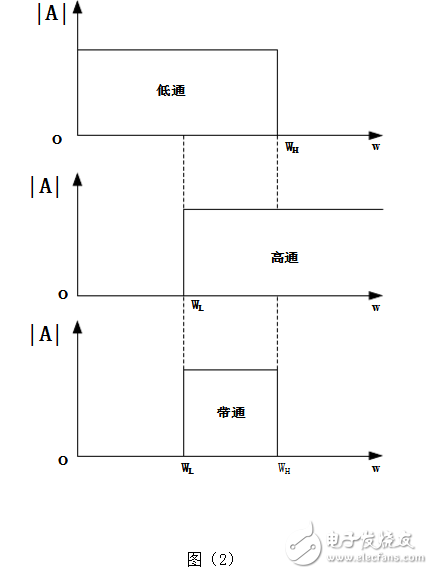

由图(1)所示带通滤波电路的幅频响应与高通、低通滤波电路的幅频响应进行比较,不难发现低通与高通滤波电路相串联如图(2),可以构成带通滤波电路,条件是低通滤波电路的截止角频率WH大于高通电路的截止角频率WL,两者覆盖的通带就提供了一个带通响应。

这是一个通带频率范围为100HZ-10KHZ的带通滤波电路,在通带内我们设计为单位增益。根据题意,在频率低端f=10HZ时,幅频响应至少衰减26dB。在频率高端f=100KHZ时,幅频响应要求衰减不小于16dB。因此可以选择一个二阶高通滤波电路的截止频率fH=10KHZ,一个二阶低通滤波电路的fL=100HZ,有源器件仍选择运放LF142,将这两个滤波电路串联如图所示,就构成了所要求的带通滤波电路。

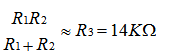

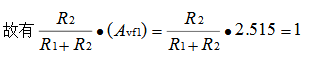

由巴特沃斯低通、高通电路阶数n与增益的关系知Avf1=1.586,因此,由两级串联的带通滤波电路的通带电压增益(Avf1)2=(1.586)2=2.515,由于所需要的通带增益为0dB,因此在低通滤波器输入部分加了一个由电阻R1、R2组成的分压器。

元件参数的选择和计算

在选用元件时,应当考虑元件参数误差对传递函数带来的影响。现规定选择电阻值的容差为1%,电容值的容差为5%。由于每一电路包含若干电阻器和两个电容器,预计实际截止频率可能存在较大的误差(也许是+10%)。为确保在100Hz和10kHz处的衰减不大于3dB.现以额定截止频率90Hz和1kHz进行设计。

前已指出,在运放电路中的电阻不宜选择过大或较小。一般为几千欧至几十千欧较合适。因此,选择低通级电路的电容值为1000pF,高通级电路的电容值为0.1μF,然后由式RCWC1可计算出精确的电阻值。

对于低通级由于已知c=1000pF和fh=11kHz,由式RCWC1算得R3=14.47kΩ,先选择标准电阻值R3=14.0kΩ。对于高通级可做同样的计算。由于已知C=0.1μF和fL=90Hz,可求出R7=R8≈18kΩ。

考虑到已知Avf1=1.586,同时尽量要使运放同相输入端和反相输入端对地的直流电阻基本相等,现选择R5=68k,R10=82k,由此可算出R4=(Avf1-1)R5≈39.8k,R9=(Avf1-1)R10≈48k,其容差为1%。

设计完成的电路如图所示。信号源vI通过R1和R2进行衰减,它的戴维宁电阻是R1和R2的并联值,这个电阻应当等于低通级电阻R3(=14k)。因此,有

由于整个滤波电路通带增益是电压分压器比值和滤波器部分增益的乘积,且应等于单位增益,

联解式和,并选择容差为1%的额定电阻值,得R1=35.7kΩ和R2=23.2kΩ。

带通滤波器电路图设计(三)

实用的带通滤波器电路原理图

该电路在负反馈支路上是一个带阻滤波齐器,以使其只允许通过被反馈支路阻断的频率信号。

-

我是一只鱼_97c

2021-06-27

0 回复 举报我想问一下,图三是只有一个LM358吗 收起回复

我是一只鱼_97c

2021-06-27

0 回复 举报我想问一下,图三是只有一个LM358吗 收起回复

-

无源带通滤波器电路,有源带通滤波器原理图2008-09-24 0

-

带通滤波器设计2008-12-01 5454

-

160Hz带通滤波器电路图2009-03-30 1163

-

多端反馈带通滤波器电路图2009-03-30 667

-

高Q带通滤波器电路图2009-03-30 1754

-

带通滤波器电路与幅频特性图2009-05-08 12978

-

典型带通滤波器电路图2009-05-08 3867

-

实用的带通滤波器电路原理图2009-12-07 4013

-

带通滤波器原理图2009-12-07 4070

-

带通滤波器设计原理图2016-01-15 1517

-

二阶有源带通滤波器原理图及设计流程2016-10-11 222229

-

低通滤波器电路图大全(六款低通滤波器电路设计原理图详解)2018-03-26 348803

-

电源滤波器电路图大全(八款电源滤波器电路设计原理图详解)2018-03-26 157618

-

220v电源滤波器电路图大全(五款220v电源滤波器电路设计原理图详解)2018-03-26 104471

全部0条评论

快来发表一下你的评论吧 !