芯片静电测试之HBM与CDM详解

描述

在芯片制造与使用的领域中,静电是一个不容小觑的威胁。芯片对于静电极为敏感,而HBM(人体模型)测试和CDM(充放电模型)测试是评估芯片静电敏感度的重要手段。

那么,HBM和CDM,这两种测试所代表的风险,哪个更大呢?

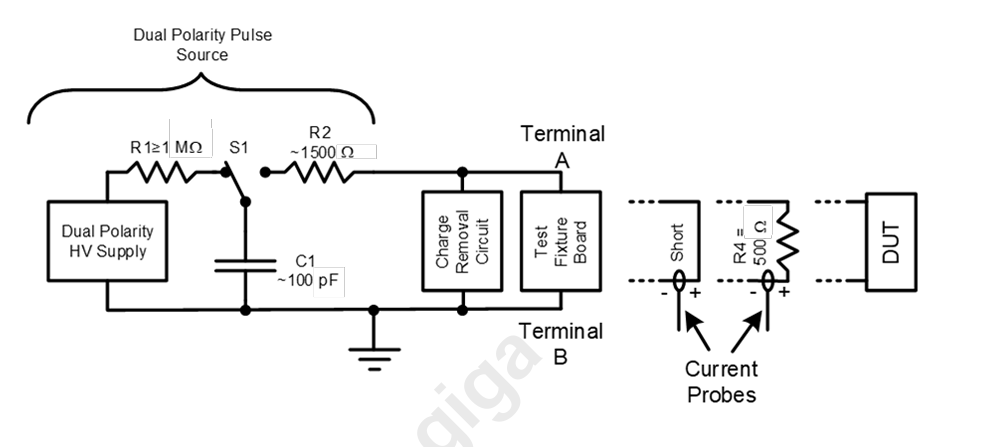

HBM测试主要是模拟人体在接触芯片时所产生的静电放电情况。在日常生活中,我们的身体在活动过程中会积累静电,当这些静电通过手指等接触芯片引脚时,就可能对芯片造成损害。在HBM测试中,通过特定的电路模拟出人体静电的放电波形和能量(如下图一)。其测试电压范围较广,一般从几百伏到上万伏不等。

这种测试方式所代表的风险主要在于:如果芯片在较低的HBM电压下就出现失效,那么在日常使用中,只要有类似人体静电放电的情况发生,芯片就可能损坏。比如一些消费电子类芯片,经常会有用户触摸操作,如果HBM抗静电能力差,产品在使用过程中就容易出现故障。

图一(引用自《ANSI/ESDA/JEDECJS-001-2024》标准)

CDM测试则聚焦于芯片自身带电所产生的静电放电情况。在芯片的生产、运输和组装过程中,芯片可能会因为摩擦等原因而带上静电。当芯片与接地的物体接触时,这些静电就会瞬间释放。

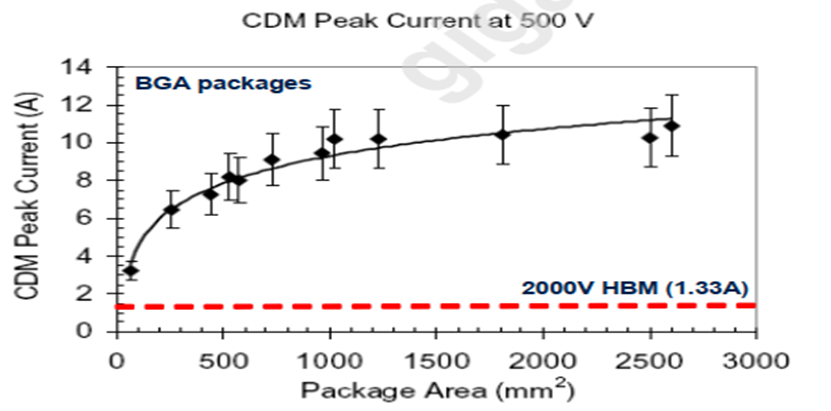

CDM测试的特点是放电时间非常短,通常在皮秒级别,但其放电电流却很大。这意味着芯片在这种情况下所承受的能量冲击是非常强烈的。例如在芯片制造的自动化生产线中,芯片在高速传输过程中如果CDM抗静电能力不足,就可能在与设备接触瞬间被静电损坏,导致生产良率下降。

从芯片的使用场景来看,对于那些经常会被人体接触的芯片,如手机芯片、电脑鼠标等设备中的芯片,HBM测试所代表的风险就显得尤为关键。

但对于芯片的生产环节,特别是自动化程度高、芯片频繁在设备之间传输的情况,CDM测试的风险则更为突出。

如今随着芯片功能迭代的增加,采用了先进制程、更小晶体管尺寸的芯片,更大规模的封装,充放电量更大,更容易被瞬间的大电流破坏;而HBM的ESD能量不变,比较稳定,在迭代过程中风险相对小,所以从某种程度上来说,CDM的风险相对而言大一些。(如下图二)

图二(引用自《JEP157》标准)

季丰电子

季丰电子成立于2008年,是一家聚焦半导体领域,深耕集成电路检测相关的软硬件研发及技术服务的赋能型平台科技公司。公司业务分为四大板块,分别为基础实验室、软硬件开发、测试封装和仪器设备,可为芯片设计、晶圆制造、封装测试、材料装备等半导体产业链和新能源领域公司提供一站式的检测分析解决方案。

季丰电子通过国家级专精特新“小巨人”、国家高新技术企业、上海市“科技小巨人”、上海市企业技术中心、研发机构、公共服务平台等企业资质认定,通过了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ANSI/ESD S20.20等认证。公司员工近1000人,总部位于上海,在浙江、北京、深圳、成都等地设有分公司。

-

ESD测试的详细解释2025-11-26 509

-

AEC-Q102之静电放电测试(HBM)2024-12-25 1721

-

芯片的HBM静电都有哪些测试标准,各标准之间有没有差异2024-11-27 7367

-

什么是AEC-Q-CDM测试?2024-11-01 1674

-

季丰电子CDM测试机已全部配备高带宽的6G示波器2023-08-12 1865

-

浅谈CDM的原因与机理2023-05-16 19823

-

HBM静电测试机尾波的危害2022-11-30 3828

-

同样都HBM,芯片级(component level)和系统级(system level)的差别在哪里?2022-09-19 9896

-

HBM、MM和CDM测试的基础知识2022-07-24 35533

-

半导体测试HBM了解一下~2020-10-16 9978

-

芯片IC可靠性测试、静电测试、失效分析2020-04-26 5577

-

什么是小尺寸集成电路CDM测试?2019-08-07 5391

全部0条评论

快来发表一下你的评论吧 !