二维材料模块的自组装实现,获得高质量半导体薄膜

制造/封装

536人已加入

描述

在原子尺度上精确设计具有垂直结构的高性能半导体薄膜可用以现代集成电路和新型材料的研究。获得这种薄膜的一种方法是实现连续的层层自组装,即利用二维构建材料在垂直方向上堆叠,并依靠范德华力连接。石墨烯以及过渡金属二硫化物这些只有1和3原子厚的二维材料就被用于实现一些早先制备较为困难的异质结,并表现出较为优异的物理特性。然而,还没有既能保持二维材料构建本征特性又能产生夹层界面的大规模自组装的方法存在,这限制了层层自组装方法相一个小尺度规模化制备的转变。

康奈尔大学Jiwoong Park(通讯作者)等人报道了实现高水平空间均匀性和本征夹层界面生产晶圆级尺度的半导体薄膜的方法。相关研究论文以题为“Layer-by-layer assembly of two-dimensional materials into wafer-scale heterostructures”于2017年9月21日在线发表于Nature顶刊。薄膜的垂直方向组分通过二维材料模块在真空下原子尺度上的自组装实现。同时制备了一些大规模、高质量的异质结薄膜和设备,包括超晶格薄膜、批次生产的电阻可调的隧道结阵列、能带调控异质结隧道二极管以及毫米级超薄膜。堆叠形成的膜可拆卸、可中断并与水和塑料等界面相容,从而可实现与其他光学和机械系统集成。

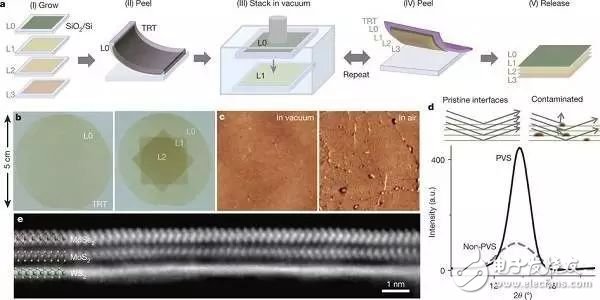

图1 利用层层自组装获得高质量半导体薄膜

图2 程序化真空堆叠(PVS)过程

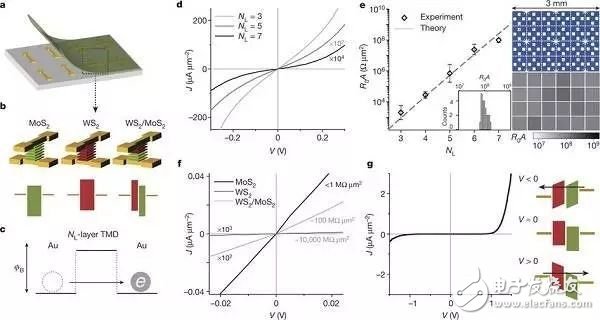

图3 利用层数或垂直组分来调控半导体薄膜的电导率

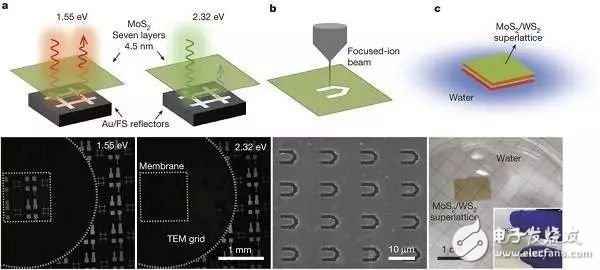

图4 应用于光学和机械领域可拆卸和自支撑的半导体薄膜

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

用于生长高质量二维半导体的重凝硫前驱体研究2024-01-13 1377

-

首次实现GHz频率的二维半导体环形振荡器电路2023-11-24 1707

-

12英寸二维半导体晶圆的批量制备完成2023-07-13 733

-

中国团队成功实现12英寸二维半导体晶圆批量制备技术2023-07-12 1252

-

我国突破12英寸二维半导体晶圆批量制备技术2023-07-10 2225

-

二维材料电致横向PN结及纵向异质结快速转移制备2023-02-15 2569

-

基于垂直架构的新型二维半导体/铁电多值存储器2022-11-28 1046

-

二维半导体晶体管实际沟道长度的极限2022-10-17 3973

-

科学家发现二维铁磁半导体中隧穿电导由磁化强度决定2021-12-16 1204

-

剖析二维电子器件的高k介电薄膜——氟化钙2021-04-20 5689

-

物理所成功制备单层MoS2晶圆,将推动二维半导体材料的研究发展进程2020-10-25 5745

-

二维材料家族包含了哪些材料?2020-06-05 14871

-

二维材料从新出发2020-01-27 3349

-

高质量二维原子晶石墨烯的制备及性能研究2017-10-27 835

全部0条评论

快来发表一下你的评论吧 !