上升沿触发器有哪些

电子常识

2680人已加入

描述

数字电路中,数字电平从低电平(数字“0”)变为高电平(数字“1”)的那一瞬间叫作上升沿。上升沿触发是当信号有上升沿时的开关动作,当电位由低变高而触发输出变化的就叫上升沿触发。也就是当测到的信号电位是从低到高也就是上升时就触发,叫做上升沿触发。

在Verilog HDL等硬件描述语言中,最常用的两种事件分为电平触发和边沿触发,其中边沿触发即包括上升沿触发、下降沿触发。上升沿触发的写法是在符号“@“之后加上”posedge 信号名”,其中“posedge”表示信号的上升沿。

上升沿触发的D触发器

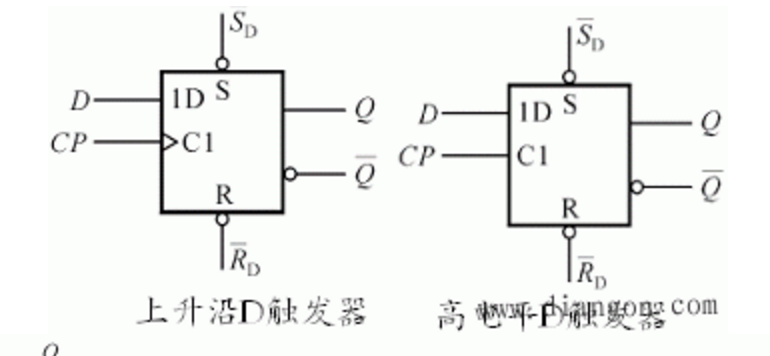

也叫正边沿触发,由六个与非门组成,能实现边沿触发的主要原因是有二条反馈线。

根据电路图作如下分析:

1)CP=0时,由于G3、G4门封锁,触发器状态不可能改变。

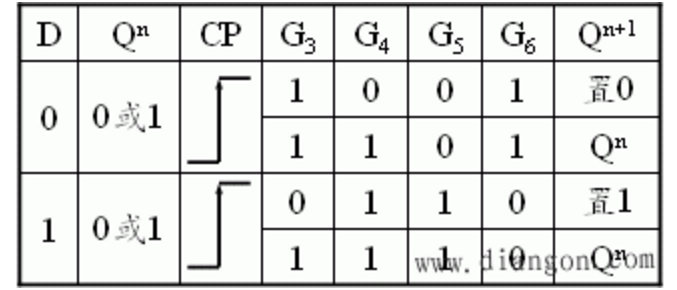

2)在CP=1期间、CP上升沿及CP下降沿时用表加以说明。

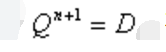

可见,触发器在CP脉冲作用后的次态与D信号相同,即:

。在CP=1期间,有维持和阻塞作用,使触发器接收信号和状态翻转稳定可靠。

上升沿触发的D触发器逻辑符号,请注意它与电平触发器的区别。

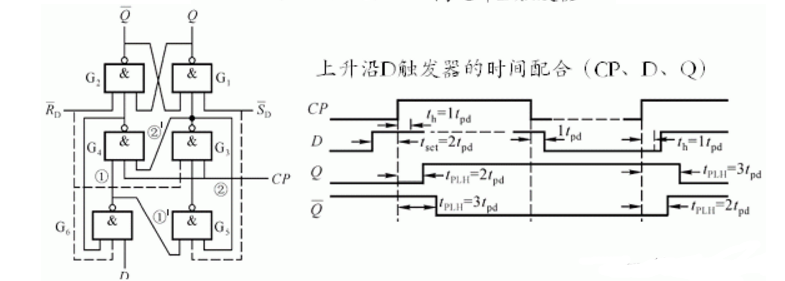

⑴ 输入信号建立时间tset。它表示D信号应比CP早到的时间,从图可见,该时间为:

。

。

⑵ 输入信号保持时间th。它表示CP上升沿到达后,D信号应保留的时间。由图可见,该时间为:

。

。

⑶ 触发器翻转时间tpLH或tpHL。从CP脉冲上升沿到达到Q端由低电平变为高电平之间时间:

,Q由高到低时间:

。

。

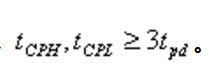

⑷ CP脉冲的高低电平时间tCPL,tCPH,

。

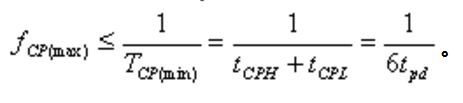

为此,CP脉冲的最高工作频率为:

。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 触发器

-

jk触发器有圈是上升沿还是下降沿2024-08-22 6106

-

jk触发器上升沿和下降沿怎么判断2024-07-23 6134

-

d触发器有几个稳态 触发器上升沿下降沿怎么判断2024-02-06 7828

-

jk触发器是上升沿还是下降沿触发2024-01-11 11710

-

rs触发器是上升沿还是下降沿 触发器如何确定是上升沿2023-09-12 11563

-

20位总线接口D型触发器;上升沿触发;三态-74ALVT168212023-02-23 466

-

低功耗双D型触发器;上升沿触发-74AUP2G802023-02-17 498

-

八路D型触发器;上升沿触发;三态-74ALVC3742023-02-16 491

-

具有置位和复位功能的双D型触发器;上升沿触发-74LVC74A2023-02-15 507

-

低功耗D型触发器;上升沿触发-74AUP1G792023-02-14 495

-

单D型触发器;上升沿触发-74LVC1G792023-02-09 515

-

低功耗D型触发器;上升沿触发-74AUP1G802023-02-07 591

全部0条评论

快来发表一下你的评论吧 !