滞回比较器的计算公式(阈值电压公式计算)

电子常识

描述

关于比较器滞回的讨论需要从“滞回”的定义开始, 与许多其它技术术语一样, “滞回”源于希腊语, 含义是“延迟”或“滞后”, 或阻碍前一状态的变化。工程中,常用滞回描述非对称。

绝大多数比较器中都设计带有滞回电路, 通常滞回电压为5mV到10mV。内部滞回电路可以避免由于输入端的寄生反馈所造成的比较器输出振荡。但是内部滞回电路虽然可以使比较器免于自激振荡, 却很容易被外部振幅较大的噪声淹没。这种情况下需要增加外部滞回, 以提高系统的抗干扰性能。

滞回比较器的计算公式

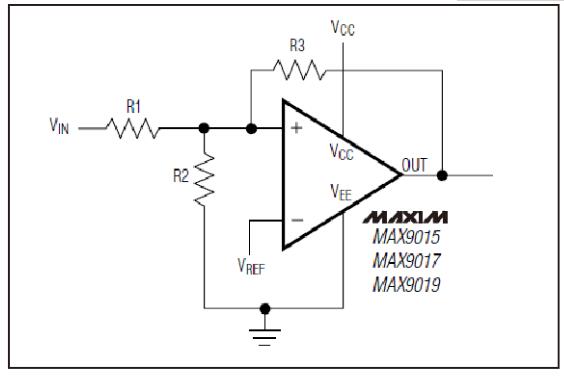

可调门限滞回比较器

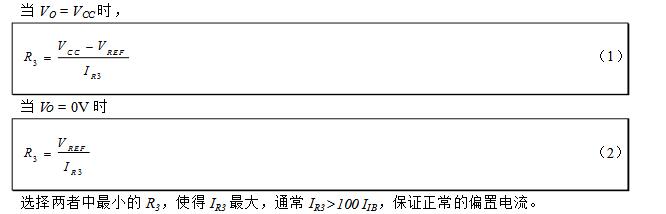

一、R3计算

当经过触发点R3的电流分两种情况: 当Vo = Vcc时,

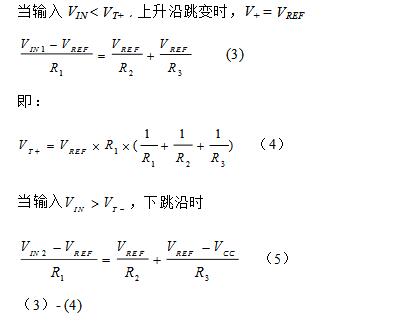

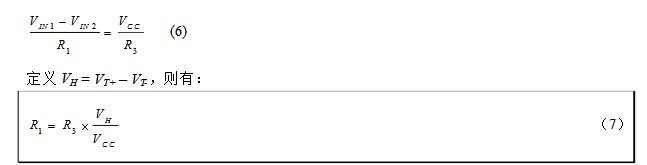

二、R1计算

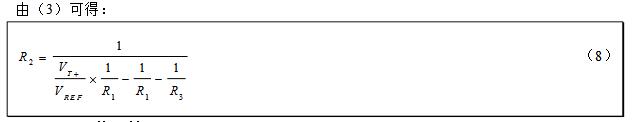

三、R2计算

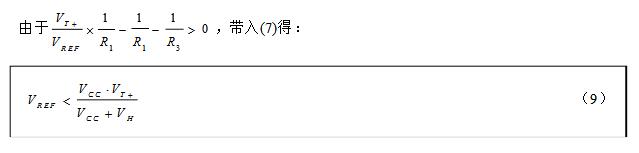

四、Vref取值限制

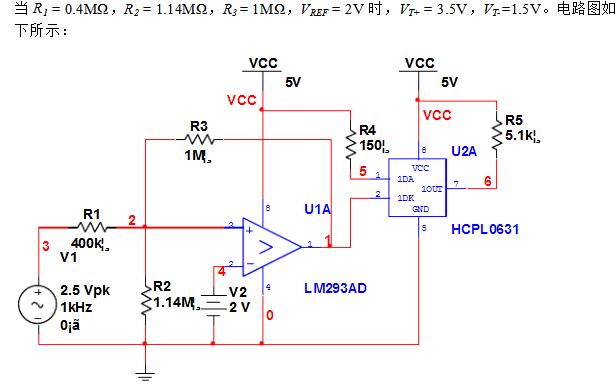

五、电路应用实例

阈值电压公式计算

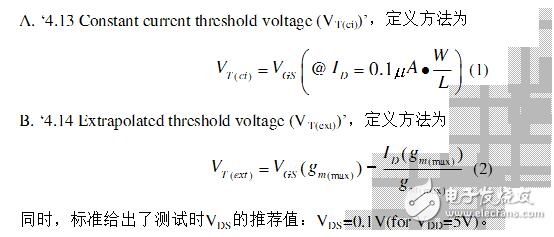

根据JEDEC STANDARD JESD-28的规定计算方法(JEDEC 14.2.2 –Hot Carrier Working Group --- June 15,1995),有两种计算阈值电压的方法:

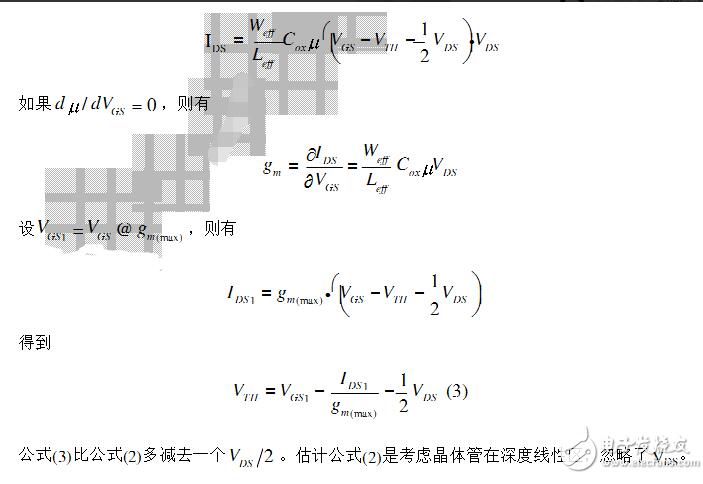

方法A易于操作,在早期的阈值电压测试中常用,随着工艺的先进,这种方法不够准确,方法B逐渐开始采用,但实际上JEDEC定义的不够准确,它是把VDS忽略掉了。正确的计算方法是,根据线性区的电流方程:

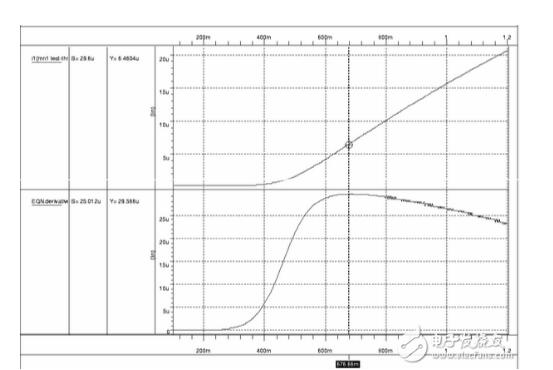

我用Hspice仿真的方法,用A、B两种方法计算了某0.18um工艺中NMOS的阈值电压,取VDS=0.1V。下面是计算结果:

1、W=1u, L=1u. 方法A:在波形图上测量到ID=0.1uA时,VGS=0.356V,那么VT(ci)=0.356V;ID=1uA时,VGS=0.467V 方法B.:在波形图上测量到gm(max)=29.6u,此时VGS约为0.675~0.679V,就取

2、W=10u, L=1u. 方法A:在波形图上测量到ID=1uA时,VGS=0.361V,那么VT(ci)=0.361V;ID=10uA时,VGS=0.471V; 方法B.:在波形图上测量到gm(max)=311.4u,此时VGS=0.683V,此时ID=68.11uA,代入公式(3),得到VT(ext)=0.414V。

同时用Hspice中的vth()输出,得到Vth=0.414V

三种计算方法得到的结果与上相同。

- 相关推荐

- 比较器

-

电缆的电压降怎么计算_电缆电压降计算公式2018-04-03 85404

-

液压计算常用公式与马达常用计算公式2022-12-27 4808

-

如果想改变反相滞回比较器的阈值电压应改变哪些参数呢?2023-03-24 0

-

功率的计算公式/电功率计算公式2008-08-13 132427

-

常用体积计算公式2010-07-17 589062

-

电流公式_齐全的电流计算公式2011-12-19 322708

-

电感的计算公式2016-05-06 2381

-

电容降压原理和计算公式2016-06-22 2145

-

迟滞比较器计算公式与回差计算2018-02-26 123053

-

滞回比较器计算公式2022-11-03 16291

-

电机扭矩的计算公式和转速计算公式2023-12-25 5112

-

迟滞比较器门限电压计算公式2023-12-28 4578

-

滞回比较器的阈值电压如何确定?2024-07-30 1556

-

滞回比较器的阈值电压是什么2024-07-30 1607

-

什么是滞回比较器,及滞回阈值参数计算2024-12-22 99

全部0条评论

快来发表一下你的评论吧 !