FPGA设计过程中定点小数计算要注意些什么

可编程逻辑

描述

在FPGA设计过程中难免会碰到需要进行截位,那定点小数的计算过程中我们需要注意些什么呢?

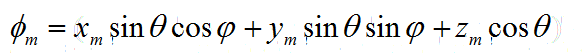

首先,我们考虑如下计算式。

sin cos 数据形式是 FIX_32_30

X Y Z 数据形式是 FIX_32_20

φ 是角度 最后需要计算 exp(jπφ),可以看出来φ具有周期性,是可以-1~+1。要求的数据形式是 FIX_32_29

1、首先 分析 temp = sin*cos 结果

两个FIX_32_30相乘得到的数据是 FIX_64_60,我们发现这个结果最大值为-1~+1,所以只需要保留两位整数位即可(其中一位为符号位)即通过截位使其变成FIX_32_30,所以 temp 为 sin*cos [61:20]。

2、接着分析 X*temp y*temp的结果

一个FIX_32_20乘以FIX_32_30结果为FIX_64_50。

在一般情况下sin*cos结果为-1~+1之间,也就是说相乘之后X Y数只会变小,最大为其本身。所以一般情况下通过截位使得结果为FIX_32_20,即保留12位整数位,20位小数位即可。

但我们观察到计算exp(jπφ)中,是存在周期性的φ的循环周期为-1~1,所以我们只需要截取成 FIX_32_31就可以(做了一个近似,类似exp(jπφ) = exp(-j0.9999999πφ)),以截取的部分为[50 : 19] ,结果为FIX_32_31

3、再分析Z*COS的结果

一个FIX_32_20乘以FIX_32_30结果为FIX_64_50,同样的将其截取成FIX_32_31即可。

4、其次三个之和的计算过程中,因为周期性,不需要扩展高位,计算结果为FIX_32_31。

5、最后FIX_32_31算术左移两位即可得到FIX_32_29。

总结:

1.定点小数计算过程中,需要注意小数点的位置。

2.不同小数点位置的数据是不能相加的。

3.可以通过数据计算本身的周期性质,进行截位可以保留更多的小数点位。

-

FPGA开发过程中配置全局时钟需要注意哪些问题2024-04-28 1527

-

定点小数运算2025-07-25 422

-

基于牛顿迭代法的FPGA定点小数计算2019-07-18 3268

-

有关FreeRTOS中信号量和计数信号量在使用过程中需要注意的细节2021-08-06 1871

-

ST的LL库在使用的过程中需要注意些什么地方?2023-10-09 458

-

定点小数的表示方法2009-10-13 8662

-

一文了解FPGA浮点小数与定点小数的换算及应用2018-06-28 8084

-

FPGA定点小数的常规格式、相对于浮点小数的优势与劣势和计算的概述2018-06-12 10203

-

轴承在维护过程中需要注意什么2021-09-14 1678

-

使用雷达液位计过程中的注意事项有哪些2022-01-17 1326

-

浮点与定点运算以及数据定标和精度问题2022-12-06 6516

-

LoRa模块的使用过程中要注意什么?2023-02-03 1730

-

电源适配器的包装和运输过程中需要注意哪些事项?2023-11-23 2510

-

PCBA加工过程中一定要注意的事项2023-12-20 1069

-

速度探头在使用过程中需要注意哪些问题呢2025-02-06 785

全部0条评论

快来发表一下你的评论吧 !