Xilinx支持Serial RapidIO Gen2核可应用在Rapid IO交换设计中

可编程逻辑

描述

Rapid IO协议由于无主机,且各设备之间可以并行交换信息,所以广泛应用于对交换速率要求高,且交互复杂的应用中。Xilinx现在有支持Serial RapidIO Gen2的核,可以应用在此场景中,但Xilinx 的 Rapid IO 核对外接口仅有 AXI 流接口 , 且对各类数据流的处理需要外部单独设计, 不能方便的对消息、 门铃、 数据进行读写传输。

1. Xilinx IP核配置

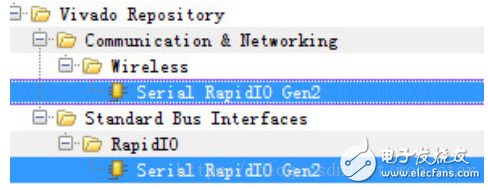

Rapid IO 物理层在 Vivado 的 IP 列表中可以找到。

在 block design 界面下, 找到 Rapid IO 物理层的核, 添加到 block design 设计中, 双击进行配置。

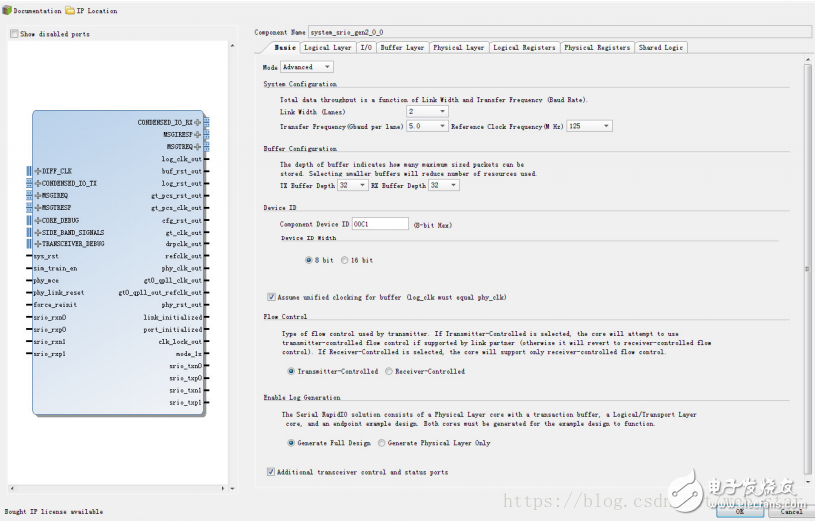

第一个配置界面中选择基本配置或者高级配置, 我们的设计均按照高级配置进行设置; 在系统配置选项, 选择 link width 位宽、 Gbaud速率、 ref_clk 频率; 在 Device ID 框中配置设备 ID; 因为核需要知道设备 ID, 选择附加控制和状态接口 , 其它设置默认。

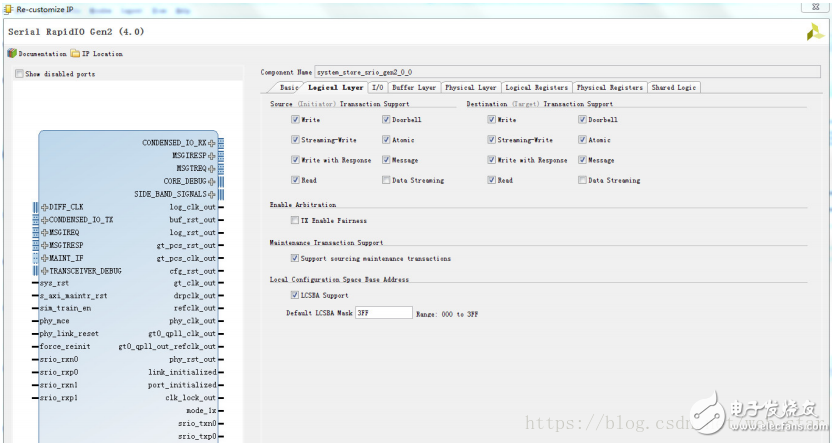

逻辑层设置页面, 选择支持维护, 其它按照默认设置即可。

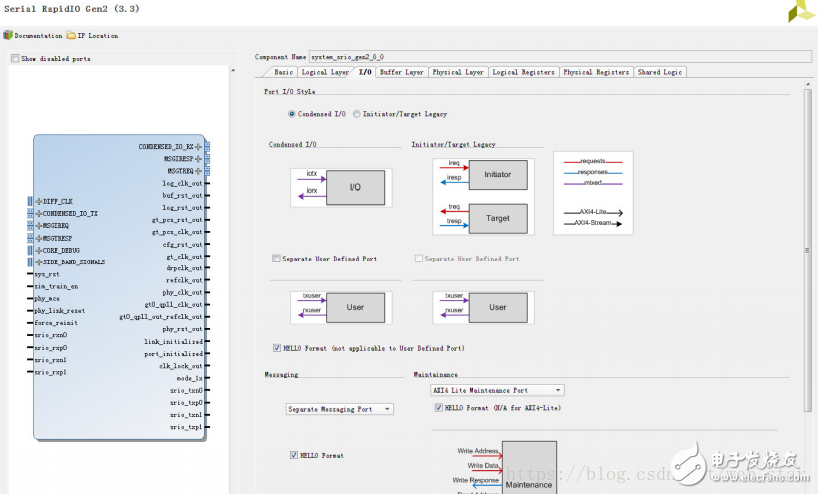

IO 设置页面, IO 端口设置为 Condensed I/O, Messaging 端口设置为 Separate Messaging port, 均选择 HELLO format。

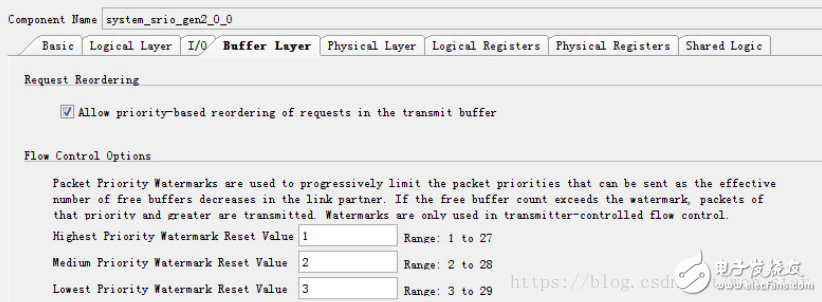

缓冲层页面按照默认设置即可。

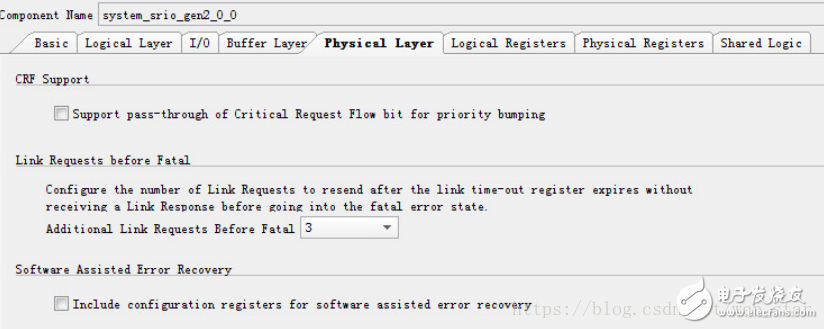

物理层页面按照默认设置即可。

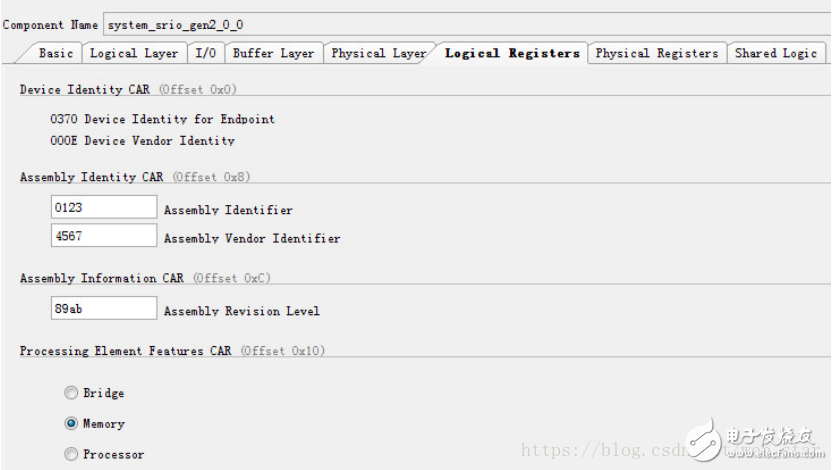

逻辑寄存器 页面 可以自定义 设置 Assembly CAR, Processing Element Feature CAR 选择 Memory 类型。

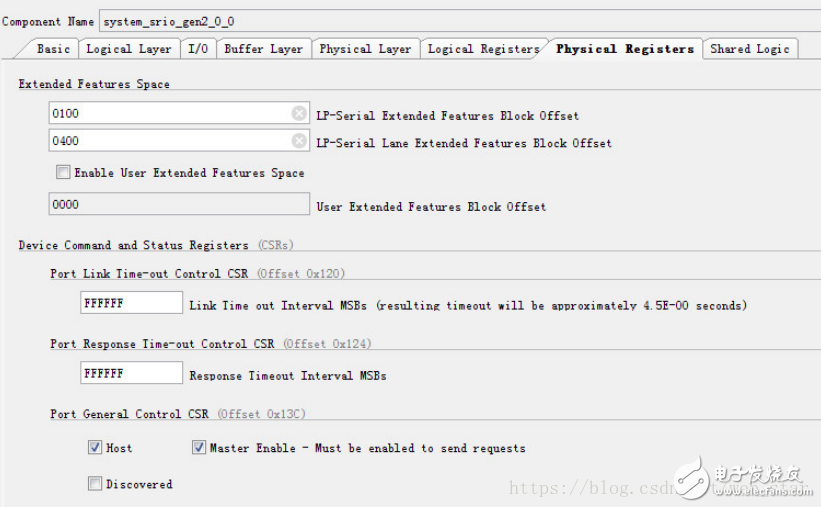

物理寄存器页面按照默认设置即可。

逻辑共享页面设置为在核内包含共享逻辑。

2. AXI转SRIO模块

本模块实现对Xilinx核的数据流信息进行处理, 并映射到CPU的寄存器, 用于以Rapid IO作为交换的高速数据传输应用。

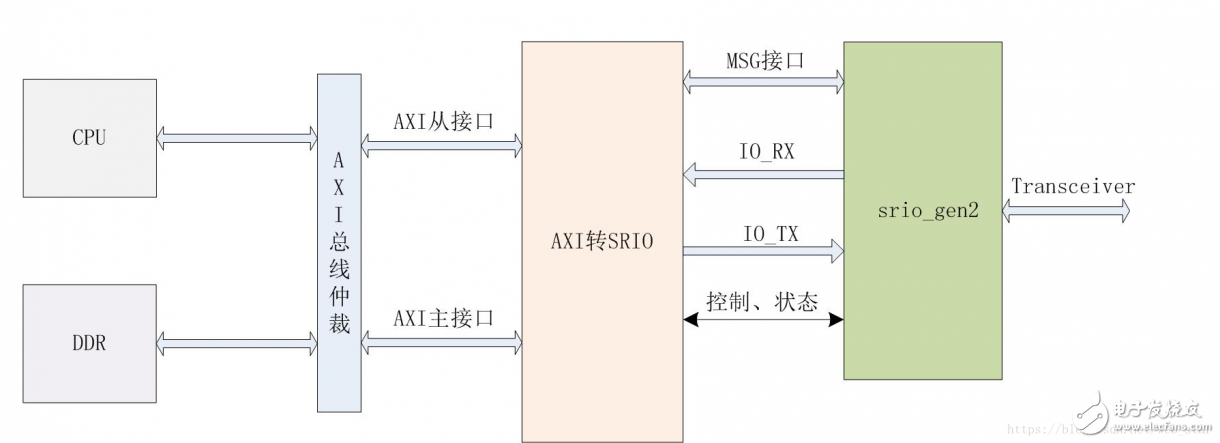

CPU通过AXI从接口接收和发送消息、门铃,大块数据传输,通过AXI主接口写入和读出DDR,然后通过IO_RX、IO_TX接口发往srio_gen2核。

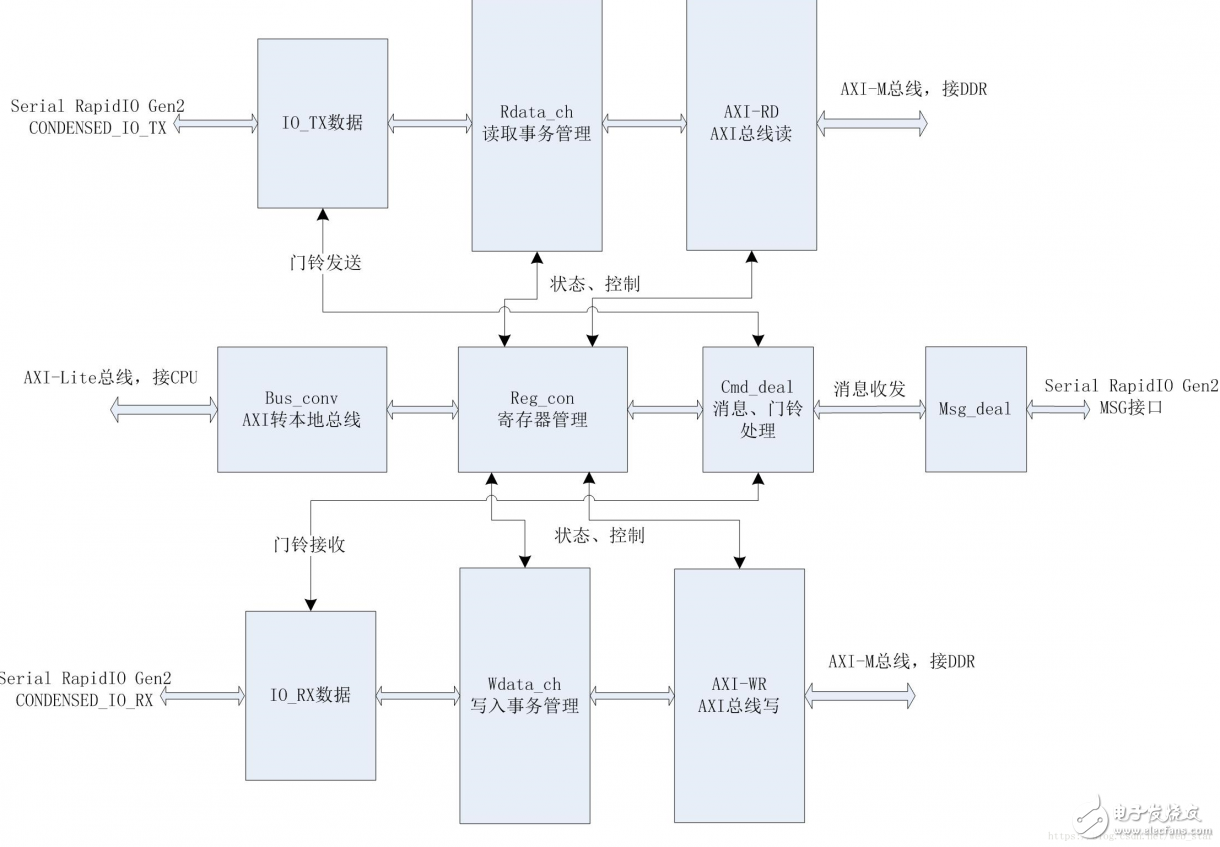

AXI转SRIO核内部构造如图所示。

IO_RX接口接收的大块数据,通过Wdata_ch写入事务管理器,再经过AXI-M总线,写入DDR缓存;需要发送出去的大块数据,通过AXI-M总线,从DDR缓存读出,经过Rdata_ch读事务管理器,发往IO_TX接口。

IO_RX和IO_TX的门铃,以及MSG的消息,传输到门铃、消息事务处理模块,然后送往CPU。

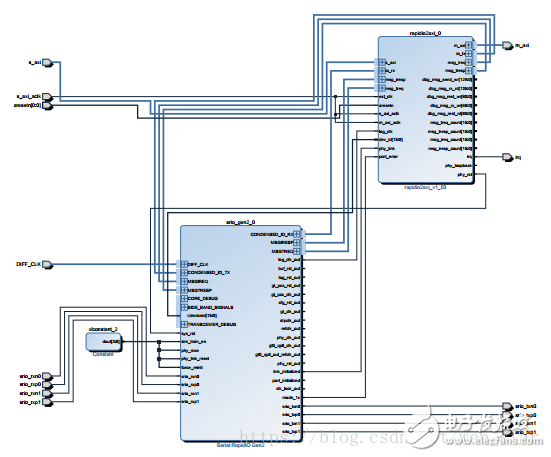

在Vivado工程设计中的连接图(清晰PDF版本 https://download.csdn.net/download/web_star/10310707)。

通过AXI转SRIO模块,大大简化了设计,且可以通过CPU发送消息、门铃,且可以发起和接收高速大量DMA数据。

-

IDT Serial RapidIO 交换机特性对比分析2026-04-14 89

-

IDT CPS - 1616:高性能 Serial RapidIO Gen 2 交换机解析2026-04-12 446

-

数字隔离器可应用在本质安全应用中2023-11-24 471

-

Serial RapidIO Gen2Development Platform(SRDP2) 快速入门指南2023-04-12 470

-

Serial RapidIO Gen2Development Platform(SRDP2) User 手册2023-04-10 499

-

可应用在电磁涡流场问题的等几何配点法2021-06-21 892

-

如何在SPARTAN 6 phy的GEN1和GEN2时钟生成之间切换2019-07-24 2850

-

Altera推出Serial RapidIO Gen2 IP,满足通信带宽需求2012-11-02 1919

-

全新Serial RapidIO Gen2交换器系列2010-06-28 2168

-

IDT推出Serial RapidIO Gen2系统建模工具2010-03-23 1374

-

IDT宣布推出PCI Express Gen2 系统互连交换2010-02-11 1174

全部0条评论

快来发表一下你的评论吧 !