FPGA的FIFO实现过程

可编程逻辑

描述

FIFO队列是一种数据缓冲器,用于数据的缓存。他是一种先入先出的存储器,即最先写入的数据,最先读。FIFO的参数有数据深度和数据宽度。数据宽度是指存储数据的宽度。深度是指存储器可以存储多少个数据。

FIFO队列有两个标志位。一个满和一个空标志位。分别表示FIFO是数据写满,还是数据读空。在数据写满状态下,数据写入是不允许的,因此在这个状态下,写入的数据无效。而数据读空状态下,数据读取是不允许的,因此在这个状态下,读取的数据无效。

FIFO队列有两个位置指示指针。一个是写指针,指向队列的第一个存储单元。一个读指针,指向队列的最后一个存储单元。当有写命令的时候,数据写入写指针指向的存储单元,然后指针加一。当有读命令的时候,读指针加一,在读出读指针指向的存储单元的数据。这里读命令,指针要加一,是定义读数据,是读出读指针的下一个存储单元的数据。

当写指针和读指针的指向存储单元一样时,这时候根据之前是读命令还是写命令来判断队列是空,还是满。在读命令,两个指针值一样时候,则队列空。在写命令,两个指针值一样,则队列满。

以后就开始写代码实现上诉FIFO队列,并进行仿真。

以下,是实现数据宽度为8.深度为2^4的深度的FIFO。。读/写时钟是同一个。

module fifo_cus

#(

parameter N = 8, //数据宽度

parameter M = 4 //fifo的地址宽度

)

//对队列的参数设置。建议这样写,便于以后代码的移植。

//如果以后要实现数据宽度为16,深度为2^8的FIFO。只需改N =16 M=8即可

(

input clk, //输入时钟

input rst_n, //输入复位信号

input wr, //输入写使能

input[N-1:0] w_data, //输入输入

input rd, //输入读使能

output empty, //输出fifo空标志

output full, //输出fifo满标志

output[N-1:0] r_data //输出读取的数据

);

//寄存器组,用来充当FIFO队列

reg [N-1:0] array_reg [2**M - 1:0];

//定义写指针,指示当前写的位置,下一个状态写的位置,写位置的下一个位置

reg [M-1:0] w_ptr_reg, w_ptr_next,w_ptr_succ;

//定义读指针,指示当前读的位置,下一个状态读的位置,读位置的下一个位置

reg [M-1:0] r_ptr_reg, r_ptr_next,r_ptr_succ;

//定义FIFO满和空的信号

reg full_reg, full_next;

reg empty_reg, empty_next;

wire wr_en;

//数据的写入,在数据的上升沿的时候,有写使能信号,将数据写入。而

always@( posedge clk ) begin

if( wr_en )

array_reg[w_ptr_reg] <= w_data;

else

array_reg[w_ptr_reg] <= array_reg[w_ptr_reg];

end

// 数据的读取。数据读取是一直在读取的,不过读取的是之前的值。

assign r_data = array_reg[r_ptr_reg];

assign wr_en = wr & ~full_reg;

/*状态跳转

在复位信号有效,读/写指针都指向0地址。此时队列状态为空。

在复位不有效,且在时钟的上升沿,读/写指针的值,队列空,满状态的值又下一状态决定。否则保持 */

always@( posedge clk ) begin

if( !rst_n )

begin

w_ptr_reg <= 0;

r_ptr_reg <= 0;

full_reg <= 1'b0;

empty_reg <= 1'b1;

end

else

begin

w_ptr_reg <= w_ptr_next;

r_ptr_reg <= r_ptr_next;

full_reg <= full_next;

empty_reg <= empty_next;

end

end

//下一个状态的判定

always@ * begin

w_ptr_next = w_ptr_reg;

r_ptr_next = r_ptr_reg;

full_next = full_reg;

empty_next = empty;

w_ptr_succ = w_ptr_reg + 1'b1;

r_ptr_succ = r_ptr_reg + 1'b1;

case( {wr,rd} )

/*读命令:在读命令下,如果队列不为空,讲当前读指针的下一个指针赋值给读指针的下一个状态,同时将队列的满标志置0。

然后判断读指针的下一个指针是否和写指针的值一样。一样的话,说明,队列为空。否则不为空。 */

2'b01:

begin

if( ~empty_reg )

begin

r_ptr_next = r_ptr_succ;

full_next = 0;

if( r_ptr_succ == w_ptr_reg )

empty_next = 1'b1;

else

empty_next = 1'b0;

end

end

/*写命令:在写命令下,如果队列不为满,将当前写指针的下一个指针赋值给读指针的下一个状态,同时将队列的空标志置0。

然后判断写指针的下一个指针是否和读指针的值一样。一样的话,说明,队列为满。否则不为满。

*/

2'b10:

begin

if( ~full_reg )

begin

w_ptr_next = w_ptr_succ;

empty_next= 0;

if( w_ptr_succ == r_ptr_reg )

full_next = 1'b1;

else

full_next = 1'b0;

end

end

/*读写命令:在读写命令下, 直接改变对应指针的下一个状态值。

*/

2'b11:

begin

w_ptr_next = w_ptr_succ;

r_ptr_next = r_ptr_succ;

endcase

end

// 满/空输出信号的赋值。

assign full = full_reg;

assign empty = empty_reg;

endmodule

好了,终于搞定FIFO的代码了。下面来仿真看看结果。

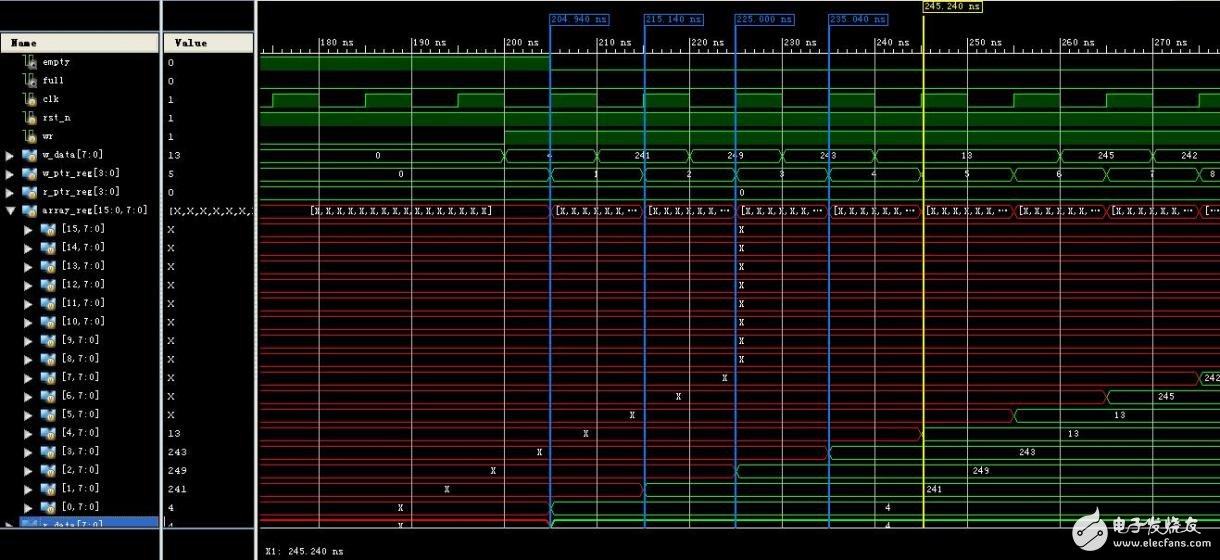

以下分析仿真的结果:

写数据:

从下图仿真,可看出。在最开始的时候,队列是空的状态。读指针和写指针都是0。在写使能情况下,在每个时钟的上升沿(蓝色线),数据写入队列array_reg中。同时,写指针加一。而读指针是不变的。

从下图发现,在队列满状态下,即使写使能,FIFO也不接受写数据。依旧保持原来的值。

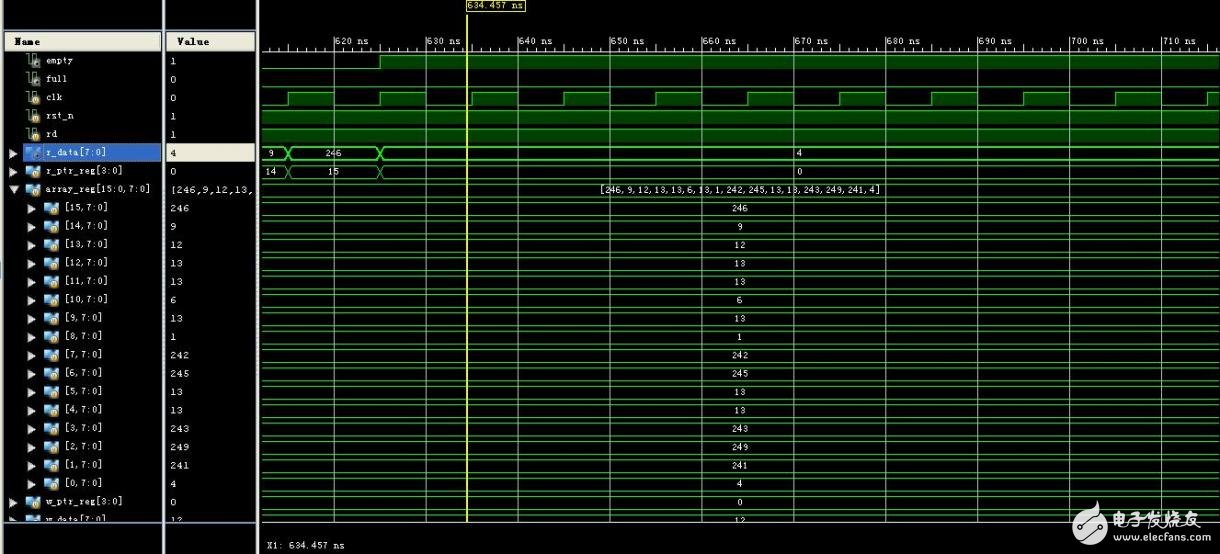

读数据

从下图中看出,最开始,数据读出是有值的。为初始化的读指针指向的存储单元的值。这里为4。

当有读命令时候,在时钟的上升沿(蓝色线),读指针加一。读取的数据随之改变。

在数据读完后,即队列为空状态下。此时对数据的读取是无效的。从图中可看出,读完后,读指针为0.回到存储器的第一个地址。而此时读出的值是无效的。

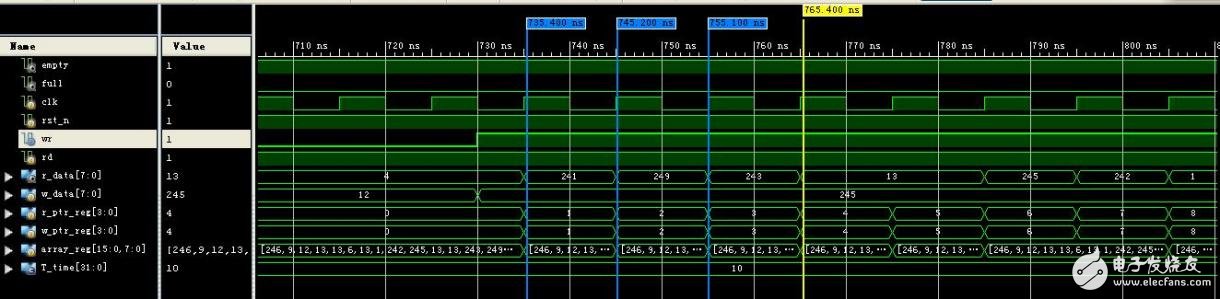

读写命令:

在同时读同时写的时候。从下图,可看出,结果有问题了。在队列为空的状态下,此时读取的值,应为此时写的数据才对了。但是从图中,可看出,读取的值不是当前写的数据的值。而是之前存储在FIFO中的值。这样的话,读取的值就不是正确的值了。

从上图仿真结果,可知。程序在读写命令时候,编写得不正确。造成结果不对。

返回程序分析。程序不对的地方在于读写命令的时候,处理 得不正确。在空的状态下,数据写入是先写入,然后写指针加一。而读取命令是,指针先加一,然后再读取。而读和写指针的值一样的。这样造成,读取的FIFO的存储单元的值,为写的存储单元的下一个存储单元的值。因此造成读取不正确。

改正的程序如下:

2'b11:

begin

if( ~full_reg && ~empty_reg )

begin

w_ptr_next = w_ptr_succ;

r_ptr_next = r_ptr_succ;

end

else if( full_reg ) //在满的状态,不允许写

begin

r_ptr_next = r_ptr_succ;

full_next = 0;

end

else if( empty_reg ) //在空的状态,不允许写

begin

w_ptr_next = w_ptr_succ;

empty_next = 0;

end

end

只需要规定以下:在满的状态,不允许写,在空的状态下,不允许读。这样就可以了。

然后再进行仿真:

这里只看读写命令的图。从下图中,可看出,此时读取的数据,为刚刚写的数据。这样就正确了。

这样,就完成了FPGA的FIFO了。通过这样一个简单的练习,可看出,仿真,是很重要的,能发现程序中的问题。

以上仿真没有覆盖到所有情况,有兴趣的,可以自己仿真看看仿真图,验证程序写得是否正确。

-

FPGA设计过程中常用的FIFO2022-09-20 3454

-

如何在Altera FPGA中使用FIFO实现功能设计?2021-03-12 4009

-

FPGA电路FIFO设计的源代码2020-07-08 972

-

在FPGA上实现自行FIFO设计的方法2018-11-28 8850

-

基于FPGA的异步FIFO的实现2018-06-21 7103

-

异步FIFO在FPGA与DSP通信中的应用解析2017-10-30 1675

-

异步FIFO在FPGA与DSP通信中的运用2011-12-12 907

-

LabVIEW FPGA模块实现FIFO深度设定2011-09-26 7963

-

基于VHDL和FPGA的非对称同步FIFO设计实现2011-01-13 2227

-

高速异步FIFO的设计与实现2010-01-13 613

-

基于PCI接口芯片外扩FIFO的FPGA实现2010-01-06 674

-

基于FPGA的FIFO设计和应用2009-11-20 2378

-

异步FIFO结构及FPGA设计2009-04-16 731

全部0条评论

快来发表一下你的评论吧 !