浅谈瑞盟科技·MS30517SA——单通道、高速、低侧栅极驱动器

电子说

描述

产品简述

MS30517SA 是单通道、高速、低侧栅极驱动器

器件,能够有效地驱动 MOSFET 和 IGBT 开关 。

芯片的设计能够大大减少击穿电流,MS30517SA

能够提供高峰值拉、灌电流脉冲,同时提供了轨到

轨驱动能力以及低传播延迟(典型值为 13ns)。

MS30517SA 能够承受 -5V 电压输入。

主要特点

◼低成本栅极驱动器器件,提供 NPN 和 PNP 离

散解决方案的高品质替代产品

◼4A 峰值拉电流和灌电流对称驱动

◼低传播延迟:13ns(典型值 )

◼快速上升和下降时间:9ns 和 7ns(典型值 )

◼TTL 和 CMOS 兼容逻辑阈值

(与电源电压无关)

◼双输入设计(选择一个反相(IN- 引脚)

或者同相(IN+ 引脚)驱动器配置)

◼工作温度范围:-40°C 至 125°C

◼SOT23-5 封装

应用

◼开关模式电源

◼直流到直流转换器

◼针对数字电源控制器的伴随栅极驱动器器件

◼太阳能、电机控制、不间断电源 (UPS)

◼宽带隙电源器件(例如 GaN)的栅极驱动器

产品规格分类

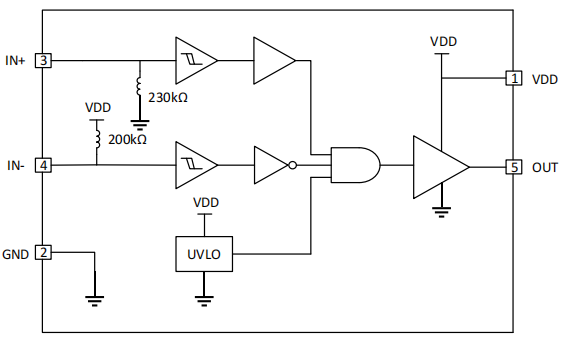

内部框图

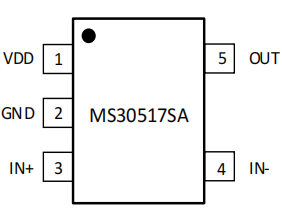

管脚图

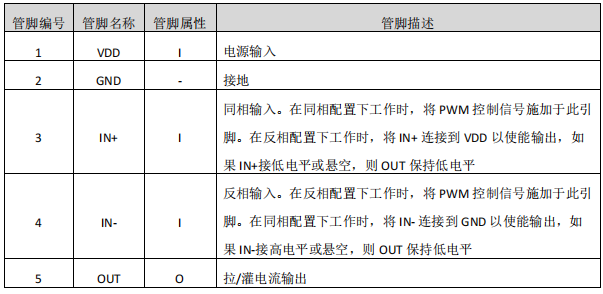

管脚说明

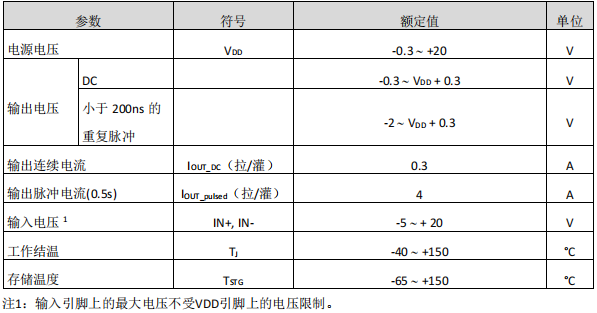

极限参数

芯片使用中,任何超过极限参数的应用方式会对器件造成永久的损坏,芯片长时间处于极限工作

状态可能会影响器件的可靠性。极限参数只是由一系列极端测试得出,并不代表芯片可以正常工作在

此极限条件下。

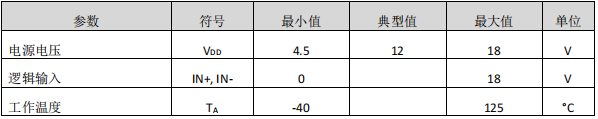

推荐工作条件

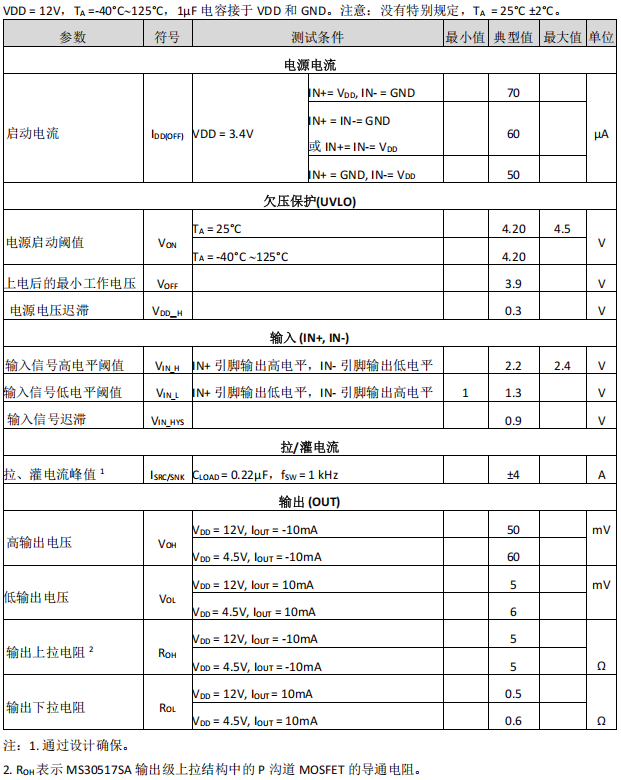

电气参数

如有需求请联系——三亚微科技 王子文(16620966594)

功能描述

概述

MS30517SA 是单通道、高速、低侧栅极驱动器器件,能够有效地驱动 MOSFET 和 IGBT 开关。 芯

片的设计能够大大减少击穿电流,MS30517SA 能够提供高峰值拉、灌电流脉冲,同时提供了轨到轨驱

动能力以及低传播延迟(典型值为 13ns)。

MS30517SA 可提供峰值为 4A 的拉/灌(对称驱动)电流驱动能力,可以在 4.5V 至 18V 的电源电压

范围以及 -40°C 至 125°C 的温度范围内运行。 VDD 引脚上的内部欠压锁定 (UVLO) 电路可在 VDD 低于欠

压阈值时,使输出保持低电平。 此器件能够在低电压(例如低于 5V)下运行,并且拥有同类产品中最

佳的开关特性,因此非常适用于驱动诸如 GaN 功率半导体器件等宽带隙电源开关器件。

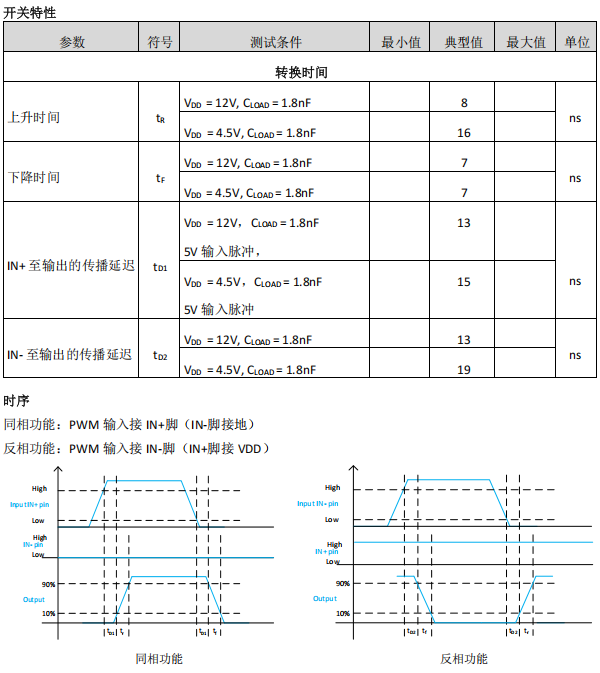

MS30517SA 采用双输入设计,可以灵活地用同一器件实现反相(IN-引脚)和同相(IN+引脚)配

置。IN+或 IN- 引脚用于控制驱动器输出的状态。未使用的输入引脚用于使能和禁用功能。出于保护目

的,当输入引脚处于悬空状态时,输入引脚上的内部上拉和下拉电阻确保输出保持低电平。因此,未

使用的输入引脚不能悬空,必须进行适当偏置,以确保驱动器输出使能正常工作。

MS30517SA 的输入引脚阈值基于 TTL 和 CMOS 兼容低压逻辑。该逻辑是固定的,与 VDD 电源电压

无关。高低阈值之间的宽迟滞特性提供出色的抗扰度。

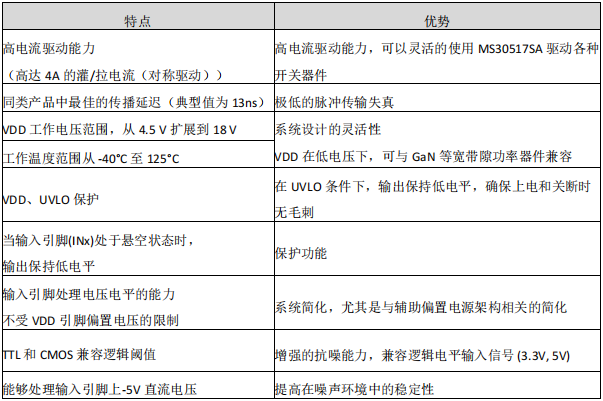

MS30517SA 的特点和优势

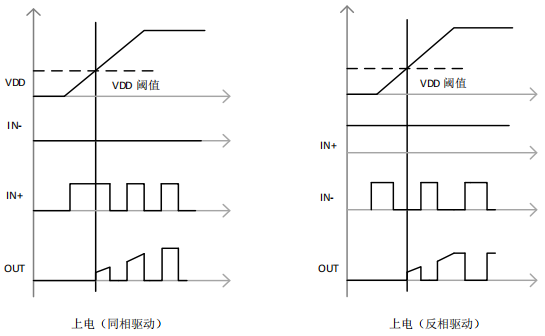

VDD 和 UVLO

MS30517SA 具有内部欠压闭锁(UVLO)保护功能。当驱动器处于 UVLO 状态时,无论输入状态如

何,该电路都会保持所有输出为低电平。此器件能够在低电压(例如低于 5V)下运行,并且拥有同类

产品中最佳的开关特性,因此非常适用于驱动诸如 GaN 功率半导体器件等宽带隙电源开关器件。

由于驱动器从 VDD 引脚汲取电流来偏置所有内部电路,为了实现最佳高速电路性能,建议使用两

个 VDD旁路电容来防止噪声问题。建议使用表面贴装元件。一个 4.7μF 陶瓷电容应尽可能靠近

MS30517SA 的 VDD 至 GND 引脚。此外,ESR 相对较低的电容(如 1μF)与之并联并靠近连接,以帮助

提供负载所需的高电流峰值,达到预期电流水平和开关频率,电容的并联组合应呈现低阻抗特性。

工作电源电流

MS30517SA 具有极低的静态 IDD电流。典型工作电源电流是指在欠压闭锁(UVLO)状态和全开状态

(静态和开关条件下)下的 IDD电流。器件完全开启且输出处于静态时的 IDD电流,表示当器件的所

有内部逻辑电路完全工作时的最低静态 IDD电流。总电源电流是静态 IDD电流、开关引起的平均 IOUT

电流以及与未使用的输入引脚上的上拉电阻相关的任何电流之和。例如,当反相输入引脚被拉低时,通

过上拉电阻从 VDD 电源汲取额外电流(参见内部框图)。已知工作频率(fSW)和所用驱动电压下的

MOSFET 栅极(QG)电荷,平均 IOUT电流可以计算为 QG和 fSW的乘积。

输入级

MS30517SA 的输入引脚基于 TTL 和 CMOS 兼容的输入阈值逻辑,独立于 VDD 电源电压,该逻辑电

平阈值的设置可以同时兼容 3.3V 和 5V。与传统 TTL 逻辑方案相比,更宽的迟滞可提供更强的抗扰度。

MS30517SA 具有重要的保护功能,只要任何输入引脚处于悬空状态,相应通道的输出就会保持在

低电平状态。这是通过在所有反相输入(IN-引脚)上使用 VDD 上拉电阻或在所有同相输入引脚(IN+

引脚)上使用 GND 下拉电阻来实现的。

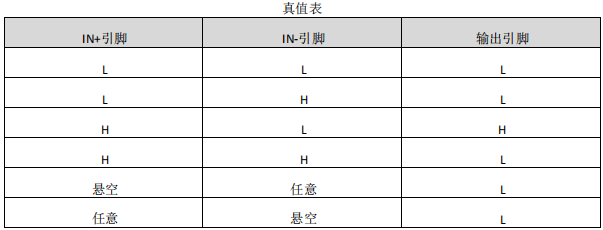

MS30517SA 还具有双路输入配置,两个输入引脚可用于控制输出状态。输出引脚的状态取决于

IN+和 IN-引脚上的偏置。参考真值表和典型的应用图。

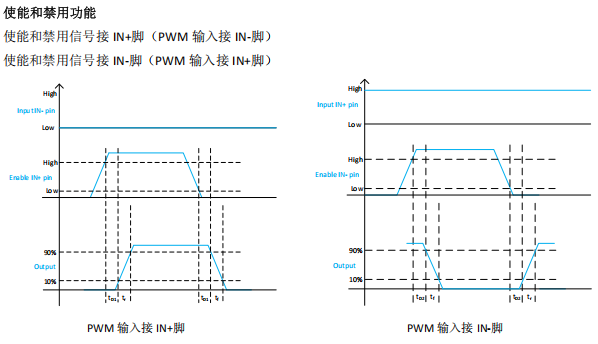

一旦为 PWM 驱动选择了一个输入引脚,另一个输入引脚(未使用的输入引脚)必须适当偏置以

使能输出。如前所述,未使用的输入引脚不能保持悬空状态,因为只要有任何输入引脚处于悬空状

态,输出就会出于保护目的而被禁用。或者未使用的输入引脚可以有效地用于使能/禁用功能。

使能功能

利用未使用的输入引脚,MS30517SA 可以实现使能或禁用功能。当 IN+被拉低至 GND 或 IN–被拉

高至 VDD 时,输出被禁用。因此,IN+引脚接高电平可使能逻辑引脚,而 IN–引脚接低电平可使能逻辑

引脚。

输出级

当 VDD 为 12 V 时,MS30517SA 提供峰值为 4A 的拉/灌(对称驱动)电流驱动能力。MS30517SA

输出级采用混合上拉结构,利用 N 沟道和 P 沟道 MOSFET 器件并联排列。当输出从低电平变为高电平

时,MS30517SA 在很短的时间内开启 N 沟道 MOSFET,从而短暂提升峰值电流,实现快速开启。

低传播延迟

当 VDD 为 12V 时,MS30517SA 具有同类最佳的 13ns(典型值)输入至输出传播延迟。在高频开

关应用中,这是业界标准栅极驱动器器件中的最低脉冲传输失真水平。

功能模式

在正常模式下,输出状态取决于 IN+和 IN-引脚的状态。不同输入引脚组合的输出状态如下:

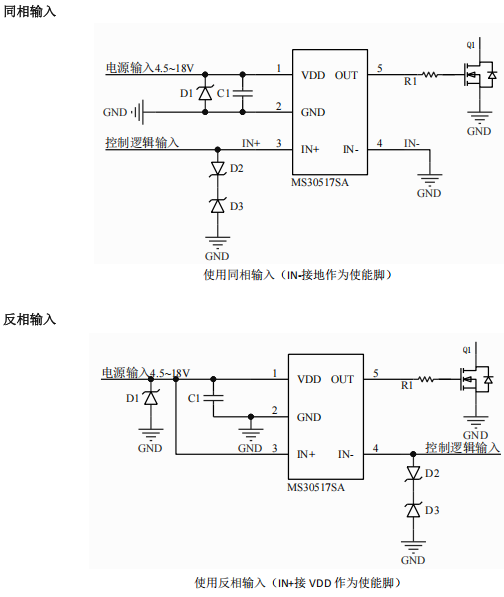

典型应用图

MS30517SA 的工作电源电压为 4.5V 到 18V。在应用中,应在电源 VDD 端并联一个 ESD 静电放电

器件 D1,该器件的钳位电压为 18V 到 24V。为防止干扰,电源 VDD 端应接旁路电容 C1,该电容需靠

近 VDD 引脚,推荐陶瓷电容,电容值 4.7μF(电容值不低于 2.2μF)。

控制逻辑输入端并联 ESD 静电放电器件,D2 钳位电压应小于 6V,D3 钳位电压应大于控制输入电

压,小于或等于 18V(VIN

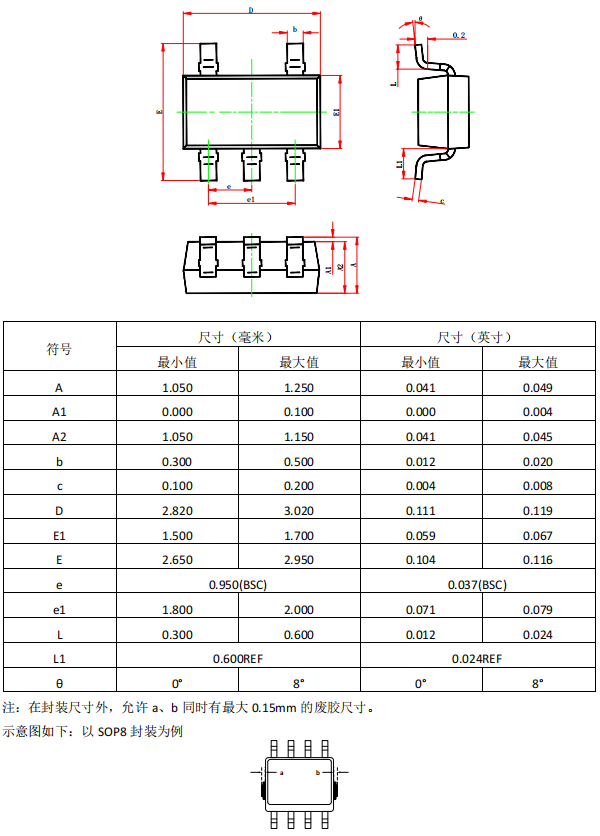

封装外形图

SOT23-5

——爱研究芯片的小王

审核编辑 黄宇

- 相关推荐

- 热点推荐

- 栅极驱动器

-

SGM48536/37/38/39/40:高性能单通道高速低侧栅极驱动器2026-03-26 390

-

深入剖析UCC27518和UCC27519单通道高速低侧栅极驱动器2026-01-11 905

-

深入解析UCC2751xA-Q1:高性能单通道高速低侧栅极驱动器2026-01-09 333

-

UCC27511A单通道高速低侧栅极驱动器:特性、应用与设计要点2026-01-08 337

-

深度剖析UCC27614:高性能单通道低侧栅极驱动器2026-01-07 657

-

单通道、高速、低侧栅极驱动器UCC2751x数据表2024-04-01 608

全部0条评论

快来发表一下你的评论吧 !