异步FIFO在DSP图像采集系统中的应用

处理器/DSP

描述

基于DSP的图像采集与处理系统与传统的PC端的系统相比,具有功耗低、携带方便、处理速度快的特点,被广泛使用在图像采集与处理领域。DSP(Digital Signal Process or)芯片也称数字信号处理器,是TI公司推出的专用于数字信号处理系统中进行算法处理的微处理器器件。DSP采用哈佛结构总线设计,程序存储器和数据存储器分开,取值和数据访问可以同时进行。DSP还使用流水线操作,使得多条指令重叠进行操作,可以有效地提高指令执行效率。此外,DSP还拥有独立的硬件乘法器,在处理滤波、卷积等运算时具有很快的速度,因此,DSP特别适合在图像采集与处理系统中作为核心器件。视频采集端的视频解码芯片使用TVP5150,将采集到的模拟图像信号转换成数字图像信号。

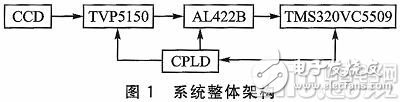

1 系统设计整体架构

本系统是基于DSP的数字图像处理系统,总体结构设计如图1所示。首先CCD摄像机拍摄视频图像,输出标准PAL制式视频信号,输入到视频解码芯片TVP5150中,TVP5150将模拟图像信号转换为数字图像信号送入FIFO中,本系统采用AL422B。DSP通过EMIF接口从FIFO中读取图像数据并存入存储器,图像数据经过DSP中算法处理后,通过仿真器传输到PC机上进行显示。其中,CPLD负责FIFO的读写指针复位和读写使能控制等工作。

(First In First Out)是一种先进先出的数据缓存器。FIFO与其他存储器的区别是没有读写地址线,操作可以变得很简单,而且,它只能将数据顺序写入,并且顺序读出。此外,FIFO还具有以下一些特点:

①对连续的数据进行缓存,防止数据的丢失。

②可以对数据进行集中存储,使CPU总线避免频繁的操作。

③允许系统进行高速的DMA操作,即可以不通过CPU的干预,直接进行数据存储,节约了使用CPU的时间,使系统的效率大大提高。

FIFO分为同步FIFO和异步FIFO。同步FIFO是指读写时钟必须是同一个时钟,而异步FIFO可以接受一种时钟写入数据,另一种时钟读出数据,也就是读写时钟可以不一致,能够相互独立。

由于本系统中TVP5150送数据到DSP时,TVP5150的写时钟和DSP的读时钟是不一样的。TVP5150的输出时钟是27 MHz,数据位为8位宽度,那么每秒的数据量就是216 Mbps,而DSP的输出时钟很难匹配27 MHz的时钟频率,设置为33 MHz,8位数据宽度,那么最大传输速率为264 Mbps。显然,两者的数据传输量在单位时间内是不一样的,如果这时不经过任何缓存就进行数据间的相互传输,系统无法同步操作,并且会进入一种亚稳定状态,从而整个系统功能失常。为了避免亚稳定状态以实现系统数据的高速稳定的传输,本系统使用了异步FIFO作为解决方案,且采用AL422B作为异步FIFO存储器,容量为3MB(393 216字节×8位),可以存储PAL制式一帧图形的信息。它的一些技术指标如下:

①支持VGA、CCIR、NTSC、PAL和HDTV制式的视频信号;

②独立的读写操作,可以接受不同的I/O速率;

③读或写周期为20 ns;

④访问时间为15 ns;

⑤输出使能控制;

⑥具有DRAM自刷新功能;

⑦3.3 V或5.0 V供电。

AL422B的读写过程分为4个步骤:写复位,写使能,读复位,读使能。首先复位写指针 ,当写使能

,当写使能 为低电平时,在WCK的上升沿将数据写入到写数据寄存器;当

为低电平时,在WCK的上升沿将数据写入到写数据寄存器;当

为高电平时,写操作被禁止。然后复位读指针 ,当

,当 都变为低时,在RCK的上升沿将数据写入读数据寄存器;反之,读操作被禁止。

都变为低时,在RCK的上升沿将数据写入读数据寄存器;反之,读操作被禁止。

2 系统硬件设计

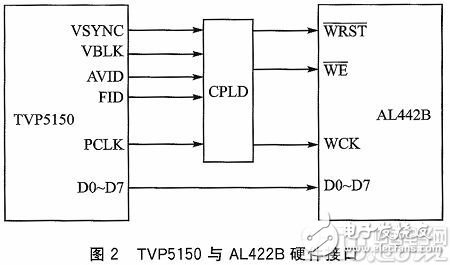

2.1 TVP5150与AL422B的接口实现

在本系统中,TVP5150的数据输出端要与AL422B的数据写入端相连,AL422B的数据读出端要与DSP的数据输入端相连。首先介绍TVP5150与AL422B之间的硬件连接,TVP5150的数据总线可以与AL422B的写入端的数据总线直接进行连接。

TVP5150的输出时钟需要进行二分频并移相半个时钟周期,然后与AL422B的写时钟WCK连接,因为我们只需要获取灰度图像,这样做可以将彩色部分的图像滤除并且可以减少数据量。

TVP5150端的VSYNC、VBLK、AVID、FID借助CPLD进行逻辑组合后与AL422B的写指针复位WRST和写使能WE连接。具体逻辑组合将在软件设计部分介绍。

TVP5150与AL422B接口如图2所示。

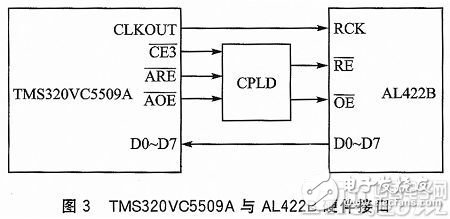

2.2 TMS320VC5509A与AL422B的接口实现

TMS320VC5509A(以下简称5509A)要接收来自AL422B中的数据,需要将AL422B的读数据总线与5509A的EMIF数据总线接口直接连接。5509A的输出时钟CLKOUT给AL422B提供读时钟。AL422B的输出使能 和读使能

和读使能 需要借助CPLD将5509A端的外部存储器片选信号

需要借助CPLD将5509A端的外部存储器片选信号 、EMIF接口输出使能

、EMIF接口输出使能 和EMIF接口读使能

和EMIF接口读使能 进行逻辑组合后进行连接。组合逻辑部分在软件设计部分介绍。TMS320VC5509A与AL422B接口如图3所示。

进行逻辑组合后进行连接。组合逻辑部分在软件设计部分介绍。TMS320VC5509A与AL422B接口如图3所示。

3 系统软件设计

软件部分分为两部分,分别是DSP内的程序设计和CPLD中的组合逻辑。

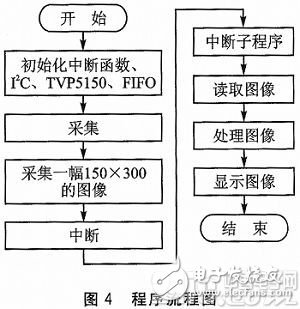

3. 1 DSP主程序

程序流程图如图4所示。

3.1.1 主函数初始化

主函数需要对时钟频率、中断函数、EMIF外部存储器接口、I2C总线、TVP5150视频配置、AL422B的写指针复位进行初始化。

其中,AL422B的初始化采用TMS320VC5509A的GPIO口GPIO0、GPIO1、GPIO2发送逻辑电平到CPLD,然后由CPLD发送命令控制AL422B的读写指针复位与读写使能。

在DSP中,首先定义GPIO口的方向控制寄存器IODIR和引脚电平寄存器IODATA,并将IODIR寄存器的低3位设为1,也就是将GPIO0、GPIO1、GPIO2的方向设为输出。接着对IODA TA寄存器进行赋值,并将寄存器的值通过GPIO口送到CPLD,CPLD端进行逻辑组合,对AL422B的复位写指针 复位。

复位。

3.1.2 初始化TVP5150

TVP5150是视频解码芯片,要求其模拟输入是PAL制信号,转换为8位的YUV4:2:2格式的数字输出信号。DSP需要通过GPIO口对TVP5150进行复位,方法类似于AL422B的写指针复位控制。DSP还需要通过I2C总线控制TVP5150的寄存器,TVP5150寄存器的配置如下:

①杂项控制寄存器:地址0x03,设置为0x0f。

②输出和数据比率选择寄存器:地址0x0d,设置为0x40。

③配置复用引脚寄存器:地址0x0f,设置为0x0a。

④有效像素开始高位寄存器:地址0x11,设置为0x4d。

⑤有效像素开始低位寄存器:地址0x12,设置为0x02。

⑥有效像素结束低位寄存器:地址0x13,设置为0xe4。

⑦有效像素结束低位寄存器:地址0x14,设置为0x02。

经过寄存器配置,使得场消隐信号VBLK、像素有效信号AVID、场同步信号VSYNC、奇偶场标志位信号FID、输出时钟SCLK输出有效,数据总线激活,并将采集到的图像裁剪成150×300的图像。

在初始化程序后,执行while死循环,等待中断的到来。

3.1.3 中断函数

由于只需要处理150×300的图像,所以在FIFO里只需存储150×300个像素点,存满后发出中断信号,DSP转去执行中断服务程序。中断函数首先通过GPIO口告知CPLD使AL422 B的读指针复位(方法类似AL422B的写指针复位,这里不再赘述),并且使AL422B的输出使能 有效、读使能

有效、读使能 有效(具体实现在3.2说明)。然后DSP便读取FIFO中的数据,因为FIFO外扩在DSP的

有效(具体实现在3.2说明)。然后DSP便读取FIFO中的数据,因为FIFO外扩在DSP的 这个空间,地址为0x600000,所以DSP将

这个空间,地址为0x600000,所以DSP将 中的数据写入内存中,存入内存中的数据供后续处理。

中的数据写入内存中,存入内存中的数据供后续处理。

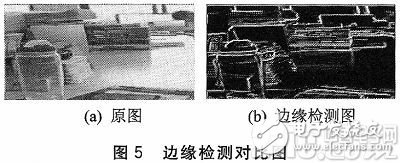

这里,我们使用的处理算法为图像的边缘检测法,处理完成后在CCS中进行显示,并观察算法处理结果。

最后,进行写指针复位,准备下一次的图像采集。需要注意的是,由于图像在传输过程中奇偶场是分开传输的,FIFO中只存储奇场的一部分图像,而完整的图像是由奇场和偶场共同组成的,所以获得的图像显示的是一帧图像压缩一半的结果,图像是失真的。但是,我们只观察算法的处理结果,因此没有进行图像的完整显示。

3.2 CPLD程序

CPLD接收的输入信号有来自TMS320VC5509A的GPIO口的信号,来自TVP5150的场消隐信号VBLK、像素有效信号AVID、场同步信号VSYNC和奇偶场标志位信号FID。CPLD的输出信号有提供给FIFO的写使能信号 ,写复位指针信号

,写复位指针信号 和读复位指针信号

和读复位指针信号 ,以及提供给TMS320VC5509A的中断信号

,以及提供给TMS320VC5509A的中断信号 。

。

当VSYNC由高电平变为低电平时,输出的是有效视频信号,同时当VBLK为低电平、AVID为高电平时,TVP5150输出有效视频数据。

因为偶数场是从一行的中间开始扫描的,如果不设置FID信号,最后采集到的图像可能是偶场信号,也可能是奇场信号,那么,在CCS中显示的图像有可能是完整的,也可能显示的是左右颠倒的图像,刚好错开半行的图像。所以,设置FID信号为0,采集奇场的信号。

CPLD将这些逻辑进行组合,使AL422B的写使能 有效,TVP5150输出视频数据到AL422B中。

有效,TVP5150输出视频数据到AL422B中。

因为要采集一幅150x 300的图像,需要在CPLD中设置一个计数器对采集到的像素进行计数,由AL422B的写时钟WCK作为计数器的时钟信号,当计数到45 000后触发DSP外部中断2,同时将计数器清零。

AL422B外扩在DSP的 这个空间,当

这个空间,当 和TMS320VC5509A的EMIF接口输出使能信号

和TMS320VC5509A的EMIF接口输出使能信号 且为低电平时,通过CPLD的逻辑组合使能AL422B的输出使能信号

且为低电平时,通过CPLD的逻辑组合使能AL422B的输出使能信号 。接着当TMS32 0VC5509A的EMIF接口读使能信号

。接着当TMS32 0VC5509A的EMIF接口读使能信号 为低电平时,通过CPLD的逻辑组合使能AL422B的读使能信号

为低电平时,通过CPLD的逻辑组合使能AL422B的读使能信号 。逻辑关系如下:

。逻辑关系如下:

4 实验结果

利用设计的系统进行实物图像的采集,图5(a)为采集的实验室的办公座椅场景,图5(b)为使用边缘检测算法来对采集到的图像进行的边缘处理。

边缘检测能够突出图像的边缘特征,使观察者一目了然,并且蕴含了丰富的内在信息(方向、阶跃性质和形状等)。

结语

在DSP仿真软件CCS中设置断点,经过多次图像采集处理的测试,均可以得到的完整的图像信息。结果表明,使用异步FIFO作为TVP5150与DSP之间的数据传输连接器,能够达到系统预设功能,并且可以稳定、高速地进行传输。

-

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用2023-10-18 2571

-

基于FPGA器件实现异步FIFO读写系统的设计2020-07-16 1503

-

基于FIFO芯片和MC9S12DG128单片机实现图像采集系统的设计2018-11-27 6240

-

基于FPGA的异步FIFO设计方法详解2018-07-17 8846

-

基于异步FIFO结构原理2018-02-07 1197

-

异步FIFO在FPGA与DSP通信中的应用解析2017-10-30 1679

-

基于DSP技术的图像采集系统研究设计2017-10-23 963

-

基于异步FIFO在FPGA与DSP通信中的运用2017-10-19 938

-

基于DSP和FPGA技术的细胞图像采集系统设计2016-08-26 636

-

异步FIFO在FPGA与DSP通信中的运用2011-12-12 907

-

基于DSP的最小图像采集处理系统设计2011-09-14 2646

-

Camera Link接口的异步FIFO设计与实现2010-07-28 737

-

异步FIFO和PLL在高速雷达数据采集系统中的应用2009-12-22 2639

-

DMA控制器在DSP数据采集系统中的应用2009-04-28 10416

全部0条评论

快来发表一下你的评论吧 !