高速信号完整性分析测试

描述

随着人工智能、数据中心、5G/6G、云计算、商用机器人和自动驾驶的快速发展,高速数据传输犹如连接城市的高速公路网络一般,广泛应用于消费电子、商用和军用领域。国际标准组织IEEE和OIF光联盟在不到十年内将以太网速率从10G提升至800G,推动了数字电路传输速度的飞跃。与此同时,PCB、连接器以及背板上信号的传输速率也越来越高,其中串行数据通信在传输过程中占据主导地位。在当今社会对于高速信号需求普遍存在的大背景下,按照最严格性能标准制造且设计精密的各种高速互连PCIE/ETH/VPX背板以及高速线缆,变得至关重要。背板作为嵌入式系统中的通信主干,必须依据严格的信号完整性标准开展设计,以确保系统内模块之间能够实现及时且精准的数据传输。

由于高速串行信号传输速率不断攀升,在电路设计过程中,工程师常常遇到诸多棘手问题,诸如:系统不稳定、间歇性的死机、不同产品兼容性差以及经常出现误码等,而这些现象多半是信号完整性的问题。依照信号传输的完整流程,分别针对 TX 端(发送端)、传输链路以及 RX 端(接收端)展开相应测试,便能够精准地定位问题根源,从而为后续的优化改进工作提供有力依据,确保高速传输系统的高效稳定运行。

什么是信号完整性?

sinolink technologies

信号完整性(Signal Integrity,简称SI)是指信号在线路传输过程中保持质量的能力,其核心要求在于确保信号的完整性、准确性和可靠性。在电子系统设计中,如果信号能够按照既定的时序、持续时间和电压幅度到达接收端,则表明该电路具有良好的信号完整性。良好的信号完整性意味着信号在传输和接收过程中能够维持规定的电平和时序。反之,若信号完整性差,其影响因素诸多。其中主要是电源完整性问题。影响因素包括时序问题、反射、串扰、传输距离、信号衰减、温度变化、信号传输介质、杂散、地弹、振铃等,这些都会对信号完整性造成负担,从而导致系统的稳定性下降、误码率增加、功耗增加和性能下降。因此,在高速电路设计中,确保良好的信号完整性至关重要。

在高速电路设计面临三个严峻的问题:信号完整性SI ,电源完整性PI,电磁干扰EMI。SI的主要任务是保证数字电路各芯片之间信号的准确传递;PI的主要目的是确保各部分电路和芯片的可靠供电和噪声抑制;EMI主要目的是确保PCB电路即不干扰其它设备,也不被其它设备干扰。值得注意的是SI的问题,一半以上是因为电源不好引发的信号质量问题,在EMI问题中,一个重要的影响因素是PDN上的高频噪声尤其是电源/地之间的高频噪声。

高速串行信号质量如何评估?

sinolink technologies

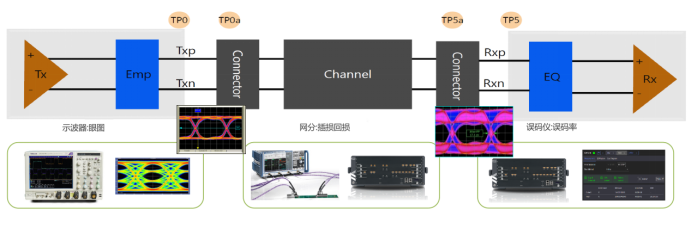

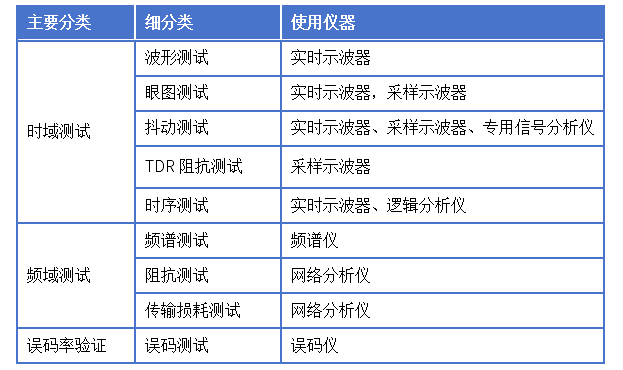

在高速信号传输链路中互连链路上任何一个环节的故障可能影响整个系统工作的效率以及稳定性,对于测试人员需要花费更多的成本去发现问题、定位问题、分析问题、解决问题。新标准逐渐从单一互连简单要求的基础上,额外增加协同整体要求。整个高速链路性能的评估,包括Tx发送端,传输链路,以及Rx接收端三大部分组成,发送、接收、电缆或者背板需要放在一个互连链路中评估。评估时按照时域、频域和其他进行不同仪表的选取。

高速链路信号完整性测试工具

TX发送端信号质量的评估

其中TX发送端经常用示波器进行波形完整性、时序完整性、电源完整性、抖动/眼图等测试。

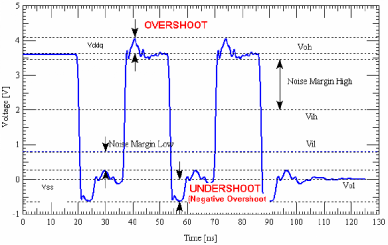

波形完整性:

主要关注波形的单调性、过冲、振铃、衰减。

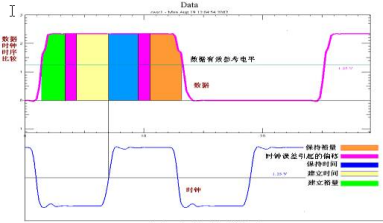

时序完整性:

主要关注建立保持时间、时序抖动、skew、毛刺等。

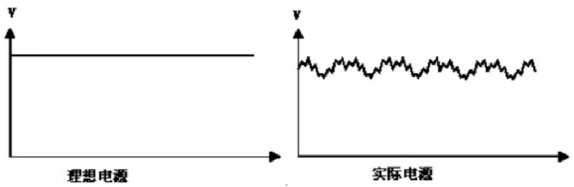

电源完整性:

简称PI,是单板电源设计的一项技术,通过合理的电源平面和滤波设计,为单板上的器件提供稳定/洁净的电源供电,保证单板稳定工作,所以纹波测试为电源测试的必测项,PI和SI是相互影响的。PI包括电源系统设计、直流压降分析、电压瞬态分析、同步开关噪声以及器件建模等。

抖动/眼图:

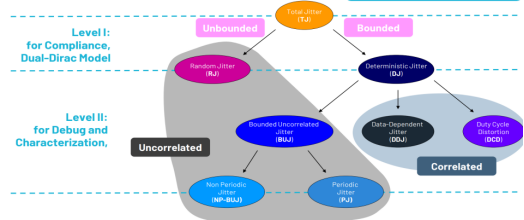

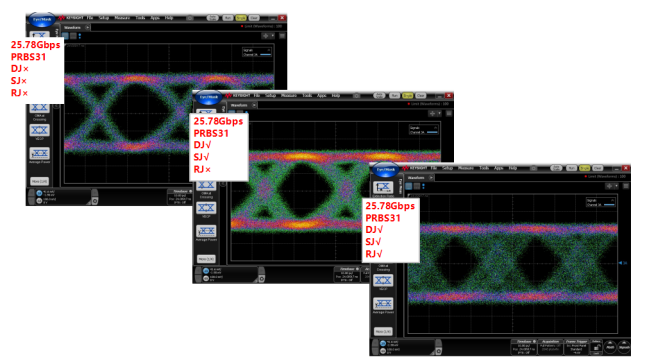

损耗、反射、串扰三大信号完整性的杀手给信号传输带来巨大影响,会使信号的抖动变大,眼图变差,干扰时钟恢复,降低系统性能,进而在接收端带来误码。抖动又可以按照成因分为:TJ、RJ、DJ。DJ中又可细分为PJ、DCD、ISI/DDJ。

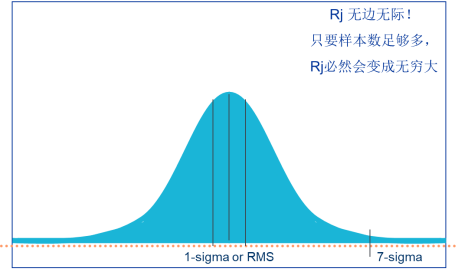

其中Random Jitter(随机抖动)的统计分布是正态高斯分布,是无界抖动,随着样本量的增加RJ会一直增加。

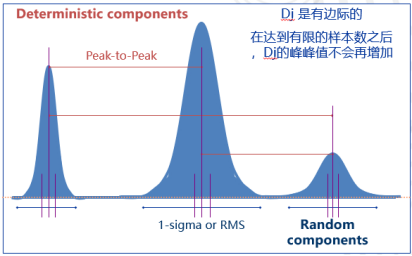

然而Deterministic Jitter (确定性抖动)是有界抖动,在达到有限样本数之后,DJ的peak-peak值不会再增加。

上述抖动在测试中经常用来定位问题信号完整性问题来源,除此之外,我们通常还需要进行眼图模板的测试来直观的表述信号质量的好坏。

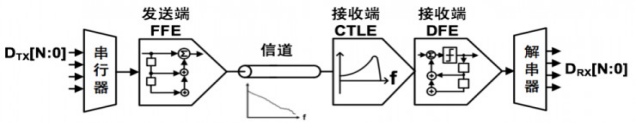

为了在抵抗传输损耗带来的影响,改善信号质量,常用的均衡有TX端的FFE,RX端有FFE、CTLE、DFE。

其中TX端的预加重和去加重的目的都是尽量平衡高频分量和低频分量,减少传输链路对高频分量衰减大于低频分量衰减。预加重技术就是在传输线的始端增强信号的高频分量,以补偿高频分量在传输链路中较大的衰减。去加重则是降低低频分量的始端信号。

其中RX端最常用的均衡包括FFE、CTLE、DFE。

FFE实质是使用数字线性高通滤波器提高信号的高频分量,实现信道的补偿。

CTLE是直接通过线性模拟高通滤波器拟合信道的衰减,实现信道的补偿。信道的频率响应可以看做是一个低通滤波器,因此将信道和一个高通滤波器串联就能得到一个全通的滤波器。

DFE为判决反馈均衡,就是将判决后的信号反馈到输入信号上。与FFE类似,DFE也是通过数字高频滤波器实现的,DFE可以只放大高频信号,而不放大高频噪声。

高速传输链路评估

信号在传输链路路径上传输时会有损耗,反射,串扰的问题,导致信号发生畸变。

损耗:传输线的损耗对不同频率是不均匀的,频率越高,损耗越大,上升沿越缓。速率越高,传输线越长,损耗所带来的问题越严重,眼图越容易闭合。

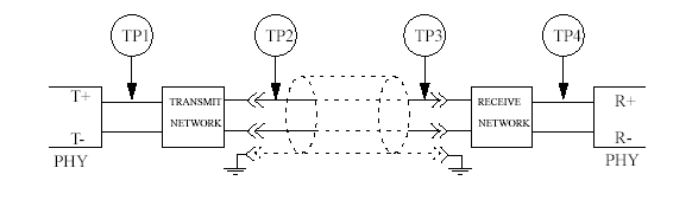

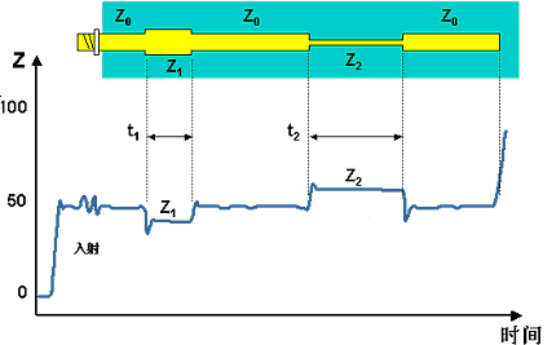

反射:传输线上分布电容、电感、和小电阻的存在,会导致传输线的分布式阻抗不均匀,信号流经传输线时部分能量会沿原路反射回去,通常使用TDR来测量传输路径的阻抗变化,如下图:

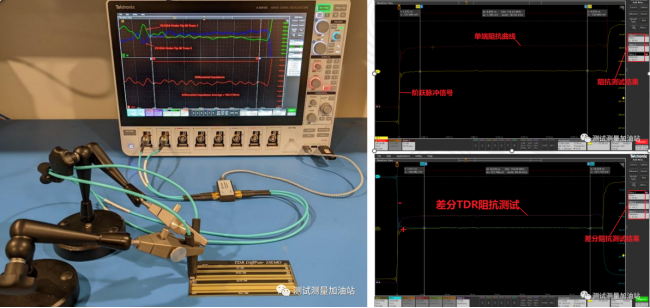

下面为实时示波器TDR阻抗测试:

信号在传输过程中,对不同速率其损耗不同,反射和串扰都可以导致信号的波形发生失真,导致眼图闭合。通常使用矢量网络分析仪VNA进行S参数测试和TDR或VNA进行阻抗测试。

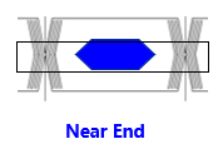

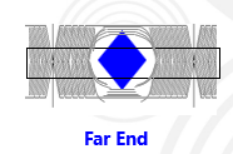

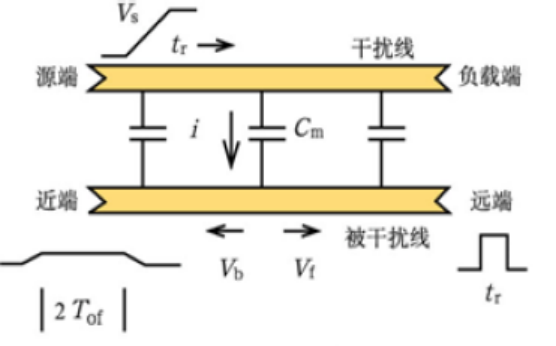

串扰:相邻通道间通过地线或空间辐射产生的互相影响。频率越高,串扰越大。串扰会带来额外的噪声,毛刺,抖动,并且使得信噪比变差。远端串扰: 同向传输(同源)信号的干扰,幅度高,脉冲很窄。近端串扰: 反向传输(非同源)信号的干扰,幅度低,脉冲很宽。

RX接收端容限能力的评估

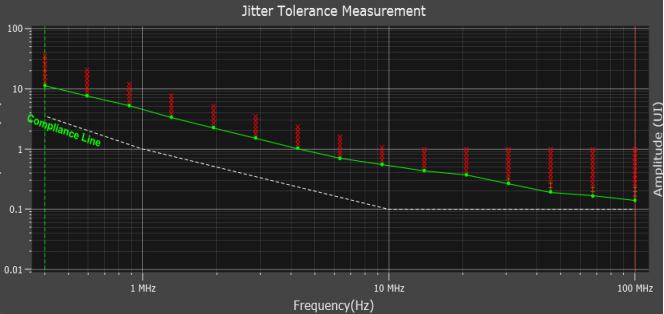

发送端一般利用实时示波器测抖动和眼图,接收端需要利用误码仪进行抖动容限测试和噪声容限测试。接收端中包括CDR时钟恢复、复杂的均衡和信号调理等复杂结构。单纯考察发送端是不足以保证没有误码,接收端的测试也是非常重要,各种高速标准也明确提出了接收端容限测试的规范。误码仪是进行高速SerDes芯片接收端测试必备仪器。RX接收端会根据对应的协议规范或者自定义标准进行误码率、JTOL、ITOL的测试。下面我们以RX接收端测试为例为大家介绍高速传输链路信号完整测试。

测试原理:

使用测试仪表产生一个劣化(注入抖动)的眼图信号,俗称压力眼信号。压力眼信号的参数有明确规定,,在不同的规范中具体指标会有不同。通过校准后的压力眼会输入被测接收机进行抖动容限测试。中星联华SL3000B系列高性能误码仪可提供PJ、RJ、BUJ等抖动注入,可以为RX JTOL测试提供强力支持。

测试流程:

产生规范要求的抖动分量,在不同的频点上分别产生相应的抖动量

将stressed信号注入DUT Rx

统计DUT Tx端发出的信号的误码率是否达到要求

注入抖动眼图:

测试结果图:

目前,中星联华的高性能误码仪是国内首个支持注入抖动和加噪声创建压力信号的高性能误码仪,也是目前国内首款能够满足接收端抖动容限JTOL和噪声容限ITOL测试的误码仪。其中可支持的注入抖动类型有低频正弦抖动、高频周期抖动、BUJ串扰抖动、RJ随机抖动以及SSC扩频时钟等;支持的噪声类型有CMI和DMI和BBN宽带白噪声,有效地解决“卡脖子”的难题。

RX接收端测试利器——

中星联华高性能误码仪

sinolink technologies

产品特色:

模块化:多通道灵活配置,单机支持32发32收

高速率:1G-120Gbps,数据速率灵活可调

压力眼:注抖加噪,让信号拥有72般变化

UDP:最大可支持16Gbit超长用户自定义码型

中星联华高性能误码分析仪具有模块化设计、灵活的通道配置、高速率、注抖加噪创建压力眼信号、超长用户自定义码型等业内领先的核心技术,可用于高速Serdes芯片和高速接口、光芯片、光器件、光模块、光传输、高速互连等领域苛刻的测试。

-

听懂什么是信号完整性2024-12-15 1393

-

12月20日线上讲堂|听懂什么是信号完整性2024-12-06 997

-

高速PCB信号完整性设计与分析2024-09-21 721

-

如何实现高速连接器信号完整性分析2023-06-04 3431

-

高速信号完整性测试和验证技术2017-01-14 1298

-

高速信号的电源完整性分析2012-08-02 3622

-

高速电路信号完整性分析与设计—高速信号完整性的基本理论2012-05-25 2118

-

高速并行总线信号完整性测试技术2009-10-17 1146

-

高速电路信号完整性分析与设计—信号完整性仿真2009-09-12 44468

-

高速电路的信号完整性分析2008-10-15 1392

-

高速电路信号完整性分析之应用篇2006-05-28 1125

全部0条评论

快来发表一下你的评论吧 !