后悔没有早点看到:天线设计中的知识点!

电子说

描述

天线设计,也是4G模组应用中最容易踩坑的地方。今天主要分享讨论Air700ECQ/EAQ/EMQ系列模组,天线管脚到4G天线之间的电路设计和走线规则。

Air700ECQ/EAQ/EMQ模组属于Cat.1 bis R13架构,天线架构精简为单天线架构,去掉了分集接收天线,因此只需要一根天线。

知识点:

Cat.1 bis相对于Cat.1的区别是,后者为两根天线(一根主天线,一根分集天线);Cat.1 bis在设计和应用上更简单,更符合低速物联网的实际应用场景。

一、天线的阻抗控制和匹配

由于Air700ECQ/EAQ/EMQ射频天线传输的信号频率区间,从824MHz到2655MHz不等,属于高速模拟信号,因此对于天线电路设计,主要目的是:

保证射频信号无损的从模组天线管脚传输至4G天线,也就是关注于模组和4G天线的射频PCB传输线以及匹配电路。

整个射频传输链路如下所示:

4G模组---->PCB传输线----->天线匹配---->PCB传输线---->射频连接器---->同轴传输线---->4G天线

特别说明:

有些产品可能不需要“射频连接器”和“同轴传输线”;本文仅以需要“射频连接器”和“同轴传输线”的情况进行说明。

1. 阻抗控制:

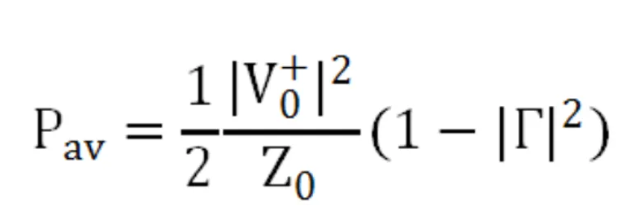

根据传输线理论,负载端的传输功率为:

其中Γ为反射系数;Z0为传输线特征阻抗;V0为传输电压。

由此可见:

当反射系数为0,即负载匹配时候,传送到负载的功率最大;

当反射系数为1,即负载失配时候,传送到负载的功率为0。

因此,为了保证尽可能保证射频功率无损的传到4G天线,则必须保证PCB传输线的反射系数尽量接近0。

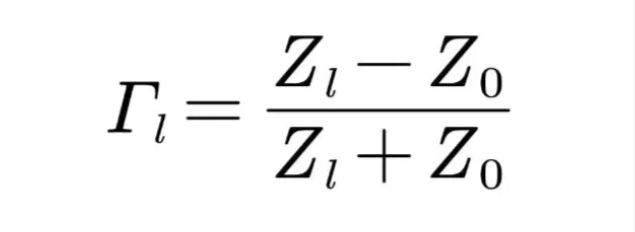

而反射系数为:

其中Γ为反射系数;Z0为传输线特征阻抗;ZL负载端特征阻抗。

负载阻抗ZL=Z0,根据反射系数的公式,分子为0,所以,反射系数为0,表示无反射;

当负载开路的时候,即负载阻抗无穷大,分子分母上的Z0可以忽略不计,所以,反射系数为1。

对于射频系统的行业规范,射频器件输出阻抗和输入阻抗均是按照50欧姆特征阻抗来设计。因此,在我们设计PCB传输线时,也要将传输线特征阻抗控制在50欧姆附近才能保证反射系数最小。

2. 匹配网络:

由于模组射频管脚输出阻抗和4G天输入阻抗由于各种原因,无法完全做到精确50欧姆特征阻抗,总是会有容抗的成分,因此就需要增加匹配网络来调整信源和负载为纯组性,即负载阻抗与信源阻抗满足共轭匹配时,能够使负载得到最大功率。

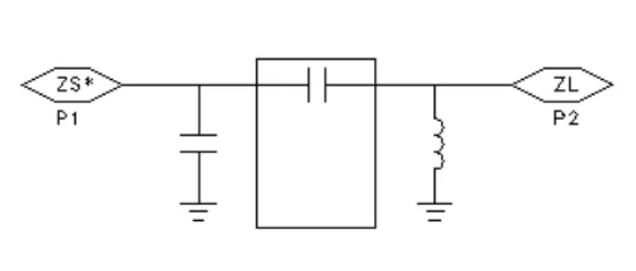

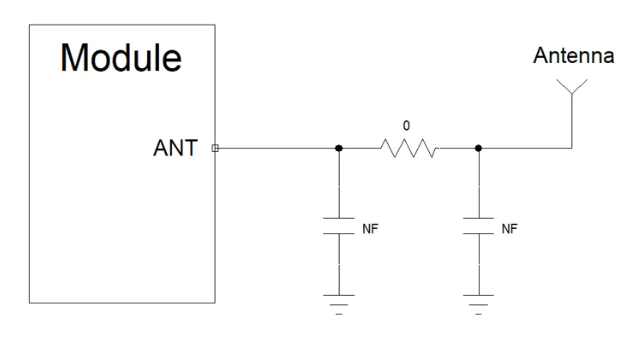

通常在4G模组天线端预留Π型匹配网络,以便在4G天线调试时能够给与足够的匹配调整空间。

二、天线传输线的参考设计

虽然天线电路原理设计并不复杂,但天线走线的PCB设计非常重要——直接影响整个系统的射频指标性能。

模组天线电路的参考设计如下:

注意事项:

连接到模组RF天线焊盘的RF走线必须使用微带线或者其他类型的RF走线,阻抗必须控制在50欧姆左右;

在靠近天线的地方预留Π型匹配电路,两颗电容默认不贴片,电阻默认贴0欧姆,待天线厂调试好天线以后再贴上实际调试的匹配电路;

Π型匹配电路靠近天线放置。

三、推荐的PCB堆叠和线宽方案

一般情况下,射频信号线的阻抗由材料的介电常数、走线宽度(W)、对地间隙(S)、以及参考地平面的高度(H)决定,因此天线走线需要做50欧姆特征阻抗控制,需要对本文前面所述的几个参数做精确控制。

PCB特性阻抗的控制通常采用:

微带线、共面波导两种方式。

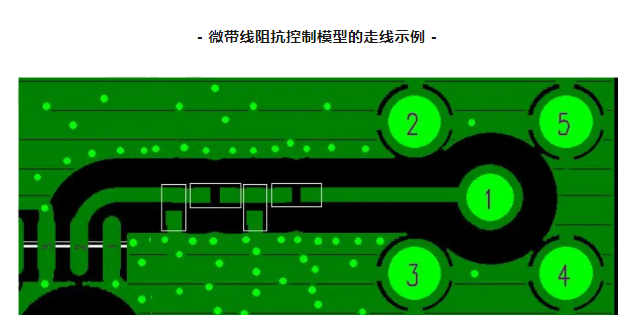

1. 微带线:

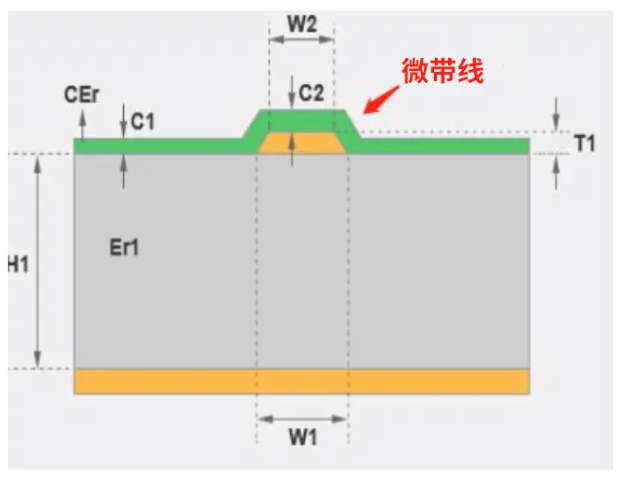

微带线是一根带状导线,指只有一边存在参考平面的传输线,顶部和侧边都曝置于空气中(也可上敷涂覆层),位于绝缘常数Er线路板的表面之上,以电源或接地层为参考。

如下图所示:

注意事项:

通常在PCB设计时会在表面大范围覆铜,如果采用微带线做阻抗控制,要注意射频走线要与周围覆铜的地保持3倍线宽以上,避免周围的地对阻抗的影响。

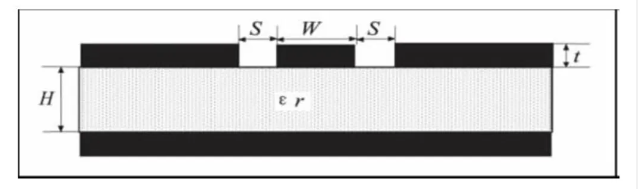

2. 共面波导:

共面波导是将两个平行的导体与一个介质隔离开来,它们位于同一平面内,而电场则穿过介质。

相对于微带线和带状线,共面波导的特点是:

结构简单、宽带、低损耗、易于与其他微波元器件进行集成等优点,适用于集成电路中高频段的传输。

共面波导需要精确控制射频走线与周围地铜箔的距离,相对微带线来说控制难度相对较高。

▼ 微带线与共面波导的选择 ▼

虽然微带线和共面波导模型理论上都能做到传输线的50欧姆阻抗控制,但是在实际的设计中还要考虑阻抗控制后的线宽能否具备实际可操作。

例如:

在用2层PCB板,1.2mm板厚情况下,用微带线模型算出的50欧姆理论线宽为77mil。

这个线宽在实际设计中根本无法设计,即不具备可操作性。

同样的用共面波导模型,在距离两边地铜箔4mil距离情况下,线宽仅13.8mil就能达到50欧姆阻抗。显然,这种情况下共面波导模型更符合实际设计要求。

常用的PCB 50欧姆阻抗控制堆叠方案:

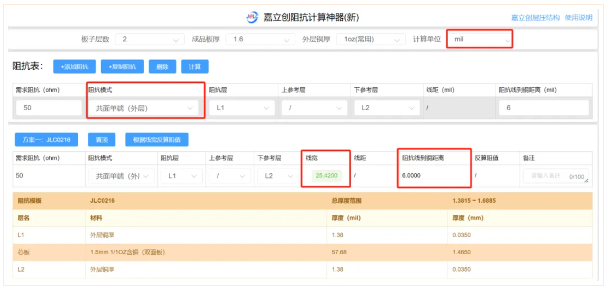

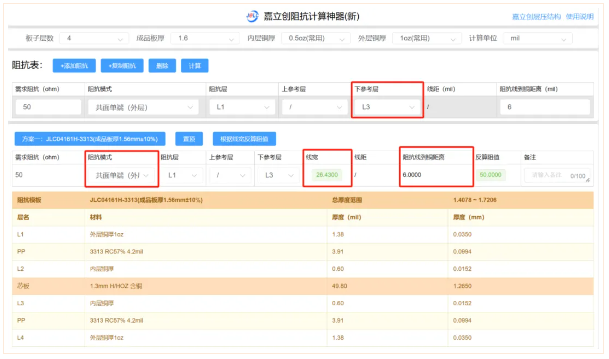

01)二层PCB板共面波导结构,下方参考地为L2层:

2层板1.0mm板厚:共面波导

阻抗线到铜箔距离 6mil,线宽 21.77mil;

2层板1.2mm板厚:共面波导

阻抗线到铜箔距离6mil,线宽24.11mil;

2层板1.6mm板厚:共面波导

阻抗线到铜箔距离6mil,线宽25.42mil;

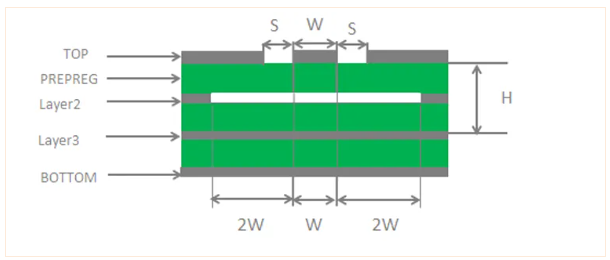

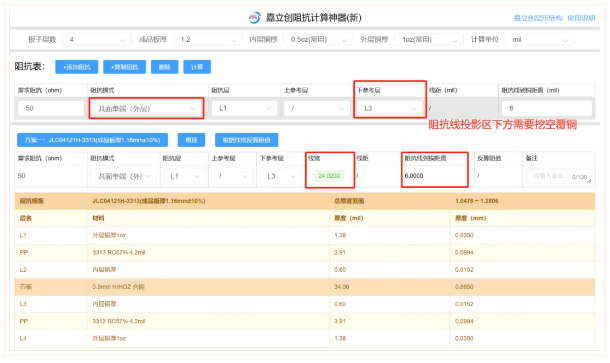

02)四层PCB板共面波导结构,下方参考地为L3层:

上图需要注意多层板结构参考地和阻抗线之间的层,需要将阻抗线投影区下方挖掉5W线宽的覆铜如上图L2层。

4层板1.2mm板厚:共面波导

阻抗线到铜箔距离6mil,线宽24.02mil;注意L2层阻抗线下方覆铜挖空处理。

4层板1.6mm板厚:共面波导

阻抗线到铜箔距离6mil,线宽26.43mil;注意L2层阻抗线下方覆铜挖空处理。

3)阻抗控制计算方式:

下面是立创阻抗计算器网址,如果有其他线宽和叠构需求,请自行计算;投板的时候请将需要阻抗控制的线段高亮截图给板厂,要求板厂按要求进行微调管控。

嘉立创阻抗计算神器:

https://tools.jlc.com/jlcTools/index.html#/impedanceCalculateNew

四、天线传输线设计规则

在射频天线接口的电路设计中,为了确保射频信号的良好性能与可靠性,建议遵循以下设计原则:

传输线整段走线都要进行50欧姆阻抗控制;

与射频引脚相邻的地引脚不做热焊盘,要与地充分接触;

射频引脚到射频连接器之间的距离应尽量短,同时避免直角走线,建议走线夹角保持为135°;

建立连接器件的封装时,信号脚需与地保持距离;

射频信号线参考的地平面应完整;在信号线和参考地周边增加一定量的地孔可以帮助提升射频性能;

射频信号线必须远离干扰源,避免和相邻层的任何信号线交叉或平行。

五、你一定要听的几句忠告

天线设计,是4G模组应用中最容易踩坑的地方。

这也是所谓的行业内专业人员和行业外非专业人员,最大的经验差别。

天线效果差异:

天线设计的差,信号质量就差,在基站信号好的地方体验不出来差别,最多就是功耗大一点(信号越差,发射功率越大,电流就越大,耗电量就越多)。

但在基站信号不那么好的地方,就是能联网和不能联网的区别,体验一个天上一个地下。

如果使用的是外置天线:

比如棒状天线,这时只需要内部PCB走线就可以,本文已经做了详细描述和提醒。

如果使用的是内置天线:

天线的性能不仅与内部PCB走线有关系,也与外壳的材质、天线在外壳内的空间以及天线周边的器件干扰等等都有关系,需要找专业的天线厂进行评估,尤其是在设计之初就要同天线厂进行沟通,以免后续生米做成熟饭造成无法挽回的损失。

Air700ECQ支持Wi-Fi Scan(注:Air700EAQ/EMQ不支持),跟4G共用天线,不需要单独针对Wi-Fi Scan功能进行天线调试。

虽然本文讲了很多关于天线方面的专业知识,但是对于大多数用户来说是不需要自己深刻掌握,只需要知道天线常识的来龙去脉就可以了。大多数时候,只需要找专业的天线厂帮忙搞定即可。

今天的内容就分享到这里了~

审核编辑 黄宇

-

Synopsy的Host和DPHY的知识点详解,错过后悔2022-03-08 1481

-

stm32f103中的电路知识点大合集,错过后悔2022-02-21 1272

-

文件管理的知识点汇总,错过绝对后悔2021-12-23 1432

-

IO口的知识点汇总,错过绝对后悔2021-12-15 1177

-

串口通信的知识点汇总,错过绝对后悔2021-12-13 1391

-

UART异步通信的知识点汇总,错过绝对后悔2021-12-10 1246

-

串口通信的基础知识点汇总,不看肯定后悔2021-12-03 2625

-

UART的知识点汇总,不看肯定后悔2021-12-02 1242

-

JVM的知识点汇总,不看肯定后悔2021-11-30 1691

-

ARM汇编基础知识点汇总,错过肯定后悔2021-11-29 1604

-

IIC总线的知识点汇总,不看肯定后悔2021-11-23 1295

-

DAC的知识点汇总,不看肯定后悔2021-11-08 5122

-

ARM Cortex的知识点汇总,不看肯定后悔2021-11-05 2003

全部0条评论

快来发表一下你的评论吧 !