芯片流片的基础知识

描述

在当今科技迅猛发展的时代,半导体芯片的创新已成为推动各行各业,尤其是汽车行业进步的关键力量。随着智能驾驶技术的兴起,对高性能芯片的需求正迅速增长。

7月27日,蔚来汽车公司在NIO IN创新科技日上宣布了一项重大突破:他们成功流片了全球首颗5纳米工艺的车规级智能驾驶芯片——“神玑NX9031”。这一成就不仅标志着蔚来在芯片设计领域的突破,也预示着即将到来的测试和验证阶段。一旦性能和质量达到设计要求,这款芯片将进入大规模量产,并最终实现商用,为蔚来汽车的智能驾驶技术提供强大动力。

“神玑NX9031”芯片的成功流片,不仅展现了蔚来在自主研发和技术创新方面的强大实力,而且推动了汽车芯片国产化的进程,为全球汽车产业的发展贡献了中国智慧和中国力量。预计在2025年第一季度,这款芯片将首次搭载在蔚来的旗舰轿车ET9上,为智能驾驶技术的发展开启新的篇章。

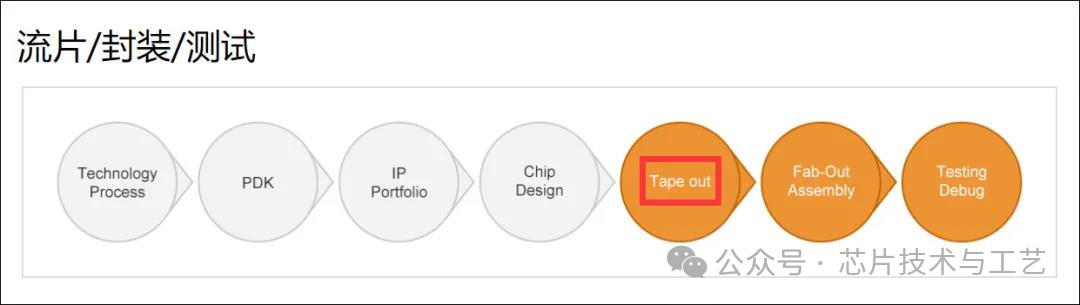

芯片流片(Tape Out)技术是半导体制造中的核心环节,将设计图案精确转移至硅片上,是设计与生产的关键桥梁。本文全面探讨了芯片流片技术,从设计、流片准备到技术实施、设备与材料应用,分析了流片过程中的关键环节与挑战。研究发现,芯片流片的成功直接影响芯片设计的可制造性和市场竞争力,设计复杂度和成本控制是主要挑战。为应对这些挑战,建议采用高效设计工具、优化工艺参数和材料选择等策略。

| 阶段 | 详细解释 |

|

Technology Process (技术工艺) |

选择和定义芯片制造所需的工艺技术。工艺技术包括晶体管的尺寸、材料的选择以及制造流程的详细规范。不同的工艺技术适用于不同类型的芯片,如高性能处理器、低功耗设备等。 |

|

PDK (Process Design Kit,工艺设计套件) |

为芯片设计人员提供的一组工具和文件,包含工艺技术的详细信息、设计规则和验证方法。设计人员使用PDK来确保他们的设计符合制造工艺的要求,保证芯片能够正确制造。 |

|

IP Portfolio (知识产权库) |

包括预先设计和验证的功能模块(如处理器核心、存储器模块、接口电路等)。设计人员可以使用这些模块来加速芯片设计过程,并减少设计中的风险和错误。 |

|

Chip Design (芯片设计) |

根据需求和PDK中的规范进行芯片的详细设计。设计包括逻辑设计、物理设计和电路布局等。设计完成后,需要进行仿真和验证,以确保芯片功能和性能符合要求。 |

|

Tape Out (流片) |

将最终设计的芯片版图数据提交给制造厂商进行生产。这是芯片制造流程中的重要里程碑,意味着设计阶段的结束和制造阶段的开始。 |

|

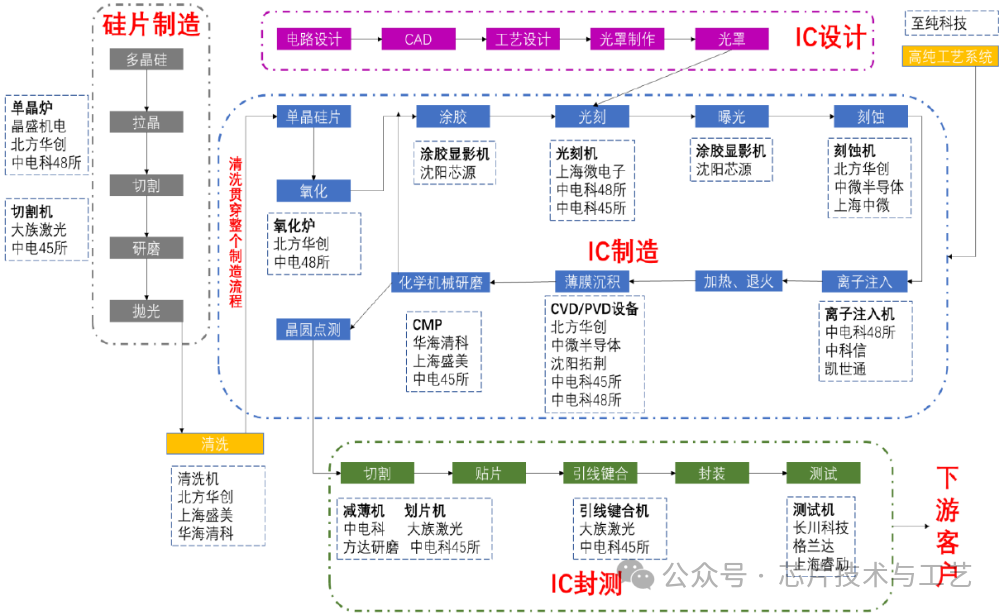

Fab-Out Assembly (晶圆制造和封装) |

包括晶圆制造和芯片封装。晶圆制造过程涉及一系列复杂的工艺步骤,如光刻、刻蚀、离子注入等。制造完成后,晶圆被切割成单个芯片,然后进行封装,以保护芯片并提供电气连接。 |

|

Testing Debug (测试和调试) |

制造和封装完成后,芯片进入测试和调试阶段。测试包括功能测试、性能测试和可靠性测试,确保芯片在各种条件下都能正常工作。如果发现问题,需要进行调试和修复。 |

此外,文章展望了芯片流片技术的市场应用与未来趋势,指出其在消费电子、通信、汽车和医疗等领域的广泛应用前景,以及技术进步带来的高精度、低成本流片需求的持续增长。

#01

引 言

1.1 芯片流片的定义

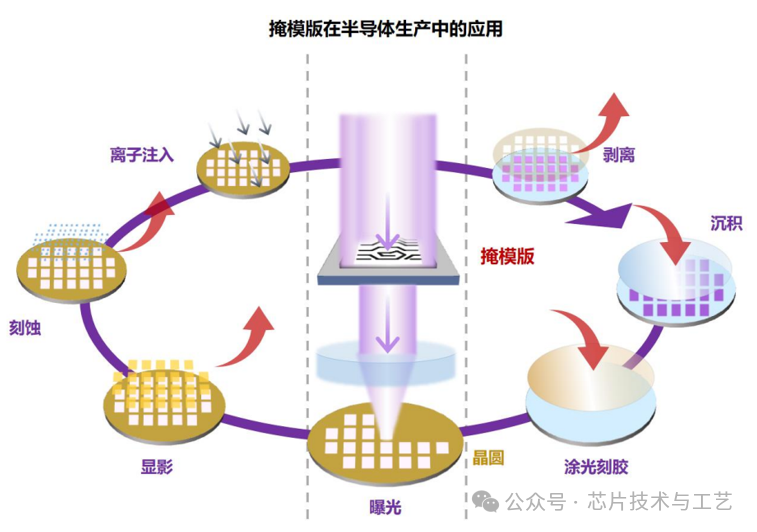

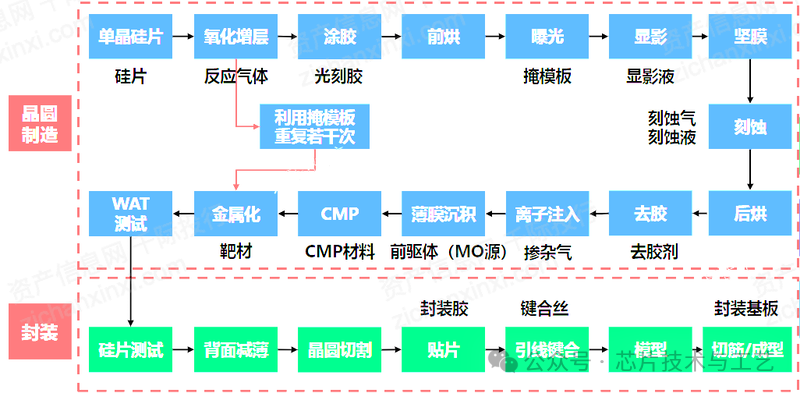

芯片流片是半导体制造中的关键环节,指将设计好的芯片图案从计算机数据转化为实际硅片上的物理结构的过程。这个过程包含光刻、刻蚀、离子注入、金属沉积等精密工艺,确保在硅片上精确构建设计的集成电路。

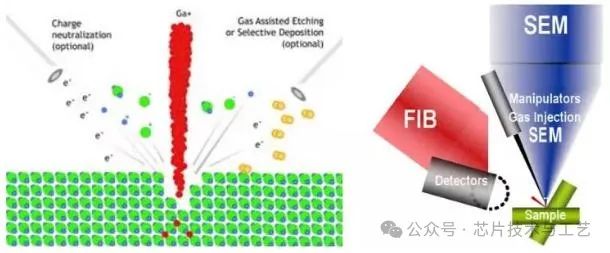

芯片流片不仅是连接设计与生产的桥梁,还需要严格的质量控制,以保证最终产品的性能和可靠性。任何工艺失误可能导致芯片失效,因此对工艺精度和操作环境的要求极高。有时需要通过聚焦离子束(FIB)编辑技术对芯片进行物理修改,以纠正设计错误或满足客户需求,从而减少研发成本和时间。

*聚焦离子束(Focused Ion Beam, FIB)技术是一种利用高能离子束进行微观加工和分析的技术。

| 项目 | 详细解释 |

| 技术原理 | 聚焦离子束技术使用高能离子束(通常是Ga+离子)聚焦在样品表面,通过离子的物理撞击和溅射作用,对样品进行纳米级的加工和分析。 |

| 主要组成部分 |

1. 离子源:产生高能离子束,常用的是液态金属离子源(LMIS)。 2. 聚焦系统:使用电场和磁场将离子束聚焦到样品表面。 3. 样品台:用于固定和移动样品,实现对特定区域的加工和分析。 |

| 应用领域 |

1. 半导体制造:用于电路修复、故障分析和截面制作。 2. 材料科学:用于纳米级加工、材料表面改性和截面分析。 3. 生命科学:用于生物样品的精细加工和分析。 |

| 主要功能 |

1. 纳米加工:通过精确控制离子束,可以在样品表面进行纳米级的雕刻和切割。 2. 截面制备:用于制作样品的精细截面,方便后续的显微分析。 3. 元素分析:结合能量色散X射线光谱(EDX),可进行元素成分分析。 |

| 优势 |

1. 高精度:能够进行纳米级的加工和分析。 2. 多功能:集成了加工、分析和成像功能。 3. 非接触:离子束与样品无直接接触,避免了机械损伤。 |

| 局限性 |

1. 损伤效应:高能离子束可能会对样品产生损伤和污染。 2. 材料选择:某些材料对离子束的响应不佳,可能影响加工效果。 3. 成本高:设备和操作成本较高。 |

| 最新进展 | 近年来,聚焦离子束技术在高分辨率加工和无损分析方面取得了显著进展。新的离子源材料和聚焦系统的改进,使得FIB的应用范围不断扩大,特别是在纳米科技和生物医学领域。 |

随着半导体技术的进步,芯片流片工艺不断创新。例如,微型立铣刀技术简化了微通道芯片的制造流程,降低了生产成本。芯片流片的成功依赖多方面的技术合作,如中芯国际与灿芯半导体合作实现了40纳米低漏电工艺的ARM Cortex-A9双核测试芯片流片,展示了设计、制造与测试环节的紧密协作。

全球范围内,芯片流片技术的应用案例层出不穷,如中国成功流片的首个自主研发5G微基站射频芯片,体现了国内半导体制造技术的突破,并支持了5G通信技术的发展。

芯片流片技术在半导体制造中的重要性不可忽视。它不仅是实现芯片设计转化为实际产品的关键环节,也是推动半导体行业技术创新和产业发展的核心动力。随着技术的进步和市场需求的增长,芯片流片技术将继续发挥其不可或缺的作用。

1.2 芯片流片的重要性

芯片流片在半导体制造中占据着重要地位,不仅是将芯片设计转化为实际产品的关键环节,也是连接设计与生产的桥梁。以下是其重要性的几个方面:

实现芯片设计落地:流片过程是将设计好的芯片图案通过一系列精密制造步骤转移到硅片上,形成具有特定功能的集成电路。流片的成功意味着设计的芯片可以顺利转化为市场上的实体产品,直接影响芯片产品的问世和市场竞争力。

工艺优化和成本控制:流片过程中的工艺优化和成本控制对芯片的市场竞争力至关重要。随着半导体技术的发展,芯片制造的复杂性和成本也在上升。通过工艺优化可以降低生产成本,提高生产效率,从而使芯片产品更具市场竞争力。同时,严格的成本控制确保了芯片产品的盈利能力。

推动技术进步:流片技术的不断进步为半导体行业的发展提供了有力支撑。随着摩尔定律的推进,集成电路的集成度提高,对流片技术提出了更高的要求。采用更先进的制程技术、引入新材料和工艺,这些技术进步不仅提升了芯片产品的性能,还拓展了半导体行业的应用领域和市场空间。

总之,芯片流片不仅是实现芯片设计向产品转化的关键环节,更是影响芯片市场竞争力和推动半导体行业持续发展的核心因素。提升流片技术水平和成功率,对促进半导体产业的繁荣和创新具有重要意义。

#02

芯片设计与流片准备

2.1 芯片设计流程

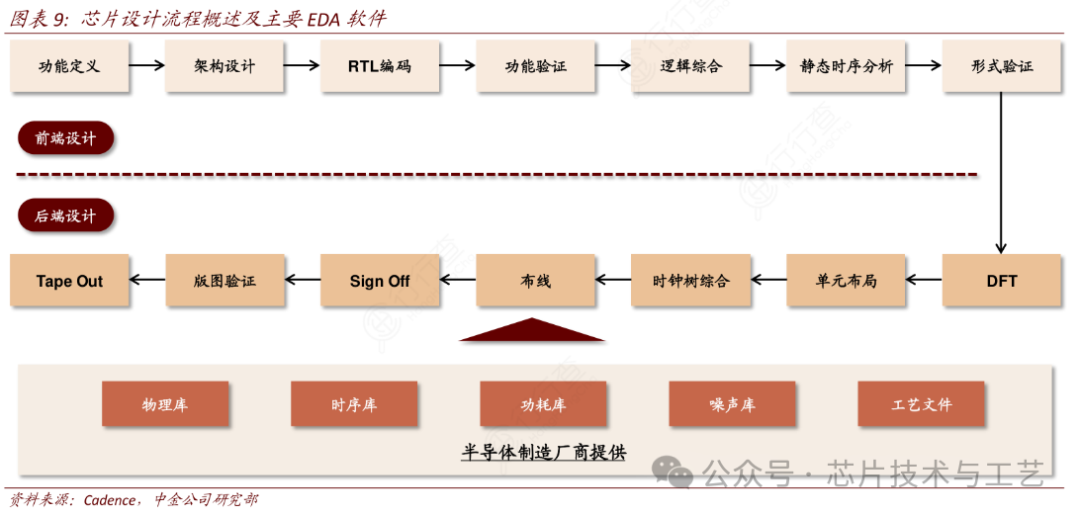

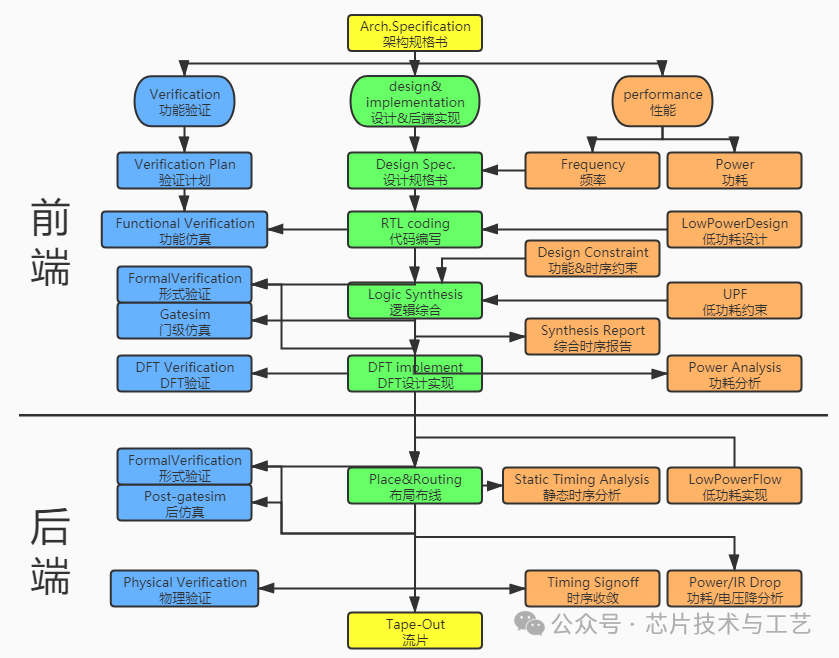

芯片设计流程是一个复杂且精细的过程,涵盖从功能定义到物理版图生成的多个环节,通常分为前端设计和后端设计两大阶段。

a.RTL设计,即寄存器传输级(Register Transfer Level)设计,是数字电路设计中的一个关键阶段。在这个阶段,设计师使用硬件描述语言(HDL),如Verilog或VHDL,来描述数字电路的行为和结构。

b.DFT(Design for Testability),即“可测试性设计”,是集成电路设计中的一个重要概念,旨在提高芯片的测试效率和准确性。

前端设计(Front End,也称逻辑设计)是芯片设计的起始点,主要目标是定义芯片的功能和架构。在这一阶段,设计团队进行详尽的需求分析,明确芯片需要实现的具体功能,并编写RTL(寄存器传输级)代码。RTL代码描述了芯片内部的逻辑结构,包括数据通路和控制通路,以及各个组件之间的交互方式。为了确保设计的正确性,前端设计阶段还会进行仿真验证,通过模拟芯片在实际工作环境中的行为来检查是否满足设计要求。

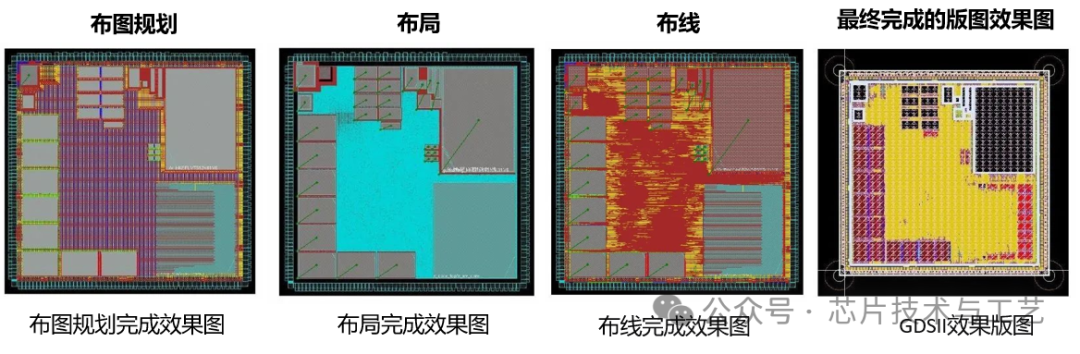

后端设计(Backend,也称物理设计)在前端设计完成后展开,主要任务是将逻辑描述转换为实际的物理版图。后端设计人员进行布局规划,确定各功能模块在芯片上的位置,以优化性能和减少功耗。接着进入布线阶段,确保信号能够准确无误地在各模块之间传递。时序分析和信号完整性分析也是关键环节,确保芯片在各种工作条件下保持稳定性能。经过这些步骤,后端设计最终生成完整的物理版图,为芯片制造奠定基础。

前后端设计的紧密协作是确保芯片设计准确性和可靠性的关键。前端设计人员提供清晰、准确的逻辑描述,而后端设计人员将其转换为高效的物理实现。整个设计流程中不断的迭代和优化是必不可少的,以确保最终芯片产品满足市场需求和性能指标。

总结而言,芯片设计流程通过前后端设计的紧密合作和不断优化,实现从功能定义到物理版图生成的转化,确保最终芯片产品的性能和可靠性。

2.2 流片前准备

在芯片设计完成后,即进入紧张的流片前准备阶段。这一阶段的工作至关重要,因为它直接关系到芯片流片的成功与否。

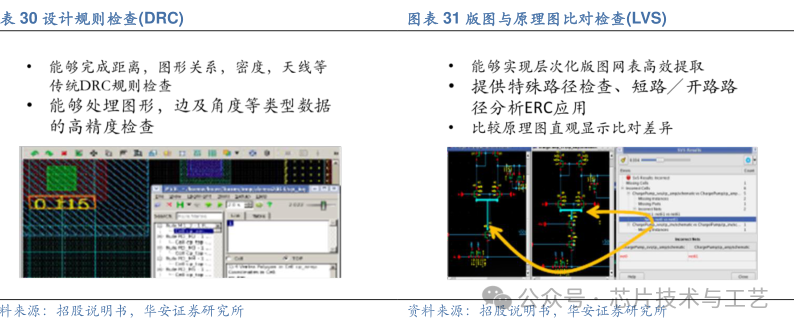

设计规则检查(DRC):这是首要环节,目的是验证设计是否满足制造工艺的要求。例如,在布局布线过程中,必须确保所有设计元素符合制造厂规定的尺寸和间距规则,以避免潜在的制造问题。

版图验证(LVS):这一步骤通过对比设计版图和原理图来确保两者一致,防止设计上的失误或偏差。

寄生参数提取:由于导线电阻、电容等寄生参数的存在,芯片的实际性能可能会与设计预期产生偏差。因此,这一阶段需要精确提取这些寄生参数,并在设计中进行相应的补偿,以确保流片后的芯片性能符合预期。

与流片厂商的沟通:确定具体的工艺参数,如掺杂浓度、氧化层厚度等,这些都是影响芯片性能的关键因素。材料选择也至关重要,不同材料的物理和化学特性直接影响芯片的性能和可靠性。

测试方案制定:决定如何对流片后的芯片进行全面的性能和可靠性测试,以确保芯片满足设计要求。

| 类别 | 子类别 | 描述 |

|

前端设计 (Front-End Design) |

HDL编码/原理图设计 |

Verilog/HDL RTL Coding(Digital):使用硬件描述语言编写寄存器传输级代码。 Schematic input(Analog):使用原理图输入工具绘制电路图。 |

| 前仿真验证 | 使用仿真工具验证RTL代码或原理图功能,确保设计满足规格要求。 | |

| 逻辑综合/静态时序分析/形式验证 |

逻辑综合:HDL代码转门级网表。 静态时序分析:分析电路时序特性。 形式验证:数学方法证明设计满足规范。 |

|

|

后端物理设计 (Back-End Design) |

物理布局布线 | 使用工具将门级网表转物理布局并完成布线。 |

| 物理版图验证 | 检查物理版图是否符合设计规则和版图与原理图一致性。 | |

| 寄生参数提取 | 从物理版图中提取寄生参数,影响电路性能。 | |

| 后仿真 | 考虑寄生参数,仿真设计性能。 | |

|

生产测试 (Manufacturing and Test) |

流片 (tape out) | 设计版图送晶圆代工厂生产。 |

| 生产 (Production) | 完成圆片生产后的切割、测试和分类。 | |

|

芯片封装与测试 (Packaging and Testing) |

芯片封装并进行功能和性能测试,确保质量标准。 |

流片前的准备工作涉及多个方面,需要设计团队与制造厂商的紧密合作,确保每个环节都得到充分的验证和优化。虽然这阶段工作繁琐且耗时,但它是确保芯片流片成功的关键所在。任何疏忽都可能导致流片失败,进而造成巨大的经济损失和时间浪费。因此,设计团队必须高度重视这一阶段的工作,确保每一项准备都细致入微,为后续的流片过程奠定坚实基础。

#03

芯片流片技术详解

3.1 设计检查与版图验证

在进行芯片流片之前,设计检查与版图验证是不可或缺的环节,这两个步骤对于确保流片的成功至关重要。

设计规则检查(DRC):这一过程的主要目的是对芯片版图进行细致审查,确认其是否严格遵循制造工艺规则。这涵盖了线宽、间距、层叠等关键参数的检查。通过高精度的软件工具,版图可以自动扫描,识别任何可能违反制造工艺规则的设计元素。一旦发现违规行为,设计团队会立即收到反馈并进行调整。预防性检查机制显著提高了芯片制造的良率,降低了因设计错误导致的生产风险。

版图验证(LVS):这一步骤确保芯片版图与原始电路设计之间高度一致。验证工具对照电路图和版图,逐一比对每个元件和连接关系,确保版图精确反映电路设计的意图,保证功能实现和性能表现达到预期标准。

设计检查与版图验证并非一次性任务。在设计和流片过程中,这两个步骤可能多次迭代进行,以确保设计的不断完善和优化,每次修改都能通过严格的验证流程。迭代式验证方法提高了设计的可靠性,为后续的芯片测试和量产奠定坚实基础。

随着半导体技术进步,设计检查与版图验证面临的挑战也在增加。芯片集成度提高,版图中元件数量和复杂度增加,要求验证工具具备更高处理能力和精度。同时,新材料的引入和工艺的创新对验证流程提出新的要求。业界不断投入研发力量,以开发更高效和精准的验证工具和方法。

设计检查与版图验证在芯片流片过程中占据举足轻重的地位。它们不仅是确保芯片设计正确性和可制造性的关键步骤,也是推动半导体行业持续发展和技术创新的重要基石。通过不断优化和完善这两个验证环节,可以为市场提供高性能、高可靠性的芯片产品,推动整个行业进步和发展。

3.2 版图布线与光罩(掩模版)制作

版图布线作为芯片设计的核心环节,其复杂性不言而喻。在这一过程中,设计者需要精心规划每一条线路,确保其既能满足功能需求,又能达到最佳的性能指标。

信号完整性:布线过程中必须考虑的重要因素之一,关系到芯片在实际运行中能否稳定、准确地传输信号。

时序问题:合理的时序设计能够确保芯片在高速运行时不会出现时序混乱或信号延迟等问题。

功耗控制:现代芯片设计中越来越受关注的方面,有效的功耗管理不仅可以提高芯片的能效比,还能延长其使用寿命。

| 图名 | 内容 | 备注 |

| 布图规划完成效果图 |

最外一圈为I0PAD,是芯片与外界连接的接口。 图中灰色和绿色的大模块是主要IP。 图中红色和蓝色的线是power stripe,用于连接整个芯片各个位置元件和模块的电源信号和地信号,一般比较宽。 |

布图规划是整个后端流程中作重要的一步,但也是弹性最大的一步。因为没有标准的最佳方案,但又有很多细节需要考量。 布局布线的目标:优化芯片的面积,时序收敛,稳定,方便走线。 |

| 布局完成效果图 |

图中灰色和绿色部分为主要IP。 其余蓝色部分为standard cell(标准单元),通过软件自动布局填充出来的效果。 其中软件会自动留有合适的空间用于下一步的布线。 |

布局即摆放标准单元,I/O pad,宏单元来实现个电路逻辑。 布局目标:利用率越高越好,总线长越短越好,时序越快越好。 但利用率越高,布线就越困难;总线长越长,时序就越慢。因此要做到以上三个参数的最佳平衡。 |

| 布线完成效果图 | 红色和黄色的金属线由软件自动布在standard cell上。 | 布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束条件下,根据电路的连接关系,将各单元和I/O pad用互连线连接起来。 |

| GDSII效果版图 |

与之前相比主要是为了完成时序要求和DRC、LVS要求,重新进行了部分区域的布局布线。" "加入了filler,即填充物以满足设计规则中关于金属层密度的要求。" |

Clock Tree Synthesis,时钟树综合,简单点说就是时钟的布线。 由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。 LVS(Layout Vs Schematic)验证:简单说,就是版图与逻辑综合后的门级电路图的对比验证; DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求; ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气规则违例; 实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题等。 物理版图以GDSII的文件格式交给芯片代工厂(称为Foundry)在晶圆硅片上做出实际的电路。 |

*来源:干货 | 一颗芯片的从无到有-电子工程专辑 (eet-china.com)

在完成版图布线后,接下来的光罩制作环节同样至关重要。

| 名词 | 作用 |

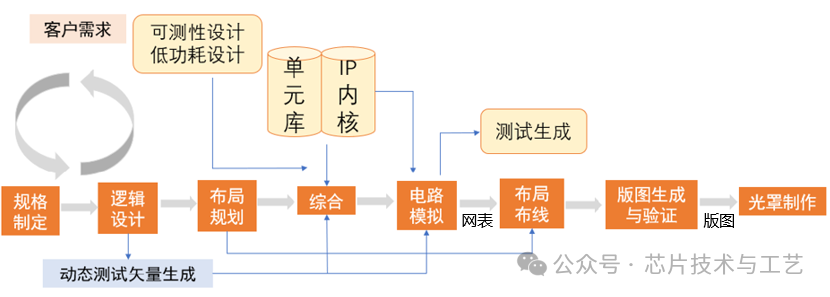

| 客户需求(Customer Requirements) | 定义芯片的功能、性能、接口、电源需求等详细规格,为后续的设计工作提供指导。 |

| 可测性设计(Design for Testability, DFT) | 在设计阶段就考虑电路的可测试性,以便在制造后能够有效地检测和诊断缺陷。 |

| 低功耗设计(Design for Low Power, DLP) | 在设计阶段采用特定的技术来降低芯片的功耗,以满足节能或电池寿命的要求。 |

| 动态测试矢量生成(Dynamic Test Vector Generation) | 在芯片制造后,生成用于测试芯片的动态测试矢量,这些矢量会在芯片的实际测试阶段使用。 |

| 规格制定(Specification) | 定义芯片的功能、性能、接口、电源需求等详细规格,为后续的设计工作提供指导。 |

| 单元库和IP内核(Cell Library & IP Cores) | 提供了设计芯片所需的基本构建块和预先设计好的、可重用的设计组件。 |

| 逻辑设计(Logic Design) | 使用硬件描述语言(HDL)编写代码,实现芯片的功能逻辑。 |

| 布局规划(Floorplanning) | 确定芯片上各个模块的位置和大小,以及它们之间的连接方式,为布局布线打下基础。 |

| 综合(Synthesis) | 将HDL代码转换成门级网表,这是将抽象的硬件描述转换成具体电路表示的过程。门级网表(Gate-Level Netlist)详细描述电路中的逻辑门及其连接方式,为物理设计和时序分析提供输入。 |

| 电路模拟(Circuit Simulation) | 使用仿真工具对设计进行模拟,以验证电路的功能和性能是否符合预期。 |

| 物理布局布线(Layout & Routing) | 将门级网表转换成实际的物理布局,并完成布线,确保信号在芯片上的正确连接。 |

| 版图生成与验证(Mask Generation & Verification) | 生成用于制造芯片的光罩(掩模)图案,并进行验证,确保版图与设计规格一致。 |

| 光罩制作(Mask Making) | 根据验证后的版图制作光罩,这些光罩将在后续的芯片制造过程中用于图案转移。 |

光罩(掩模版),作为将设计图案从虚拟世界转移到现实硅片的桥梁,其制作精度直接关系到芯片的最终质量。

| 下游应用市场 | 产品类型 | 产品应用领域 | 下游应用代表厂商 | 市场占比 |

| 半导体掩模版 | 逻辑电路制造、模拟电路制造、功率器件制造、MEMS传感器制造、IC封装等 | 半导体制造行业 | 台积电、英特尔、中芯国际、华虹半导体、华润微、中芯集成、士兰微、积塔半导体、比亚迪半导体、立昂微、燕东微、高德红外、长电科技等 | 60% |

| 平板显示掩模版 | LCD显示屏制造、OLED显示屏制造等 | 显示技术行业 | 京东方、天马微电子、华星光电、中电熊猫、惠科等 | 28% |

| 电路板(PCB、FPC)制造、触控屏(TP)制造、光学器件制造等 | 电路板制造、触控屏制造、光学器件制造等 | 电子制造行业 | 蓝思科技、紫翔电子等 | 12% |

注:掩模版下游应用市场占比数据来源于SEMI、Omdia。其中,半导体掩模板数据统计的为独立第三方半导体掩模版市场规模,不包括晶圆厂自行配套的掩模版市场规模。

*来源:什么是掩模版?掩模版(光罩MASK)—半导体芯片的母板设计-电子发烧友网 (elecfans.com)

光刻技术在这一环节中发挥着关键作用,它利用光的衍射和干涉原理,将版图上的精细图案精确地投影到硅片上。随后,通过蚀刻等工艺步骤,将这些图案转化为实际的物理结构,从而完成芯片的制作。

随着半导体技术的不断发展,版图布线和光罩制作所面临的挑战也在日益加剧。

布线密度和复杂度增加:随着芯片集成度的不断提高,给设计者带来了巨大的挑战。

光罩制作的精度和效率要求提高:随着市场对芯片性能要求的不断提升,光罩制作面临着更高的要求。

因此,不断探索和创新成为了推动这两个环节技术进步的关键动力。

总的来说,版图布线和光罩制作是芯片流片过程中不可或缺的环节,它们的技术水平和实施效果直接关系到芯片的最终性能和质量。因此,在半导体制造领域,对这两个环节的研究和优化一直是一个热点和难点问题。未来,随着新技术的不断涌现和应用,我们有理由相信,这两个环节将会迎来更多的突破和创新,为半导体行业的发展注入新的活力。

#04

设备与材料

4.1 关键设备

在芯片流片过程中,关键设备扮演着至关重要的角色。这些设备不仅保证了流片过程的顺利进行,还直接影响着芯片的质量和性能。

光刻机:作为流片过程中的核心设备,其精度和稳定性对芯片图形的转移质量有着决定性的影响。现代光刻机采用先进的光学系统和精密的机械结构,能够将版图图案以极高的分辨率投影到硅片上,从而实现微细图形的精确刻画。光刻机还配备先进的对准系统,确保每一次曝光都能准确无误地与硅片上的已有图形对齐,保证芯片结构的准确性和一致性。

蚀刻设备:在流片过程中,蚀刻设备通过化学或物理方法去除硅片表面的特定材料,形成所需的沟槽、孔洞或微细结构。蚀刻设备的性能直接影响芯片的尺寸精度和表面粗糙度,进而影响芯片的电学性能和可靠性。在选择蚀刻设备时,需要充分考虑其蚀刻速率、选择性、均匀性以及对硅片表面的损伤程度等因素。

沉积设备:用于在硅片表面沉积各种薄膜材料的关键设备。这些薄膜材料包括金属、氧化物、氮化物等,它们在构建芯片的内部结构和实现特定功能方面发挥着重要作用。沉积设备的性能直接影响薄膜材料的成分、结构、厚度以及均匀性,从而影响芯片的性能和稳定性。在选择沉积设备时,需要考虑其沉积速率、成分控制、厚度均匀性以及工艺稳定性等因素。

除了上述关键设备外,芯片流片过程中还涉及到许多其他辅助设备和工艺步骤,如清洗设备、检测设备等。这些设备和工艺步骤共同构成了一个完整的流片生产线,确保了芯片从设计到实际产品的顺利转化。

总的来说,关键设备在芯片流片过程中发挥着举足轻重的作用。它们的性能和稳定性不仅影响着流片过程的顺利进行,还直接决定着芯片的质量和性能。因此,在半导体制造行业中,对关键设备的研发和优化一直是一个重要的研究方向。通过不断提升设备的性能和稳定性,可以进一步提高芯片流片的成功率和产品良率,从而推动整个半导体行业的持续发展和创新。

4.2 材料使用

在芯片流片过程中,材料的选择和使用是至关重要的环节。不同的材料具有不同的物理和化学性质,这些性质直接影响着芯片的性能和可靠性。因此,对材料的精心挑选和严谨使用是确保芯片流片成功的关键。

光刻胶:作为芯片制造中的核心材料之一,其性能直接关系到图形转移的精度和分辨率。优质的光刻胶应具有良好的光敏性、粘附性和耐腐蚀性,以确保在光刻过程中能够精确地形成所需的图形掩膜。同时,光刻胶的去除也需要精确控制,以避免对硅片表面造成损伤或残留。

蚀刻气体:在芯片流片中发挥着去除多余材料、形成精细结构的关键作用。不同的蚀刻气体对不同的材料具有选择性,因此需要根据实际需求选择合适的蚀刻气体。此外,蚀刻过程中的温度、压力和时间等参数也需要精确控制,以确保蚀刻的均匀性和准确性。

薄膜材料:在芯片内部电路和互连结构的构建中扮演着重要角色。金属、氧化物等薄膜材料的沉积需要精确控制厚度、均匀性和纯度等参数,以确保芯片内部的电路连接和信号传输的稳定性。同时,薄膜材料的性质和稳定性也直接影响着芯片的可靠性和寿命。

|

半导 体材料 |

细分材料 | 主要用途 | 主要应用环节 | 发展趋势 |

| 制造材料 | 硅片 | 全球95%以上的半导体芯片和器件是用硅片作为基底 | 贯穿制造环节 | 硅片各技术的发展方 |

| 光刻胶及配套试剂 | 用于显影,刻蚀等工艺,将微细图形从掩模板转移到待加工基衬底 | 显影、刻蚀 | 光刻分辨率提高,KrF、ArF、EUV占据主流。 | |

| 电子气体 | 薄膜、刻蚀、掺杂、气相沉积、扩散等 | 薄膜、刻蚀、掺杂、气相沉积、扩散 | 电路线宽不断缩短,对电子气体的纯度要求不断提高。 | |

| 溅射靶材 | 半导体溅射薄膜沉积 | 薄膜沉积 | 铜、钽靶材由于12寸晶圆比重上升,逐步替代铝、钛靶材。 | |

| 高纯试剂 | 芯片的清洗、刻蚀 | 清洗、刻蚀 | 等级要求从G3、G4上升到G4、G5。 | |

| CMP | IC硅片抛光 | 化学机械抛光 | CMP抛光步骤随芯片尺寸的减小而不断增加。 | |

| 光掩膜版 | "底片"转移用的高精密工具 | 光刻 | 掩模板精细化、大型化。 | |

| 封装材料 | 封装基板 | 主要对芯片起到固定、支撑、散热以及连接下层电路板的作用 | 贴片、重组晶圆、切筋/成型 |

先进封装占比将逐步超越传统封装,先进封装材料成为主流。 封装基板已经逐渐取代传统引线框架成为主流封装。 封装基板正朝着高密度化方向发展。 |

| 引线框架 | 承托芯片和外引管脚,连接芯片焊点和引线框架或基板 | 装片、引线键合 | ||

| 键合丝 | 链接芯片焊点和引线框架或基板,以实现芯片和外电路的电气连接 | 引线键合 | ||

| 塑封材料 | 对芯片和引线框架起到密封和保护的作用 | 塑封 | ||

| 芯片粘结材料 | 将芯片与承载体连接的材料,以起到固定芯片的作用 | 贴片、塑封 |

*资料来源:千际投行,资产信息网,中国产业信息网

材料使用在芯片流片过程中具有举足轻重的地位。光刻胶、蚀刻气体和薄膜材料等关键材料的选择和使用都需要经过严格的筛选和测试,以确保芯片的性能和可靠性达到设计要求。同时,随着半导体技术的不断发展,新型材料的研发和应用也将为芯片流片技术带来更多的可能性和挑战。

#05

流片的挑战与解决方案

5.1 设计与成本挑战

在芯片的设计与流片过程中,设计与成本的挑战日益凸显,成为制约行业发展的重要因素。

设计复杂性:随着摩尔定律的延续,芯片上的晶体管数量不断增加,导致电路规模的扩大。这不仅增加了版图验证和布线优化的工作量和技术难度,还要求性能的提升和功耗控制的更高标准。互连线的长度和密度的上升,也使得设计和验证变得更加复杂。

工艺技术进步:高精度要求推动了从深亚微米到纳米级工艺的技术跨越。这对设备精度和材料性能提出了更高要求,导致设备成本上升和材料研发、采购的难度增加。同时,高精度工艺需要更为严格的质量控制,以确保每一个生产环节的稳定性和可靠性,进一步增加了流片的整体成本。

应对策略:

设计环节:通过引入更高效的设计工具和方法,如高级综合、自动布线等,提高设计效率并降低人为错误。采用层次化设计、模块化设计等思想,将复杂系统分解为更易于管理的子模块,从而降低设计的复杂性。

成本控制:优化工艺参数和材料选择是关键。深入研究工艺原理和材料性能,找到性价比更高的工艺方案和材料组合。提高设备利用率、降低废品率等方式也是降低成本的有效途径。加强与供应链合作伙伴的沟通与协作,确保材料供应的稳定性和价格合理性。

设计与成本的挑战是芯片流片过程中不可回避的问题。通过不断创新和优化设计与流片流程中的各个环节,可以有效应对这些挑战并推动半导体行业的持续发展。

5.2 流片失败的应对措施

在半导体制造领域,流片失败可能带来严重的后果,包括资金损失、时间延误,甚至可能影响整个项目的成败。因此,采取有效的应对措施至关重要。

加强设计验证和测试:在设计阶段进行详尽和严谨的仿真测试,以及在实际流片前进行严格的版图验证和时序分析,可以尽可能在设计阶段发现并修正潜在问题,从而显著提高流片的成功率。

与流片厂商的紧密沟通:流片过程中可能遇到各种工艺和设备问题,建立与流片厂商的定期沟通机制,及时反馈和解决问题,对于确保流片的顺利进行至关重要。

建立完善的失败分析和改进机制:即使做了充分的预防和准备工作,流片失败的可能性仍然存在。通过对失败原因的深入剖析,可以找出问题的根源,并据此优化设计和流片流程,从而避免类似问题的再次发生。

降低流片失败的风险需要从多个方面入手,包括加强设计验证和测试、与流片厂商的紧密沟通,以及建立完善的失败分析和改进机制。这些措施的实施,不仅可以提高流片的成功率,还可以为半导体制造行业的持续发展和技术创新提供有力保障。

#06

市场应用与趋势

6.1 应用领域

芯片技术的不断进步使得流片工艺在多个领域内得到了广泛应用,为智能设备的高性能、低功耗和小型化提供了有力支持。以下是几个主要应用领域:

智能设备:智能手机、平板电脑、智能家居等设备中的处理器、存储器和传感器都依赖于先进的芯片流片技术。这些技术确保了设备的高性能和低功耗,同时实现了更小的物理尺寸。

通信领域:随着5G和6G等新一代通信技术的快速发展,对芯片的性能和可靠性提出了更高要求。流片技术的创新为通信基站、网络设备和移动终端提供了高性能的芯片解决方案,推动了通信行业的迅猛发展。

汽车领域:汽车行业正经历电动化、智能化和网联化的变革。芯片作为汽车电子系统的核心部件,其重要性日益增加。流片技术的进步使车载芯片具备更高的集成度、更强的处理能力和更佳的安全性能,助力汽车产业向智能化和绿色化方向发展。

医疗领域:芯片流片技术在医疗设备中的应用广泛,从控制系统到生物传感器的微型化,再到远程医疗和可穿戴设备的普及,芯片技术提供了强大的支持。流片工艺的进步为医疗行业的创新发展提供了技术保障。

总的来说,芯片流片技术已经渗透到现代社会的各个领域,成为推动科技进步和产业升级的关键力量。随着技术的不断发展和市场需求的持续增长,芯片流片技术将迎来更加广阔的发展空间和应用前景。

6.2 市场现状与趋势

全球流片市场目前正处于快速发展和持续变革的阶段。随着科技的飞速进步,尤其是5G、物联网和人工智能等新兴技术的崛起,对高性能、低功耗芯片的需求不断增加,推动了流片市场的蓬勃发展。

1. 市场现状

主要需求地区:北美、欧洲和亚洲。这些地区的半导体产业发达,拥有众多知名的芯片设计公司和先进的制造工厂。

亚洲的崛起:随着全球电子产业的持续迁移,尤其是中国,正在逐渐成为全球流片服务的重要市场和供应基地。

2. 未来发展趋势

技术升级:随着芯片设计复杂性和集成度的提高,流片技术将朝着更高精度和更高效能方向发展。这要求流片服务商不断升级其工艺和设备,以满足日益严格的技术要求。

绿色流片:环保和可持续发展理念的深入将推动绿色流片技术的发展,包括采用更环保的材料和优化工艺流程以减少能源消耗和废弃物排放。

全球协作:全球半导体产业链的深度融合和协同发展将成为流片市场的重要特征。跨国合作和资源共享将有助于降低生产成本、提高生产效率,并推动全球流片市场的持续繁荣。

全球流片市场正面临着前所未有的发展机遇和挑战。服务商需要不断创新,紧跟技术潮流,并满足客户需求,才能在竞争激烈的市场中脱颖而出。

6.3 服务提供商与机遇

在中国,随着半导体产业的快速发展,芯片流片服务提供商的数量和技术水平都显著提升。这些服务提供商包括传统国有大型企业和众多新兴民营科技企业,共同推动了国内芯片设计、制造和封装测试等环节的协同发展。

1. 主要流片服务提供商

中芯国际:作为中国大陆最大的芯片代工厂商,中芯国际在技术实力和生产规模上位居国内前列。

华虹半导体:专注于CMOS影像传感器的研发与生产,拥有多项核心专利技术。

长鑫存储:主要研发和生产DRAM内存芯片,致力于打破国外技术垄断,提升国产芯片的市场竞争力。

2. 发展机遇

国家政策扶持:国家出台了一系列鼓励半导体产业发展的政策措施,包括设立专项基金、建设产业园区、推动产学研合作等,为芯片流片行业提供了良好的发展环境和资金支持。

市场需求旺盛:随着5G、物联网、人工智能等新兴技术的快速发展,对高性能、低功耗芯片的需求日益增加,为芯片流片行业带来了广阔的市场空间。

全球产业格局变化:随着全球半导体产业链的重构和转移,越来越多的国际芯片设计公司将目光投向中国市场,寻求与国内流片服务提供商的合作。这为国内企业提供了与国际先进水平接轨的机会,提升技术实力和国际竞争力。

中国芯片流片行业在服务提供商的共同努力下,正迎来前所未有的发展机遇。未来,随着技术的不断进步和市场的持续扩大,国内流片企业有望在国际半导体舞台上扮演更加重要的角色。

6.4 挑战与政策支持

中国芯片流片行业近年来取得了显著发展,但仍面临着一系列挑战,这些挑战主要来自技术、资金、人才和国际市场环境等多个方面。

1. 技术挑战

尽管中国的芯片设计能力在逐步提升,但与国际先进水平相比仍存在一定差距,尤其是在高端芯片领域,如处理器和存储器等关键技术上。流片技术的复杂性和高精度要求使得技术突破成为一项长期而艰巨的任务。

2. 资金挑战

芯片流片需要大量资金投入,包括研发经费、设备购置和维护费用等。然而,中国芯片产业整体上尚未形成稳定的盈利模式,许多企业在资金筹措上面临困难。

| 工艺类型 | 流片一次的花费(网传) |

| 40nm工艺 | 80万美元 |

| 28nm工艺 | 200万美元 |

| 14nm工艺 | 500万美元 |

| 7nm工艺 | 1500万美元 |

| 5nm工艺 | 4725万美元 |

*来源:摩尔精英

3. 人才挑战

中国虽然拥有庞大的劳动力市场,但具备专业芯片设计和流片技术的人才相对匮乏,这在一定程度上限制了芯片产业的发展速度和质量。

4. 政府支持措施

为应对这些挑战,中国政府采取了一系列政策措施支持芯片流片产业的发展,包括:

财政补贴和税收优惠:降低企业运营成本,提高市场竞争力。

人才培养和引进:通过与高校和研究机构合作,培养更多专业技能人才。

产学研用深度融合:鼓励企业加强与国际先进企业的合作和交流,引进先进技术和管理经验。

这些措施旨在提升中国芯片流片产业的技术水平和创新能力,推动整个产业链的完善和升级。

5. 未来展望

中国芯片流片行业在政府政策支持和产业界共同努力下,有望实现更大突破和发展。通过加强自主研发、优化产业链结构、拓宽融资渠道、加强人才培养和引进等措施,中国芯片流片产业将迎来更加广阔的发展空间和市场机遇。

#06

结 论

本文全面探讨了芯片流片技术及其在半导体制造中的重要性。通过详细讨论芯片设计与流片准备、流片技术的具体细节、设备与材料的使用,以及流片过程中的挑战与解决方案,揭示了流片技术的复杂性和关键性。同时,市场应用与趋势的分析展示了芯片流片技术在全球范围内的广泛应用和持续发展。

在分析中国芯片流片的现状与未来时,本文介绍了主要流片服务提供商及行业面临的机遇,讨论了挑战以及政府的政策支持。通过成功和失败案例的对比分析,总结了流片过程中的经验教训,为未来项目提供了宝贵参考。

总体而言,芯片流片技术是半导体制造中的核心技术,其发展不仅影响芯片设计的实现,也直接关系到半导体产业的竞争力和市场格局。随着技术进步和市场需求增长,芯片流片技术将在未来发挥更加重要的作用,推动半导体行业的持续创新和发展。

参考:

[1] CredenceSystemsCorporation 初次流片芯片的FIB编辑 半导体技术 2005

[2] 晶圆厂,测试芯片,流片 中芯国际与灿芯半导体40纳米低漏电工艺ARM Cortex-A9双核测试芯片成功流片

[3] Kenichi IWATSUKA;K Iwatsuka 3273 Study on micro-groove milling of a microchannel die : Selection guidelines for cutting conditions with micro end mills Proceedings of International Conference on Leading Edge Manufacturing in 21st century : LEM21 2011 10.1299/jsmelem.2011.6.3273-1

[4] 显示芯片 韩国无晶圆厂半导体公司TLi采用Arasan的IP产品实现成功流片 电源技术应用 2015

[5] None 中国首个自主研发5G微基站射频芯片流片成功 半导体信息 2020

[6] 虹识技术 虹识技术成功流片乾芯ASIC芯片QX8001 中国集成电路 2018

[7] 景行 FPGA中多协议I/O接口电路的设计与测试

[8] Shari L. Murray de Diaz Evaluating the impacts of reticle requirements in semiconductor wafer fabrication IEEE Transactions on Semiconductor Manufacturing 2005 10.1109/TSM.2005.858502

[9] 尚鹏 多协议的半导体照明网络VLSI芯片设计 2015

[10] 黄龙 单芯片集成USM驱动电路的关键技术研究与实现 2019

[11] 无 Cadence解决方案助力创意电子20nm SoC测试芯片成功流片 2022

[12] 彭进 28nm SoC芯片设计方法及流程实现 集成电路应用 2016 10.19339/j.issn.1674-2583.2016.05.005

[13] 高勇 新型全数字三相SPWM信号产生芯片的设计与实现 半导体学报 2006

[14] 宁刚玲 以GPU为例的芯片设计制造模式和流程的研究 中国新通信 2023

[15] 李亚会 一款低EMI降压型DC/DC芯片的设计 2014 10.7666/d.D728458

[16] 宋怡曈 基于buffer删除算法的MCU芯片时序优化与修复研究 2022

[17] 李灵 硅基毫米波低噪声放大器研究与设计 2022

[18] O'Neal, Chad Barrett.;CB O'Neal MEMS-based nanomechanical machining system-on-a-chip: Design, fabrication, and functional testing for feasibility. 2004

-

芯片流片失败都有哪些原因2025-03-28 2696

-

芯片设计流片、验证、成本的那些事2024-08-09 4485

-

什么是芯片流片?芯片流片为什么这么贵?2023-11-30 7962

-

芯片流片后需要做哪些工作?2023-09-02 5184

-

为什么芯片流片那么贵2021-08-09 18461

-

STM32库基础知识2021-08-05 1016

-

第5章 PHY芯片和STM32的MAC基础知识2017-10-14 5679

-

电源管理基础知识电源管理基础知识电源管理基础知识2017-09-15 1768

-

LED外延片基础知识2012-01-06 3605

-

通信基础知识教程2010-03-04 982

-

电容基础知识讲座2009-11-30 1278

-

电池过流保护片基本知识介绍2009-11-27 4034

-

led芯片基础知识2009-11-13 3077

-

偏光片的基础知识2008-10-25 5738

全部0条评论

快来发表一下你的评论吧 !