简易数字频率计设计方案汇总(三款简易数字频率计设计原理图详解)

测量仪表

描述

简易数字频率计设计方案(一)

本次设计的数字频率计以AT89C52为核心,在软件编程中采用的是C51语言,测量采用了多周期同步测量法,它避免了直接测量法对精度的不足,同时消除了直接与间接相结合方法,需对被测信号的频率与中介频率的关系进行判断带来的不便,能实现较高的等精度频率和周期的测量。

硬件电路设计方案

多周期同步测量法的基本思路是使被测信号与闸门之间实现同步化,从而从根本上消除了在闸门时间内对被测信号进行计数时的±1量化误差,使测量精度大大提高。倒数计数器就是基于该方法而设计出来的一种具有创新思想的测频、测周期的仪器。它采用多周期同步测量法,即测量输入多个(整数个)周期值,再进行倒数运算而求得频率。其优点是:可在整个测频范围内获得同样高的测试精度和分辨率。

1、系统级方案设计

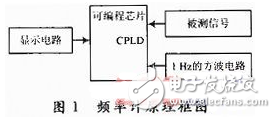

在选择多周期同步等精度测量法的情况下,按照自顶向下的设计方法,可以画出该频率计的系统级框图,如图1所示。根据测周期、频率的原理,可以将总体框图分为三个子系统:输入通道(即前置整形电路)该部分主要由模拟电路组成的;多周期同步等精度频率、周期的测量、控制及功能切换(中间部分),该部分基本上由数字硬件电路组成;单片机及外围电路,包括单片机、数码显示。

2、子系统设计

1.输入通道的设计。输入通道是由前置放大器和整形器组成的,所以要对前置放大器的增益和带宽指标进行估计。为了能准确测量信号,将输入信号经过一个放大整形电路。其具体实施方案为:将输入信号经过LM358运放放大,再通过74LS132整形,此时的信号还不能直接送入单片机,这是因为在硬件上CPU对INT0和INT1引脚的信号不能控制,解决这个问题要通过硬件,再配合软件来解决。

2.预置闸门时间发生电路设计。闸门时间的确定,可以先由一个555定时器产生一个脉冲信号,将555产生的脉冲信号送入到74LS90十进制计数器当中,由于74LS90具有二-五进制混合计数的功能,所以可以用它来实现五进制计数,将74LS90的输出接到3—8线译码器74LS138的输入端,再将译码器的输出端接上五个发光二极管,这样就可以实现硬件上的闸门时间控制。但是考虑到硬件实现上的复杂性,可以通过软件上来实现,就是将五个发光二极管直接接到单片机的P1口由软件上来实现,通过按键来改变它的闸门时间。

3.数码显示电路的设计。该部分电路是由单向八位移位寄存器74LS164和数码管组成的。考虑到精度的问题,取五位计数值,采用五片74LS164级联,同时还要显示频率和周期的单位,所以还需再级联一块74LS164,在74LS164的输出端接六个单位指示灯,分别表示周期频率的三个不同的单位数量级,即周期单位s,ms,μs和频率单位Hz,KHz及MHz。移位寄存器的时钟信号是由单片机的串行输出口TXD脚控制。

简易数字频率计设计方案(二)

频率计原理框图

此频率计的流程为:被测信号fin输入到CPLD芯片,在控制信号为1Hz时,在CPLD芯片里完成对被测信号的测频、计数、锁存、译码,输出信号接数码管显示,如图1所示。

CPLD模块原理框图

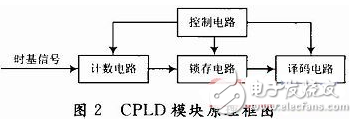

由于是一种集成度很高并且可进行用户定制的数字芯片,因此测试功能都用一块CPLD芯片来实现。在硬件电路设计时,可先将CPLD的内部电路分为控制、计数、锁存及译码四个电路模块分别进行设计,然后再将这四个电路模块有机地结合成一个能完成测频功能的整体系统。其CPLD模块原理框图如图2所示。

控制电路模块

为实现控制功能,控制电路模块需输出三个信号:一是允许对被测信号计数的计数信号CNT-EN;二是将前1s计数器的计数值存入锁存器的锁存信号LOAD;三是为下一个周期计数做准备的计数器清零信号RST-CNT。上述三个信号产生的顺序是:先提供计数信号,这种信号使计数器在1s内计数,即周期为2s的信号;接着是提供锁存信号,这种信号对计数值进行锁存,与计数信号反向;最后是发出清零信号,这种信号可对计数器清零。计数器清零结束后又可重新计数,计数进入第二个周期。控制电路模块实际上是一个控制器,它需要一个周期为1s的信号作为产生并控制控制器输出的时基信号CLKK。控制电路模块中各信号符号及端口功能如图3所示。

计数电路模块

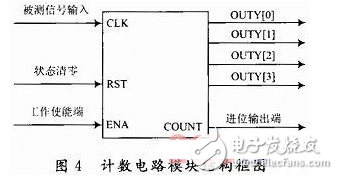

计数电路模块将对被测信号进行十进制计数。它虽然由6个十进制计数器组成,但采用CPLD后,设计时只要先制作单个十进制计数器,然后再将多个结构相同的单个十进制计数器在CPLD内部进行连接就可组合成一个完整的计数电路模块。为实现其功能,十进制计数器需要设置三个输入端:即被测信号输入端CLK、计数器状态清零端RST和计数器工作使能端ENA。

需要设置四个输出端,即OUTY[0],OUTY[1],OUTY[2]和OUTY[3],由这四个输出端输出4位二进制代码来表示十进制数。同时,还需要设置进位输出端COUNT。需要设置四个输出端,即OUTY[0],OUTY[1],OUTY[2]和OUTY[3],由这四个输出端输出4位二进制代码来表示十进制数。同时,还需要设置进位输出端COUNT。设置进位输出端COUNT是因为单个十进制计数器只能表示被测信号频率在个、十、百、千等位中的一个数位的数据。被测信号的频率是从个位计数器开始计数的,被测信号变化一次,个位计数器输出加1,当被测信号变化10次时,个位计数器输出为0,而十位计数器输出加1,当十位计数器计满10次时,十位计数器输出为0,而百位计数器输出加1,依次类推,直至千位、万位或更高位。上述十进制计数器都是满10进1,且进位时计数器清零并重新计数。计数电路模块中的单个计数器符号及端口功能如图4所示。

锁存电路模块

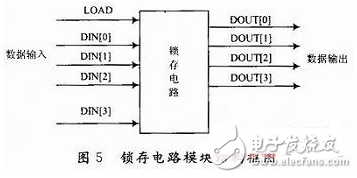

锁存电路模块可使显示电路的工作稳定而可靠,避免计数电路模块清零时引起显示闪烁的现象。锁存电路模块是由多个锁存器组成。每个锁存器都是用来锁存与其单独相连的计数器的输出数据。由于每个锁存器锁存的都是4位二进制代码表示的十进制数,其功能完全相同,因此只需要设计制作一个锁存器就可连接组合成一个锁存电路模块。为实现其功能,锁存器需设置一个使锁存器工作的使能端LOAD,四个数据输入端即DIN[0],DIN[1],DIN[2]和DIN[3],并由它们输入计数器的计数值,还需设置四个锁存数据的输出端:即DOUT[0],DOUT[1],DOUT[2]和DOUT[3]。锁存电路模块中单个锁存器的符号及端口功能如图5所示。

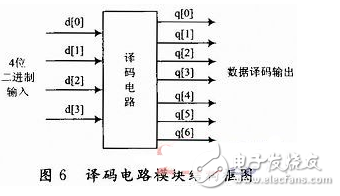

译码电路模块

译码电路模块可对表示十进制数的4位二进制代码进行编码,此模块可直接连接数码管驱动器,从而驱动数码管显示出相应的阿拉伯数字等字符。与锁存器电路模块设计一样,它也只需要先设计一个单个的译码器,然后通过连接组合就可构成译码电路模块,从而实现译码功能。为实现其功能,单个译码器需要设置4个数据输入端:即d[0],d[1],d[2]和d[3],并由这些端口输入锁存电路模块输出的4位二进制数据,需要设置7个输出端:即q[0],q[1],q[2],q[3],q[4],q[5]和q[6],它们分别连接7段数码管的7个显示输入端。译码电路模块中单个译码器符号及端口功能如图6所示。

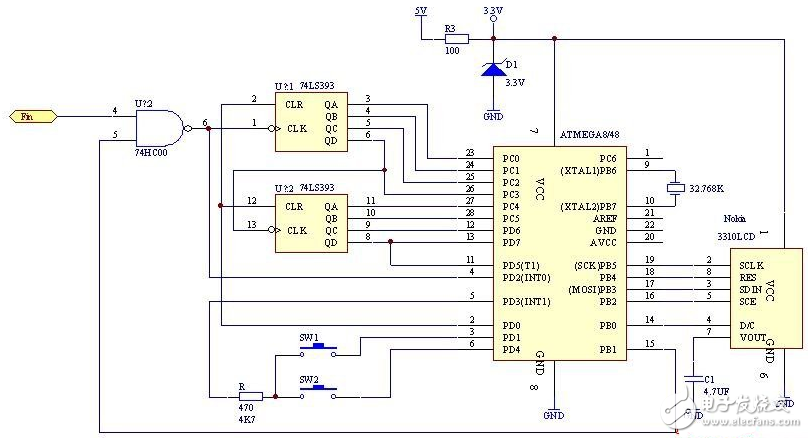

简易数字频率计设计方案(三)

频率计是我们经常会用到的实验仪器之一,本实验要使用单片机和计数电路及液晶器件来设计一个宽频的频率计。

期望达到10Hz-1.1G范围的频率精确测量。

1)计数及显示电路:

2)前置放大及分频电路:

设计思路

频率的测量实际上就是在1S时间内对信号进行计数,计数值就是信号频率。用单片机设计频率计通常采用两种办法,1)使用单片机自带的计数器对输入脉冲进行计数,或者测量信号的周期;2)单片机外部使用计数器对脉冲信号进行计数,计数值再由单片机读取。

由于单片机自带计数器输入时钟的频率通常只能是系统时钟频率的几分之一甚至几十分之一,因此采用单片机的计数器直接测量信号频率就受到了很大的限制。

本实验电路采用方式2,使用一片74LS393四位双二进制计数器和Atmega8的T1计数器组成了24位计数器,最大计数值为16777215。如果输入信号经过MB501分频器进行64分频后再进行测量,则固定1S时基下最高测量频率为1073.741760Mhz。

为了方便得到准确的1秒钟测量闸门信号,我们使用了Atmega8的异步实时时钟功能,采用32.768Khz的晶振由TC2产生1秒钟的定时信号。

测量原理:

单片机打开测量闸门,即PB1输出高电平,同时TC2定时器启动。74LS393开始对输入脉冲进行计数,74LS393每计数达256时,Atmega8的T1计数器也向上计数1次。当1S定时到达时,单片机产生中断,PB1输出低电平关闭测量闸门,然后Atmega8读取74LS393和T1的计数值,然后送LCD显示。

-

小军军军

2019-04-26

0 回复 举报请教 QQ 1052551252 收起回复

小军军军

2019-04-26

0 回复 举报请教 QQ 1052551252 收起回复

-

使用Multisim制作的简易数字频率计电路图免费下载2019-06-19 4871

-

如何进行简易数字频率计的设计分析2019-05-27 2370

-

基于FPGA数字频率计的设计2017-08-04 2128

-

基于Multisim的数字频率计2016-06-21 2591

-

简易数字频率计2016-06-15 2134

-

数字频率计设计论文2016-05-06 1012

-

简易数字频率计设计2015-12-14 1628

-

基于verilog语言的数字频率计设计2015-12-08 1474

-

数字频率计的制作2015-11-20 1282

-

设计简易数字频率计2011-06-28 8057

-

简易数字频率计课程设计报告2010-08-10 2060

-

数字频率计电路图2009-04-11 5983

-

数字频率计测频率的基本原理2008-12-01 4054

-

数字频率计课程设计图2008-04-26 6304

全部0条评论

快来发表一下你的评论吧 !