Xilinx FPGA底层资源架构与设计规范

FPGA/ASIC技术

描述

题主最近开始接触和FPGA的方案验证相关的工作内容,需要把握FPGA内部资源的详细信息,所以又仔细查看了官方的器件手册。这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

参考器件上,虽然一些专用的资源都集中在高端的FPGA型号中,不过题主想了想,还是把它们放在该系列后续的文章中吧。下文中的举证皆来自Spartan6器件文档,所以也不会超出Spartan6涵盖内容。

传统的FPGA内部资源分类作三类,可配置逻辑模块(Configurable Logic Block)、输入输出模块(InputOutput Block)和内部布线资源(Interconnect)三个部分,这些大家都知道的。随着FPGA的发展,为了满足对信号处理和片上储存的需要,又在前三类基础上增加了块RAM(BRAM)、时钟管理单元和硬件乘法器,之后又在部分系列里增加了PPC和高速串行输入与输出等等。

下文将要提到的CLB、SelectIO和Clocking资源里,SelectIO资源是比较丰富的一类,所以在顺序上把它放在最后。

正文:

首先说说CLB吧,它是一类最重要,其实也是最易于使用的结构。Xilinx把尽可能多的资源配置接口开放给用户,但是出于控制开发周期,并且提高系统稳定性的考虑,CLB不是其中之一,它的配置方案几乎全部由IDE实现过程智能分配,用户可以约束特殊Slice的位置,但很少有这种必要,交给IDE来完成会更加有效。

来看看它的结构(有一些图片资料不好找,后期整合的时候会补全):

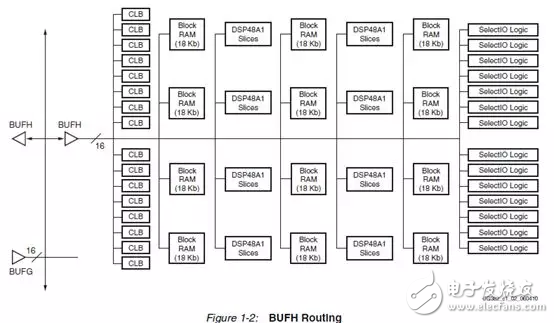

① CLB资源会根据FPGA的尺寸被内部时钟网络分割成若干个区域,一般每个区域是40个CLB单元高度;

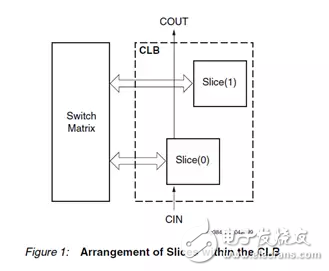

② 每个CLB连接到一个开关矩阵来接入全局布线矩阵;

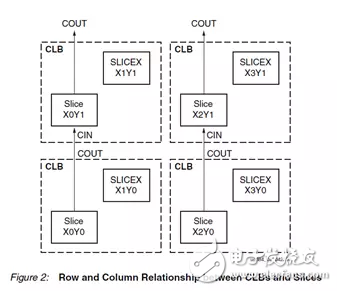

③ 一个CLB单元包含 一对Slice单元(两个Slice无直接连接,并且在CLB间成列分布,每个纵列的Slice有一条独立的进位链);

④ 一个CLB中下方的Slice记为Slice0,上方的记为Slice1;

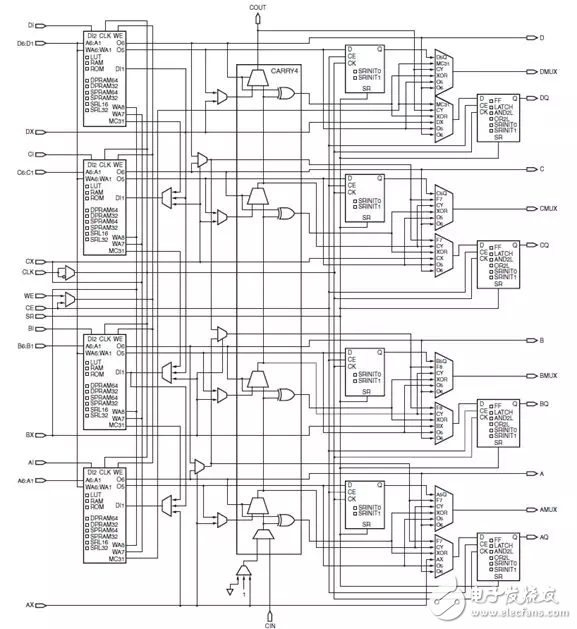

⑤ 每个Slice包含4个查找表(LUTs),8个存储单元(FF),以及一些选择器和进位逻辑,这些单元用于提供逻辑、算术和ROM功能;

⑥ 有一部分Slice支持DistributedRAM和32位移位寄存器功能,被记为SLICEM,其他的记为SLICEL(一个CLB最多有一个SLICEM,每个CLB纵列至少有一个SLICEM,在DSP48E(XilinxFPGA内的硬件乘法器)纵列旁的两个CLB纵列,每一个CLB都有SLICEM)。

SLICEM

(DistributedRAM和ShiftRegisters资源都在LUTs上挂载)

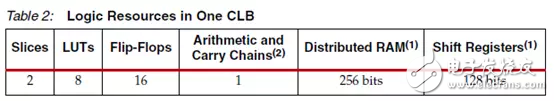

最后看一下一个CLB中的资源总量:

当然具体到Slice中几种资源还有一些细节需要关注,主要是和LUTs的特性相关,不过等后面加入案例来讲吧。如果此前你已经对FPGA设计有一些经验和体会的话,现在想必已经对FPGA的查找表结构有了自己的理解。

还是简单提及一下LUTs的作用,就是查表,,,在我看来,它就是一个6输入2输出的多功能选择器,可以直接把Verilog中always块的行为映射到它的行为上,通过对输入端口的连接配置,它就能够实现我们需要的信号行为模型。完整的过程以后会加入案例来讲。让我们缓一口气,先进入下一个内容。

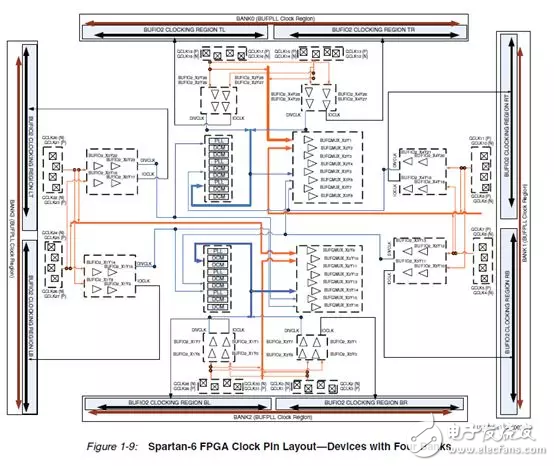

XilinxFPGA内部有复杂的时钟资源网络,来维护大数量逻辑资源条件下的时序要求和系统稳定。主要分为全局时钟线和局部时钟网络,在Spartan6上,还有数字时钟管理器(DCM)和数字锁相环(PLL)两种硬核资源,用以辅助时钟资源网络。Spartan6内部提供了16个全局时钟驱动buffer和40个局部时钟的,它们均匀地分布在上文提到的被时钟网络分割出来的各区域中:

我们可以通过例化BUFG和BUFIO等原语调用这些资源,为GTP(H/X/Z)和DDR、AD/DA这样的高速信号组提供更低相位偏移的时钟参考,但是时钟资源的分配有比较多的使用规则,在资源有限而布线拮据的情况下,时常会被Xilinx规则检查器告知使用违例。之后题主会结合一些真实案例来引导大家去规避这样的错误。

时钟资源所用的篇幅也很短,事实上涉及到时钟的问题很多,但是要在需要的时候再去认识才有价值,不然没有依据的去了解,也没有什么价值。接下来看看FPGA内部最为丰富的I/O资源,毕竟现在市场上FPGA最广泛和最擅长的,就是做接口,下文包含的很多内容,在多个系列的FPGA上都是差不多的规范:

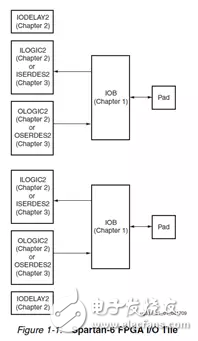

① FPGA的I/O资源被分布在若干个Bank中,每个Bank中有20个I/O Tile;

② 一个Tile包含2个IOB,2个ILOGIC,2个OLOGIC和2个IOEDLAY,用于对双端(差分)信号配对;

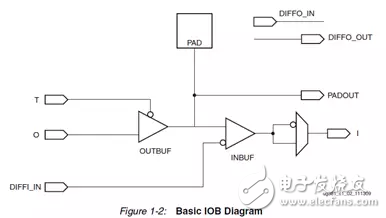

③ IOB包含输入、输出和三态驱动,可配置为不同的I/O标准;IOB直连一对I(O)LOGIC,I(O)LOGIC包含数据I/O的逻辑资源和三态控制,I(O)LOGIC也可以通过调用相关原语配置为I(O)SERDES,实现数据的串并行转换;

IOB单元支持大量的接口标准,可以对负载能力和转换速率进行控制。并且同Bank内支持复合电压输出,以驱动一些低压I/O标准,不过对参考电平的选择有一些规则。

对于单端和双端信号I/O,可以选择很多种buffer配置方式去驱动这些信号,当然IDE的实现过程中也帮我们配置好了很多,作为用户,常用的像IBUFG、IBUFR这样的时钟驱动资源,IBUFDS、OBUFDS实现信号单双端转换,以及用OBUFT实现三态控制等等。

-

Xilinx Ultrascale系列FPGA的时钟资源与架构解析2025-04-24 2915

-

FPGA芯片外围电路设计规范和配置过程2023-08-15 11410

-

Xilinx FPGA时钟资源概述2023-07-24 1598

-

XILINX FPGA IP之Clocking Wizard详解2023-06-12 9384

-

XILINX FPGA 芯片整体架构是如何构成的2021-10-29 3481

-

2012年城市道路工程设计规范资源下载2021-08-11 804

-

华为逻辑电平设计规范 资源下载2021-06-03 1223

-

接地设计规范与指南---PCB接地设计规范2020-08-15 2230

-

PCB设计规范大全2014-10-24 7159

-

华为FPGA设计规范2012-08-17 7065

-

资源分享季 (4)——华为FPGA设计规范及指导2012-07-28 7597

-

电气设计规范2009-06-25 1047

全部0条评论

快来发表一下你的评论吧 !