以太网带宽总是跑不满,是什么原因?

描述

导读

随着网络需求增长,千兆以太网速率问题备受关注。本文针对其实际速率低的情况,详细分析布线不佳等原因,并从等长走线、阻抗匹配等硬件方面及软件调试角度,提供全面提升速率与稳定性的有效方法。

正常的千兆以太网理论速率可以达到1000Mbps,实际考虑到通信各个环节的损耗,也应在800Mbps以上。而实际上却有很多板卡,按照参考电路设计的千兆以太网实测只却只能跑到300/400Mbps,甚至更低。这种情况90%是由于以太网布线不佳导致的信号完整性问题。千兆以太网RGMII信号的速率高达125MHz,而且是双边沿触发的,所以对信号完整性是有要求的。以下的RGMII信号完整性原则和方法,可以帮助优化和改善以太网的速率和稳定性。

1. 等长走线

RGMII在走线时必须要进行等长处理。等长即RGMII总线中的TX_CLK、TXD[0:3]、TX_EN这6个信号为一组,RX_CLK、RXD[0:3]、RX_EN这6个信号为一组,分别绕蛇形走线,使得每组组内信号线之间长度差值在100mil以内,不同厂家的公差要求可能不同,但对硬件工程师来说,条件允许的情况下,公差越小,则时序裕量越大,设计时应尽量将公差缩小。注意这个公差应该是CPU的MAC到PHY芯片的走线,有些核心板的手册标注了核心板RGMII走线长度和CPU内部的长度,此时必须要将它们和底板的长度加起来计算等长。

2. 阻抗匹配

RGMII的所有信号线要求单端50Ω的阻抗匹配,50Ω是一个约定俗成,沿用至今的值,也是板厂熟悉,易于叠层和制板的取值。阻抗匹配指的特征阻抗,定义是:传输线长度趋近于无穷大时,传输线的阻抗是多少(例如上述的50Ω)。在有限长传输线中,它表征电信号经过导体瞬间的阻抗,但这个值不是50Ω,阻抗匹配即有限长传输线中每一处的特征阻抗都是相等的、均匀的、连续的。设计时,它是由PCB的铜厚、线宽、相邻层间距、板材等计算得来的。对设计师来说,最重要的是阻抗的连续性,电信号经过阻抗不连续的导体,如同光线经过密度不同的介质(水和空气)时产生反射与折射,信号就会失真。传输线打孔、换层、经过电阻和连接器的焊盘、有分叉,都会导致不同程度的阻抗不连续。所以layout时应避免分叉、走线改变方向用45度折弯,尽量避免打孔换层。

3. 完整的参考平面

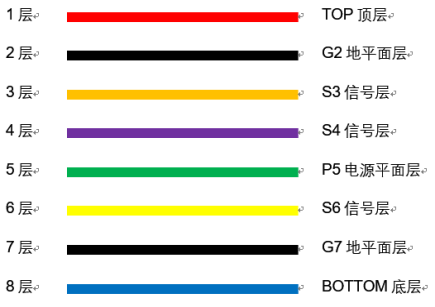

参考平面对阻抗匹配是非常重要的,传输线原理中,传输线包含信号线和回流路径,当信号线是均匀连续的,但参考平面不连续也会导致传输线不连续。参考平面是根据叠层确定的,一般是相邻的平面层,例如图1中,8层板叠层1层和3层参考2层,4层参考5层,6层和8层参考7层。信号线投影区域内参考层的铜皮也不能中断或改变网络。容易出问题的地方是换层的时候如果信号从1层打孔到了8层,那么参考层就从2层变成了7层,建议在信号换层位置200mil范围内打地过孔创造回流路径。有条件的地方也应补上地过孔增强两层地的连续性。那么当信号从1层换层到4层,参考层由GND变成了PWR,网络都改变了,这时该怎么办呢?这种情况可以在换层位置附近布置0.1uF的缝合电容将2层和5层的网络连在一起。

图1 一种常见8层板叠层结构图

4. 避免源端反射

前面讲过阻抗匹配,当信号传输到接收端,RGMII的接收IO是高阻的,信号就会反射回去,反射波到达源端又发生二次反射,叫做源端反射。源端反射会和原始信号叠加在一起形成过冲、振铃等,影响信号质量。通过在靠近信号发送端的位置串联源端匹配电阻,可以有效降低源端反射。有些芯片推荐的匹配电阻是33Ω,有些是22Ω,这是因为芯片管脚驱动器的输出阻抗不同,当驱动器输出阻抗+源端匹配电阻的阻值为50Ω左右的时候,配合50Ω的阻抗匹配,防止源端反射的效果才最好,而这也是串阻要靠近信号源端的原因。

5. 防止串扰

外部的干扰也是不能忽视的,检查诸如走线之间有没有保持3W间距,时钟走线有没有包地。类似图 1.44的叠层中3层和4层的走线有没有和相邻层的其它走线有长距离、近距离的平行走线等等,在这些地方往往也能找到能够优化的点。

6. 软件Delay line调试

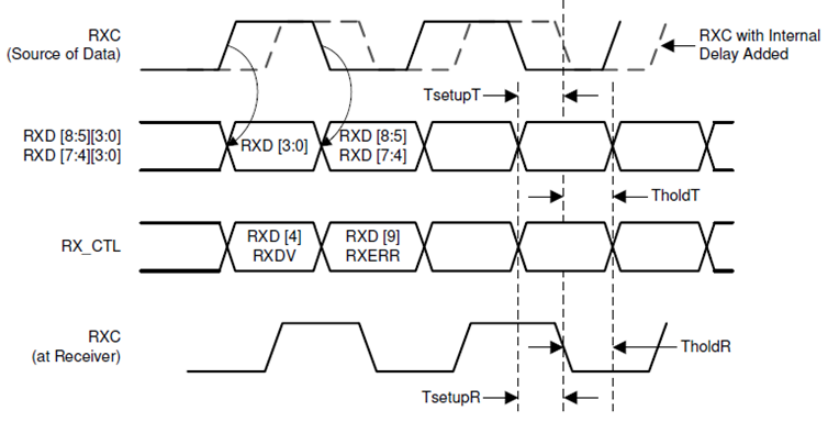

如果板子调试时发现速率不够,其实也不一定就是硬件问题,可以先看下软件有没有进行Delay line的配置。Delay line就是在CLK上增加一段无用的buffer来达到延时的效果,通过调整buffer数量,来补偿PCB走线的延时,最终使得接收端接收到的时钟边沿移动到数据眼图的正中间。一般MAC端和PHY端都可以进行Delay line的调节,但MAC端调节的精度更细,操作也更方便,一般将PHY端的Delay line设为0,只在MAC端调节。

图2 Delay line电路结构示意图

图3 Delay line调整波形示意图

刚开始调Delay line时,网络有可能完全ping不通,同时没法区分是发送有问题还是接收有问题,所以要借助PC端的Wireshark先调试发送数据。MAC端调节Delay line每个步进增加0.08ns延时,待调试的板子在后台ping PC的IP, 输入命令让板子遍历所有TX Delay line,此时观察电脑端的Wireshark,会看到从某个值开始收到板子发来的ICMP包,称为窗口的开始;随着TX delayline逐渐增加,收到的数据包会变得更完整,接着变得不完整,最后彻底收不到板子发来的ICMP包,此时的TX Delay line值称为窗口的结束。取窗口开始和结束的中间值作为此PCB板的TX Delay line最优值,记下这个值。调通板子网卡的发送功能之后,板子就具备了应答ping ICMP包的能力。下面在电脑端绑定板子网卡的MAC地址和IP地址,并开始ping板子的IP地址,板子执行以下命令遍历所有RX Delay line,观察电脑端ping命令的返回信息,会看到ping返回失败,渐渐变成ping成功,而后又变为ping失败,记录下这些节点对应的RX Delay line值。ping成功的这段区间称为接收窗口,同样取其中值,作为RX Delay line的最优值。最后把Delay line最优值设置,添加到设备树的gmac节点中,固化Delay line,完成Delay line的配置。要注意的是,使用RGMII接口连接千兆PHY时,只要硬件存在差别,都需要重新做一次Delay line的配置。另外可以调整Delay line也不代表硬件不需要做等长Layout;如果不做等长,意味着时钟信号的跳变边沿要同时对四条数据线的相位进行延时微调,它们重叠的区域才能对数据正确采样,但这个区域将会变得过窄,甚至超出Delay line延时的范围。

7. 调整驱动强度

除了配置Delay line,还可以调整RGMII的驱动强度进一步改善问题。当使用iperf长时间测试发送会掉线也可以尝试调整驱动强度。当将驱动强度调高时,信号的边沿会变得更陡峭,但与此同时,过冲和振铃也会变强,驱动强度调低时,信号边沿会变缓,但能够减少过冲和振铃的影响。驱动强度通常只有几个档位(通常4或8档),有些厂商会标出是多少mA,有些则只标出强度等级,没有具体单位,所以不用像Delay line那样找最佳值,实测在不同强度下速率最高,稳定性最好的取值即可。

-

FPGA测试DDR带宽跑不满的常见原因及分析方法2025-10-15 1262

-

以太网试验中ping是什么原因?提示无法访问目标主机是怎么回事?2024-05-13 796

-

以太网阻塞的常见原因与解决方法2023-12-27 2919

-

车载以太网基础培训——车载以太网的链路层#车载以太网北汇信息POLELINK 2023-09-19

-

车载以太网快速入门#车载以太网北汇信息POLELINK 2023-09-01

-

以太网是什么鬼?以太网基础知识详解电子学习 2023-02-07

-

DP83848CVV以太网模块link status总是down2022-07-05 9220

-

如何快速分辨以太网与千兆以太网2022-05-06 6388

-

以太网是什么_以太网怎么连接宽带2020-03-20 88296

-

万兆以太网和IP SAN的融合2020-01-24 4293

-

三速以太网2016-10-06 2986

-

以太网与工业以太网的区别2011-12-12 4056

-

LAN到WAN--以太网的飞跃2010-09-25 1322

-

为什么烙铁头总是往上跑锡2010-02-27 5018

全部0条评论

快来发表一下你的评论吧 !