三态门有哪三态_三态门有什么特点

电子常识

描述

三态门的定义

三态门(Three-state gate)是一种重要的总线接口电路。三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态器件。当EN有效时,三态电路呈现正常的“0”或“1”的输出;当EN无效时,三态电路给出高阻态输出。

三态门的应用

如果你的设备端口要挂在一个总线上,必须通过三态缓冲器。因为在一个总线上同时只能有一个端口作输出,这时其他端口必须在高阻态,同时可以输入这个输出端口的数据。所以你还需要有总线控制管理,访问到哪个端口,那个端口的三态缓冲器才可以转入输出状态。这是典型的三态门应用。

三态门的三态介绍及特点

三态是指:高电平、低电平、高阻态。

三态门有三种输出状态:输出高电平、输出低电平和高阻状态,前两种状态为工作状态,后一种状态为禁止状态。值得注意的是,三态门不是具有三种逻辑值。在工作状态下,三态门的输出可为逻辑‘0’或者逻辑‘1’;在禁止状态下,其输出呈现高阻态,相当于开路。

三态门有广泛的应用,利用三态门可以实现线与,也被广泛应用于总线传送。总线传送时,为了保证数据传送的准确性,任意时刻,n个三态门的控制端只能有一个为1,其余均为0,而三态门利用高阻态可以很好的实现这一特性。

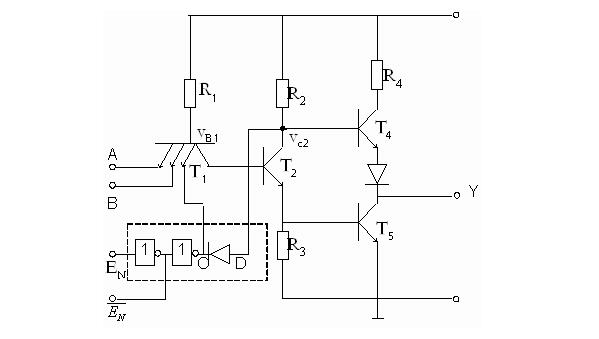

三态输出门电路

上图为三态门输出门电路的原理图。在图中,如果将虚线方框内的两个反相器和一个二极管剪掉,剩下的部分就是典型的TTL与非门电路。

所谓三态是指输出端而言。普通的TTL与非门其输出极的两个晶体管T4、T5始终保持一个导通,另一个截止的推拉状态。T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(vcc)阻抗无穷大。因此这第三种状态也称高阻状态。

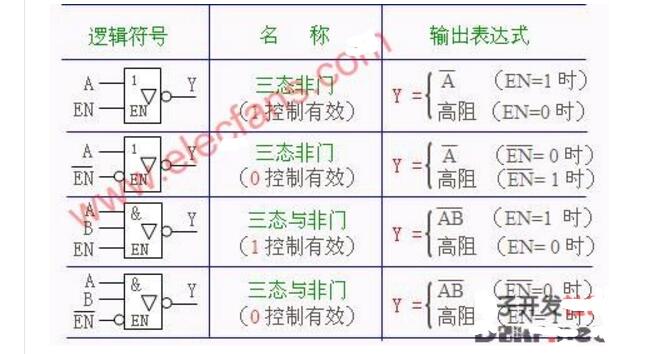

常用三态门的图形符号和输出逻辑表达式

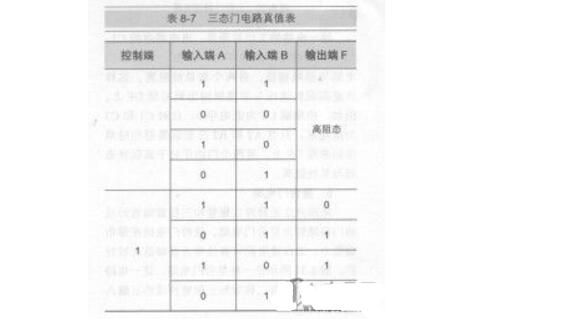

三态门电路的图形符号与真值表

三态门电路的图形符EPM3064ATC44-10N号与真值表。图8-29所示是三态门电路图形符号。三态门电路控制端对门电路控制状态有两种情况:一是控制端为高电平1时,门电路进入高阻状态,此时的三态门电路的图形符号如图8-29(a)所示,控制端C上有一个小圆圈,二是控制端为低电平0时,门电路进入高阻状态,此时三态门电路的图形符号如图8-29(b)所示,这时的三态门电路图形符号中控制端C上没有小圆圈;就是前面介绍的三态门电路。

表8-7所示是三态门电路真值表控制端为0时为高阻态)。

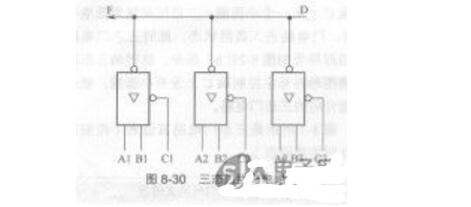

4)三态门线与电路。图8-30所示是采用三态门构成的线与电路,电路中的DF是数据总线,即该线是3个三态门电路共用的数据传输线,该线与电路要实现这样一个功能,即当其中一个三态门通过总线传输数据时,要求其他两个三态门处于关闭状态。电路中的三态门电路在控制端C接高电平时处于高阻状态。

这一电路的工作原理是:当电路中的Cl、C2和C3轮流为低电平时,总有一个三态门电路与总线相连,另两个与总线脱离,这样就能实现轮流按与非逻辑输出到总线DF上。例如,控制端C2为低电平0,此时Cl和C3为高电平,只有A2和B2与非运算后的结果加到总线DF上,另两个门由于处于高阻状态而与总线脱离。

- 相关推荐

- 热点推荐

- 三态门

-

TTL三态门的特点及应用都有哪些呢2024-05-28 6342

-

三态门的工作原理是什么?2021-05-20 3984

-

请教技术大佬 三态门与高阻态是个撒子东西?2021-04-07 3408

-

【梦翼师兄今日分享】 三态门程序设计讲解2019-12-12 3597

-

FPGA之三态门2019-11-29 5133

-

什么是三态电路 三态电路有什么特点2019-05-21 7652

-

三态门怎么理解2019-03-10 19266

-

高阻态与三态门的电路原理分析2019-01-08 7072

-

三态门逻辑电路图大全(三款三态门逻辑电路图)2018-03-01 81558

-

三态门逻辑功能的Multisim仿真方案2011-05-06 2113

-

三态门的组成及工作原理2010-02-28 26681

-

集电极开路门和三态输出门的应用2009-04-07 1518

-

什么是三态门? 三态逻辑与非门电路以及三态门电路2008-05-26 49754

全部0条评论

快来发表一下你的评论吧 !