透射电子显微镜中的应变分析技术

描述

季丰电子材料分析实验室配备赛默飞Talos F200i,设备选配有Epsilon应力分析系统,配合精准的TEM样品制备技术、纳米电子衍射收集参数优化和数据处理方法优化,可快速实现纳米尺度的应变分析。

季丰电子在总部上海、北京、深圳都建有专业的材料分析实验室,欢迎大家咨询、委案!

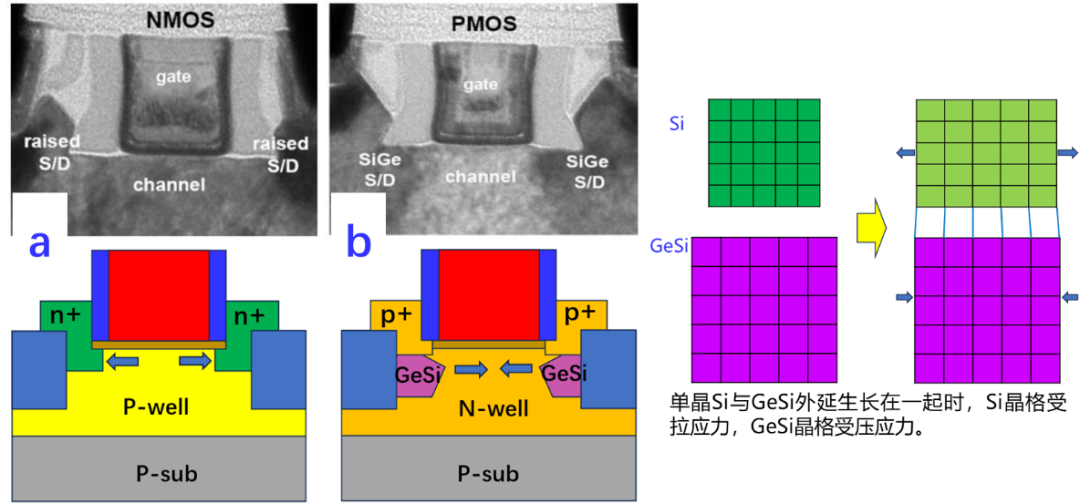

芯片器件中的应力

早在20世纪50年代人们就发现在应变对i本征载流子迁移率影响,随后在20世纪80年代应变Si技术不断被应用于芯片性能改善。应变 Si技术是指通过在传统单晶硅衬度中加入应变材料产生应力,并把应力引向器件的沟道,改变沟道中Si的导带或者价带的能带结构,通过合理的器件设计来获得合适的应力方向从而减小能带谷内、谷间散射的概率以及载流子(电子和空穴)在沟道方向上的有效质量,达到提高载流子迁移率和提高器件速度的目的。

应变Si技术主要包括全局应变硅(GeSi)和局部应变硅技术(GeSi/CoSix/NiSix/TiSix/SiN等)。全局应变硅技术利用Si与SiGex材料具有不同的晶格常数,在晶格常数较大的弛豫Si如岛虚拟衬底上外延生长一薄层Si,得到具有平面双轴张应力的全局应变Si,从而提高PMOS和NMOS载流子迁移率。局部应变Si技术是指在器件某局部区域引入应力,或只在对器件性能起主要作用的沟道位置引入应变,且可调整所引入得应变类型。

随着制程减小带来的器件沟道长度的减小,局部硅产生的应力大小逐渐增加到可与全局应变量相比拟。2002年英特尔公司首次将局部外延嵌入SiGe技术应用于CMOS工艺制程(90 nm)技术中,并由整个业界沿用至今。在 Si NMOSFET 器件中,SiC 是常见的应变材料, SiC 的晶格常数远小于Si,作为外延的源漏区时,可以对横向的沟道产生单轴张应力。

沟道制造在沿[100]晶向上的NMOSFET器件,其沟道方向的电子电导有效质量和散射概率就会降低,电子迁移率增大,从而提高了N-MOSFET器件的性能。而在 Si PMOSFET器件中,通常会嵌入 GeSi 的源漏,GeSi 的晶格常数大于 Si,对横向的沟道会产生压应力,沟道制造在沿[110]晶向上的PMOSFET器件会降低其沟道方向的空穴的电导有效质量,空穴迁移率增大,从而提高了PMOSFET器件的性能。

▲图一

(a) N-MOSFET器件的源极和漏极嵌入 SiC应变材料和(b) P-MOSFET器件的源极和漏极嵌入GeSi应变材料后产生的应力方向。

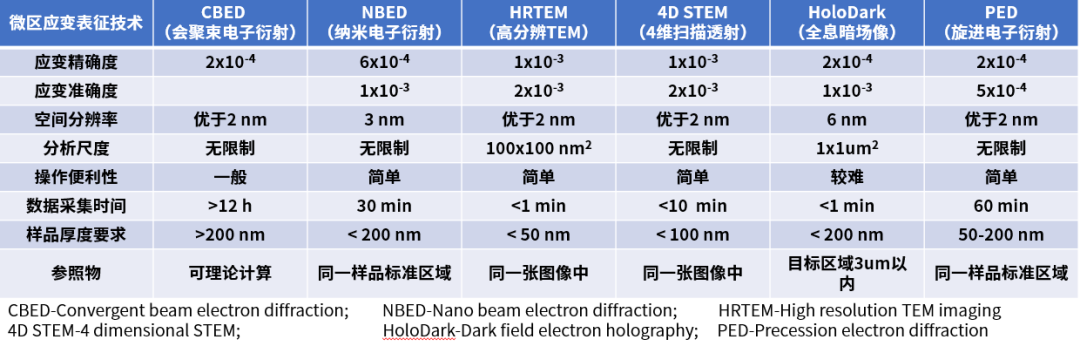

芯片应变表征方法

目前绝大多数芯片中的器件尺寸都小于1 um,最小可到纳米级别,而透射电子显微镜(TEM)的空间分辨率可达0.1 nm,是芯片器件中应变表征的首选工具,其他技术如拉曼、XRD等由于空间分辨率限制,无法用于芯片器件中的应变表征。TEM中的应力表征技术有CBED、NBED、HRTEM、4D STEM、Holography、PED等,这些技术在进行微区应变测试时的技术特点和优缺点如下表所示[1]。

▲表一 TEM中不同应变分析技术对比

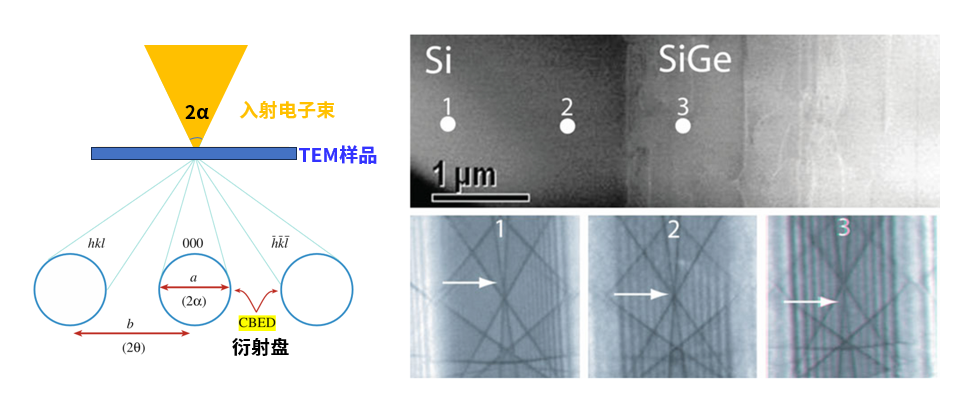

会聚束衍射(CBED)是最早用于应力测试的技术,当入射电子束会聚角足够大时会在衍射平面产生许多高阶劳厄带,这些HOLZ线的定位对材料的晶格参数非常敏感,可以用来高精度地测量应变,正常晶格的HOLZ线非常锐利,而存在缺陷或者应变区域的晶格的HOLZ线会变宽,对于锐利HOLZ 线,可以通过半动力学计算直接根据Hough变换确定的HOLZ线位置来得到晶胞参数,而对于宽 HOLZ 线,可通过复杂的拟合过程确定局部晶格参数,某些对称情况下,亦可通过对实验和动力学模拟的 HOLZ 线图案的两个霍夫变换进行拟合,也可以使用耦合动力学模拟和有限元模拟通过试错来拟合产生应变的界面应力场。

▲图二

左:CBED形成示意图;右:Si-SiGe界面1-2-3三个区域的CBED衍射花样对比,可见HOLZ的位置逐渐变化,且线逐渐变宽。[2]

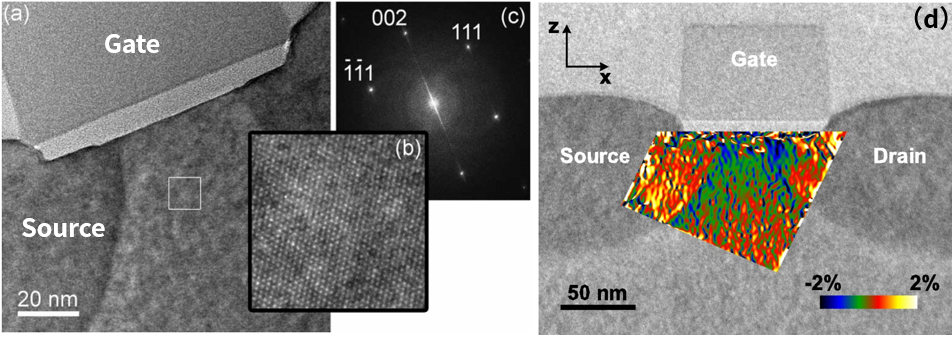

高分辨透射电子显微像(HRTEM)是一种相位衬度像,它是利用平行电子束照射感兴趣的单晶区域会在物镜背焦面处产生包含原子位置信息的衍射花样(傅里叶变换),衍射花样中的入射束和衍射束干涉(反傅里叶变换)会在物镜的像平面处重建晶体点阵的像,通过比较应变区域和正常区域的高分辨像,即可以测量局部应变,目前常用的方法是Hytch等人提出的几何相位分析(GPA),这是一种实空间分析和倒易空间分析相结合的应变分析方法,它是将高分辨像经过Fourier变换,在倒易空间进行应变分析,然后再通过反Fourier变换获得应变在实空间的分布信息。

▲图三

(a)-(c) GeSi源漏极的单晶硅沟道的HRTEM 图像及相应区域的FFT图像;(d) 由图(a)的HRTEM经GPA分析后获得的平行于栅极(εxx)的单晶硅沟道应变分布图 εxx ,显示沟道处Si受到压应力[3]

纳米电子衍射(NBED)技术是指在TEM中通过光路调整获得直径小至2nm的相干性好的电子束,以对尺寸很小的在几纳米至几十纳米的颗粒进行衍射成像,从而实现物相分析。配合专用软件可控制电子束逐点逐行扫描,获得微小区域的纳米电子衍射mapping,通过分析衍射斑点位置的变化趋势,可进一步分析该区域的应力分布情况,其原理是倒空间的衍射点阵参数变化与实空间的晶格参数变化成反比,即如果材料的某部分原子面间距在应力的作用下发生膨胀(收缩)时,对应在倒空间测得的衍射点之间的距离会缩小(扩大)。

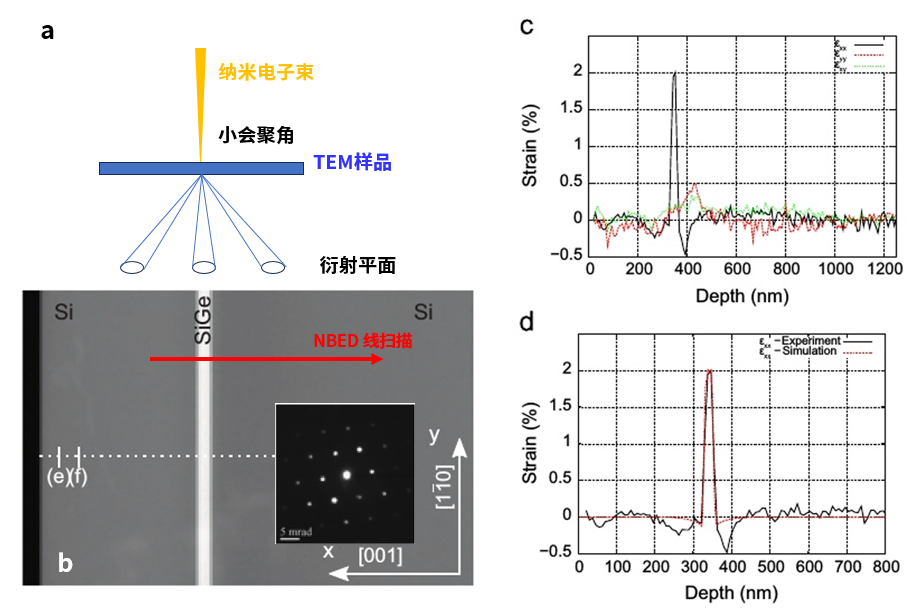

▲图四

(a) NBED形成示意图;

(b) 单晶硅中嵌入SiGe层的STEM图像;

(c)在b图进行NBED线扫描获得的应变结果,显示Si-GeSi界面附近单晶硅中存在X方向的应变,Y方向无应变。

(d) 实验测量的应变分布可与有限元模拟的应变分布结果相比拟,表明NBED测试应变结果比较可靠[1]

四维扫描透射成像(4D STEM)是近年来发展起来的一种成像技术,它是在扫描透射(STEM)模式下电子束会聚成一个极小的束斑照射到样品上并在样品表面进行逐点逐行扫描,在样品下方使用一块具有足够像素数目、高动态范围以及高信噪比的电子探测器来收集所有的散射电子,即采集完整的会聚束电子衍射花样并及时存储到计算机中,即采集扫描区域的衍射mapping(四维数据集),对这个四维数据集的后处理是非常重要,目前已经有一些开源软件能够分析处理4D-STEM数据,如py4DSTEM、pyxem等,或者研究人员可以根据自己的需求来编写程序对数据进行处理分析,从而可以获得材料的虚拟衍射成像、相位、取向和应变分布、样品厚度和倾斜度的测量等信息。4D STEM分析应力的原理与NBED类似,也是利用4D-STEM技术采集一套目标区域的NBED,利用软件可以对材料的应变分布进行精准分析,但是由于4D STEM的衍射图样噪声和强度的复杂性,自动和精确的衍射花样分析仍然具有挑战性。

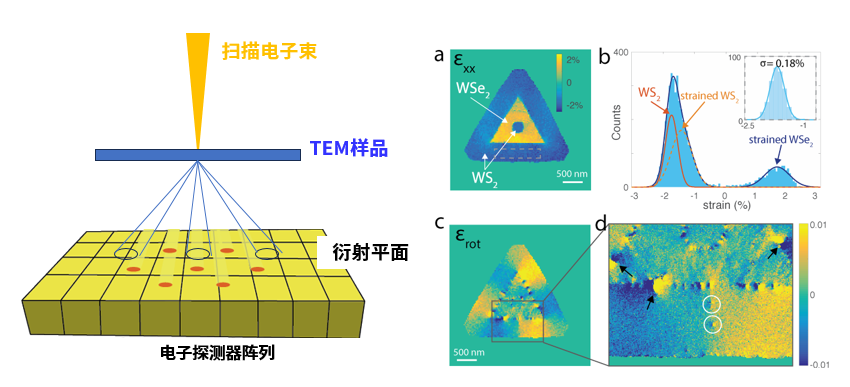

▲图五

左 4D STEM成像示意图;右 WS2/WSe2异质结4D STEM应变分析结果[4]

TEM全息暗场像(Holo Dark)是指在中心暗场衍射条件下利用无应变的完整晶体区域的衍射束作为参考波,与应变区域的衍射束相干涉,得到全息暗场干涉图样,再通过几何位相分析方法计算出应变区的应变分布。利用这种方法可以得到尺度为200nm左右的区域的应变分布,并具有较高的空间分辨率和应变分析灵敏度。

旋进电子衍射(PED)是最近20年发展起来的一种新技术,它是通过围绕电子显微镜的中心轴旋转倾斜的入射电子束透过样品产生衍射花样,在一系列衍射条件下对这些衍射花样进行积分形成PED图案。与普通电子衍射相比,旋进电子衍射有以下特点:一是旋进电⼦衍射花样斑点的⼏何位置不发⽣变化;二是随着旋进⻆度的增⼤,来⾃于⾼⻆度晶⾯的更多衍射花样变为可视,分辨率提⾼;三是旋进电⼦衍射的强度更接近于其运动学数据;四是旋进电⼦衍射对晶体取向缺陷不敏感,这是因为在电⼦束旋进过程中, 其爱瓦尔德球扫掠过倒易空间, 可有效地补偿细小的晶体取向缺陷;由于PED图案的以上特点,其在进行应变分析时应变的准确度和精确度均会比NBED要高得多。

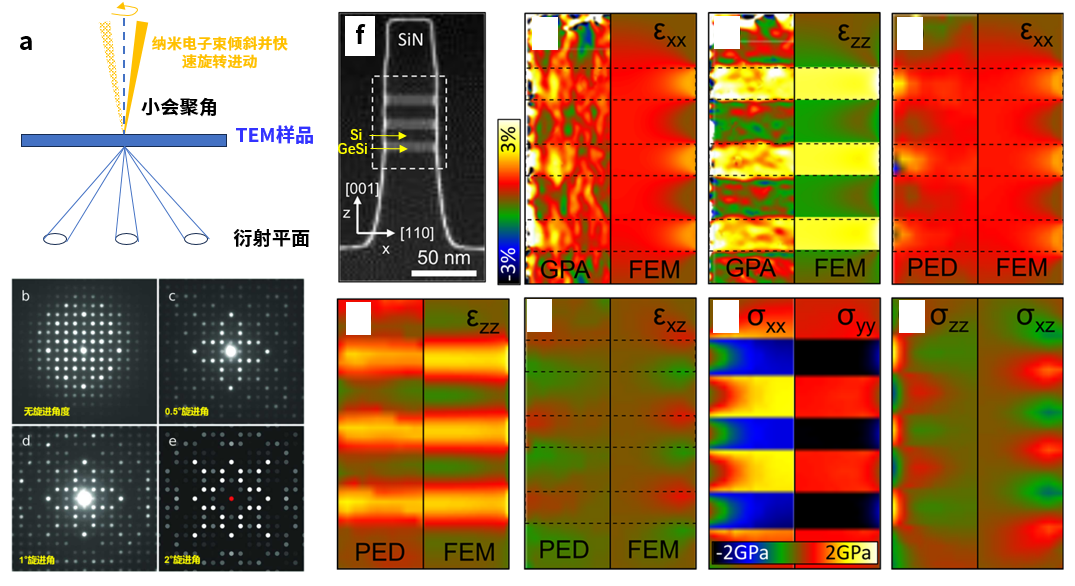

▲图六

a PED原理示意图;b-e 无旋进角度和有旋进角度衍射花样对比;f 基于HRTEM的GPA分析和利用PED技术分析的Si-GeSi异质结构的应变分布[5]

季丰电子

季丰电子成立于2008年,是一家聚焦半导体领域,深耕集成电路检测相关的软硬件研发及技术服务的赋能型平台科技公司。公司业务分为四大板块,分别为基础实验室、软硬件开发、测试封装和仪器设备,可为芯片设计、晶圆制造、封装测试、材料装备等半导体产业链和新能源领域公司提供一站式的检测分析解决方案。

季丰电子通过国家级专精特新“小巨人”、国家高新技术企业、上海市“科技小巨人”、上海市企业技术中心、研发机构、公共服务平台等企业资质认定,通过了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ANSI/ESD S20.20等认证。公司员工近1000人,总部位于上海,在浙江、北京、深圳、成都等地设有子公司。

-

如何选择合适的显微镜(光学显微镜/透射电镜/扫描电子显微镜)2025-09-28 1289

-

什么是透射电子显微镜?2025-05-23 1684

-

透射电子显微镜在金属材料的研究2025-05-22 1238

-

透射电子显微镜(TEM)与聚焦离子束技术(FIB)在材料分析中的应用2025-05-09 1177

-

什么是透射电子显微镜(TEM)?2025-04-25 5099

-

带你一文了解扫描透射电子显微镜2025-04-07 2112

-

透射电子显微镜(TEM)的优势及应用2025-03-25 2401

-

TEM样本制备:透射电子显微镜技术指南2025-01-03 1658

-

透射电子显微镜(TEM):基础知识概览2024-11-06 3131

-

透射电子显微镜的用途和特点2023-08-01 7906

-

【应用案例】透射电子显微镜TEM2023-05-31 2649

-

透射电子显微镜中有哪些主要光阑2020-12-04 15108

-

扫描式电子显微镜 (SEM)2018-08-31 7738

-

透射电子显微镜的结构与成像原理2009-03-06 14078

全部0条评论

快来发表一下你的评论吧 !