8421bcd码转换二进制

电子说

描述

8421BCD码

算机内毫无例外地都使用二进制数进行运算,但通常采用8进制和十六进制的形式读写。对于计算机技术专业人员,要理解这些数的含义是没问题,但对非专业人员却不那么容易的。由于日常生活中,人们最熟悉的数制是十进制,因此专门规定了一种二进制的十进制码,称为BCD码,它是一种以二进制表示的十进制数码。

二进制

二进制是计算技术中广泛采用的一种数制。二进制数据是用0和1两个数码来表示的数。它的基数为2,进位规则是“逢二进一”,借位规则是“借一当二”,由18世纪德国数理哲学大师莱布尼兹发现。当前的计算机系统使用的基本上是二进制系统,数据在计算机中主要是以补码的形式存储的。计算机中的二进制则是一个非常微小的开关,用“开”来表示1,“关”来表示0。

20世纪被称作第三次科技革命的重要标志之一的计算机的发明与应用,因为数字计算机只能识别和处理由‘0’。‘1’符号串组成的代码。其运算模式正是二进制。19世纪爱尔兰逻辑学家乔治布尔对逻辑命题的思考过程转化为对符号“0‘’。‘’1‘’的某种代数演算,二进制是逢2进位的进位制。0、1是基本算符。因为它只使用0、1两个数字符号,非常简单方便,易于用电子方式实现。

8421bcd码转换二进制

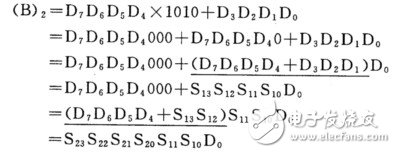

用MSI器件设计。 设两位8421BCD码为D7D6D5D4D3D2D1D0转换后的B码为B685B4B3B2B1B0则

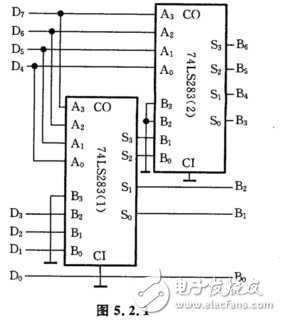

上式中加横线部分都可以用一个MSI加法器实现S为加法器的输出S的下标代表模块序号和输出高低位号。

逻辑图如图5.2.1所示。

[解法2]

VHDL设计。

根据上述解题方法在VHDL程序的结构体设计中可采用结构描述的方法其VHDL主程序如下:

LIBRARY ieee;

USE ieee.Std_logic_1164.ALL; USE work.components.ALL;

ENTITY xiti50 1 IS PORT(d:IN Std_logic_vector(7 downto 0);

b:OUT Std_logic_vector(6 downto 0));

END xiti501;

ARCHITECTURE xiti501_ar OF xitiS01 IS SIGNAL m:Std_logic_vector(3 downto 0);

SIGNAL n1n2:Std_logic;

COMPONENT v74x283 PORT(ab:IN std_logic_vector(3 downto 0);

ci:IN std_logic;

s:out std_logic_vector(3 downto 0);

co:OUT std_logic);

END COMPONENT;

BEGIN u1:v74x283 PORT MAP(‘0’&d(3 downto 1)d(7 downto 4)‘0’mn1);

u2:v74x283 PORT MAP(“00”&m(3 downto 2)d(7 downto 4)‘0’b(6 downto 3)n2);

b(0)《=d(0);

b(2 downto 1)《=m(1 downto 0);

END xiti501_ar;

[解法1]

用MSI器件设计。

设两位8421BCD码为D7D6D5D4D3D2D1D0,转换后的B码为B685B4B3B2B1B0,则上式中加横线部分都可以用一个MSI加法器实现,S为加法器的输出,S的下标代表模块序号和输出高低位号。逻辑图如图5.2.1所示。[解法2]VHDL设计。根据上述解题方法,在VHDL程序的结构体设计中,可采用结构描述的方法,其VHDL主程序如下:

LIBRARYieee;

USEieee.Std_logic_1164.ALL;

USEwork.components.ALL;

ENTITYxiti501ISPORT(d:INStd_logic_vector(7downto0);

b:OUTStd_logic_vector(6downto0));

ENDxiti501;

ARCHITECTURExiti501_arOFxitiS01ISSIGNALm:Std_logic_vector(3downto0);

SIGNALn1,n2:Std_logic;

COMPONENTv74x283PORT(a,b:INstd_logic_vector(3downto0);

ci:INstd_logic;

s:outstd_logic_vector(3downto0);

co:OUTstd_logic);

ENDCOMPONENT;

BEGINu1:v74x283PORTMAP(‘0’&d(3downto1),d(7downto4),‘0’,m,n1);

u2:v74x283PORTMAP(“00”&m(3downto2),d(7downto4),‘0’,b(6downto3),n2);

b(0)《=d(0);b(2downto1)《=m(1downto0);

ENDxiti501_ar;

-

如何实现二进制和BCD码数据的相互转变?2024-02-18 6366

-

请问bcd码和二进制有什么关系?2023-10-07 746

-

在FPGA中实现一种二进制转BCD码的电路设计2022-07-12 4558

-

8421BCD码与二进制原码的相互转换2022-01-17 1840

-

如何利用二进制数实现BCD码的转换2018-05-19 29136

-

函数转换BCD编码二进制数为整型数2018-03-14 7284

-

余3码至8421BCD码的转换_8421BCD码转换成余3码2018-03-02 200888

-

bcd码和二进制码有什么区别2017-11-24 42314

-

【小梅哥FPGA进阶教程】第二章 二进制转BCD2017-01-09 5343

-

关于两位十进制数转换成二进制数的仿真 求助啊2016-07-01 9086

-

什么是BCD码、8421码、余三码、格雷码2011-11-03 27720

-

智能仪表多字节二进制数转换BCD码2011-06-23 1629

-

二进制与BCD码转换资料2010-08-19 2502

全部0条评论

快来发表一下你的评论吧 !