32768晶振电路图大全(五款32768晶振电路图设计原理图详解)

IC应用电路图

描述

32768晶振电路图(一)

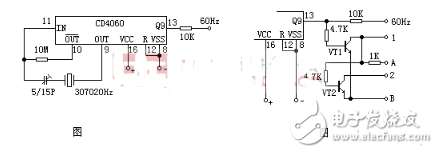

电路中,CD4069的门I和门II构成震荡频率为32768Hz的晶体振荡器。其输出经CD4069的门III整形后送至CD4040的端。CD4040的输出由二极管VD1~VD3置成分频系数为21+25+29=546,经分频后在输出端Q9上便可输出一个60Hz的时钟信号供给数字钟集成电路。图2a是另一种60Hz脉冲发生电路。

它由集成电路CD4060和谐振频率为30720Hz的晶振等元件组成。CD4060是14位二进制串行计数、分频器和振荡器。CD4060内部分为两部分,其中一部分是14级计数/分频器,其分频系数为16~16348;另一部分既可与外接电阻和电容构成RC振荡器,又可与外接晶体构成高精度的晶体振荡器。

本电路采用外接30720Hz的晶振来组成晶体振荡器,其振荡信号经CD4060内部9次分频后,在Q9端输出准确的60Hz频率信号(30720÷29=60Hz)。该电路与双阴型数字钟配用时,可采用图2b电路进行极性转换。VT1、VT2选用NPN型三极管,如9013、8050等,图中A端接正电源,B端接电源负端。

该电路与双阳型数字钟配用时,VT1、VT2选用PNP型三极管,如9012、8550等,图中A端接负电源,B端接电源正端。

32768晶振电路图(二)

555定时器构成多谐振荡的秒信号产生电路

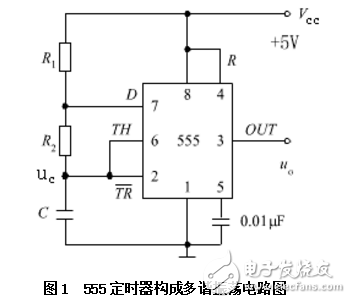

555定时器是一种集模拟、数字于一体的中规模集成电路,其应用极为广泛。利用它可以很容易地接成施密特触发器、单稳态触发器和多谐振荡器,秒信号产生电路就是选用555定时器构成多谐振荡器。原理图如下图1。

工作原理:

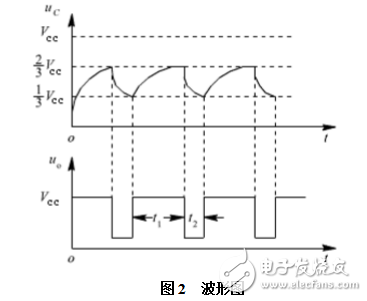

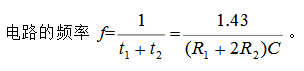

接通电源后,电容C被充电,当uc上升到2/3Vcc时,使uo为低电平,同时放电三极管T导通,此时电容C通过R2和T放电,uc下降。当uc下降到1/3VCC时,uo翻转为高电平。电容放电所需时间为:t2=R2Cln2≈0.7R2C;电容充电时间t1≈(R1+R2)Cln2≈0.7(R1+R2)C;波形如图2所示。

本例选用R1=R2=10KΩ,C选47µF。即可在输出端uo得到频率为1Hz的秒时钟信号。

本电路的优点是制作线路简单,成本不高,调节电阻R1可以调节频率,可调节占空比。缺点是由于占空比是可调的不是标准的方波,波形失真较大,且频率的稳定性差。适用于频率精度要求不高的工作场所。

32768晶振电路图(三)

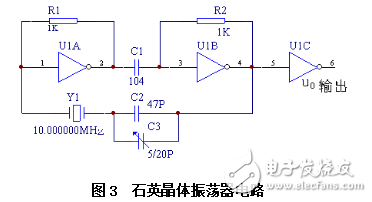

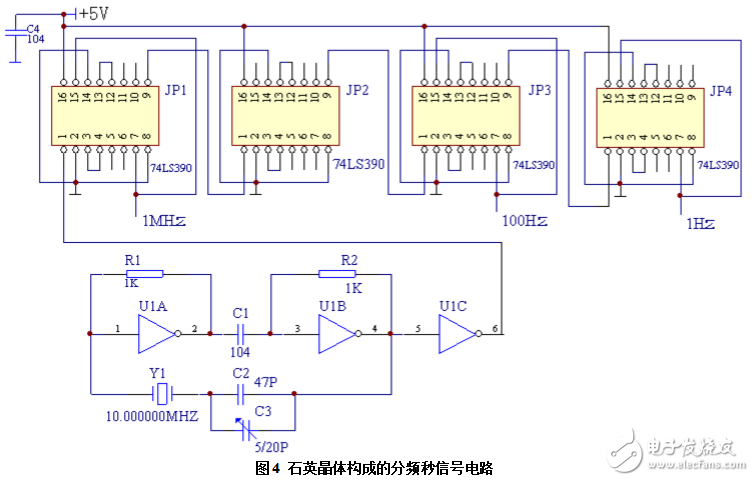

石英晶体主要成分是二氧化硅,它的物理化学性质十分稳定,Q值很高,可达104~106,选频特性非常好,构成的振荡器电路有一个极为稳定的串联谐振频率。电路的振荡频率取决于石英晶体的振荡频率。本例用二级反相器与石英晶体组成多谐振荡器。电路如图3示。R1、R2的作用是使U1A、U1B工作在线性放大区,C1的作用是正反馈耦合,晶振的作用是选频。本例的选用的晶振频率是10.000000 MHz的晶片。因此本振荡器的频率为10.000000 MHz。

要获得1 Hz的秒信号必须要对10 MHz的晶振信号进行多次分频,本例是采用74LS390 双十进制计数器进行分频,图4是石英晶体构成的分频秒信号电路。

本电路的显著优点是频率稳定性极好,可达1.000000 Hz的精确度,若想得到高的频率稳定度,可采用辅助温度补偿电路,10.0 MHz的频率稳定度可达到1-2个PPm,且波形失真小。该电路的唯一缺点是线路稍复杂,制作成本略高。适用于对秒信号要求十分严格的电路中,如高精度数字式频率计中的计数闸门。

32768晶振电路图(四)

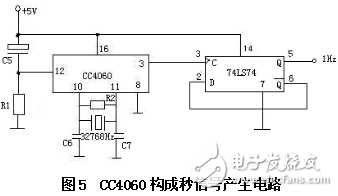

14级二进制串行计数器/分频器CC4060由两部分组成,一部分是14级分频器,另一部分是振荡器。振荡器外接用电子表的石英晶体,构成频率为32768 Hz(=215)的振荡器,32768 Hz经过CC4060十四级分频后为2 HZ,再经过一个D触发器组成的T’触发器二分频,就得到1 HZ秒信号,D触发器选用74 LS74。电路如图5所示。其中R2为直流负反馈电阻,使CC4060内部与非门工作于传输特性的线性转折区,本例取2 MΩ。C6,C7用于稳定振荡,本例取100 pF。R1C5组成上电复位电路,在接通电源瞬间产生一个微分脉冲,使CC4060输出清0,分别取10 kΩ、10 µF。

本方案电路的优点是电路简单,制成容易,成本较低,且频率的准确度也较好。可作为时钟电路的秒信号源,但其频率稳定度不及上一种电路。

32768晶振电路图(五)

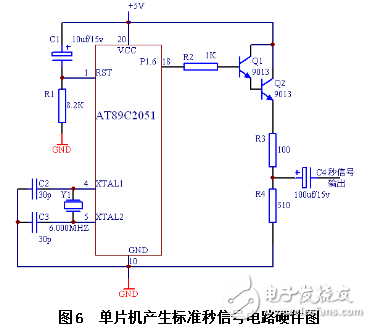

用单片机产生标准秒信号的优点是硬件电路简单,可靠性好,输出波形好,且频率稳定度与晶体相同。

但由于是利用单片机内部的计数器进行自动计数器,且必须靠“中断”服务程序来实现秒信号的生成,由于CPU对中断响应时间的不确定性的关系,因而每个秒周期均存有数微秒的时间延迟,倘若对其进行适当的软件补偿并反复进行修正调试,也可使延迟时间减至最小,从而也可获得更加精确的秒信号,且可获得晶振级的频率稳定度。

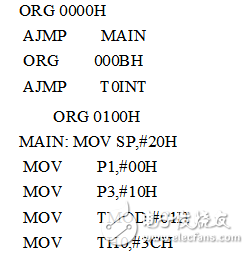

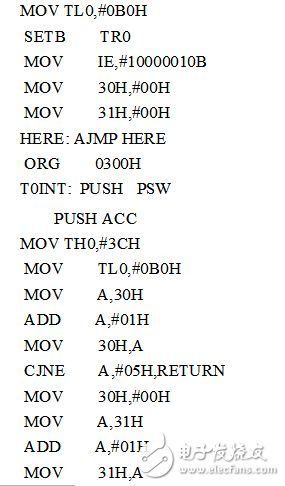

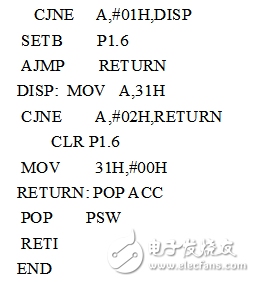

用单片机产生标准秒信号的电路很简单,凡是具有“定时/计数”功能的单片机均可胜任,现以AT89C2051单片机为例,其硬件电路如图6所示。

电路组成说明:由C1R1组成单片机上电复位电路,由C2C3和6.000 MHz晶体组成单片机时钟振荡电路,由R2Q1Q2R3R4和C4组成秒信号输出电路,单片机的P3.4(T0)口用作定时器。AT89C2051实现秒信号输出的汇编程序如下:

-

差分晶振电路图如何制作 影响差分晶振价格的原因2024-01-23 1395

-

32768晶振有什么用处2021-07-27 2274

-

一张图看尽晶振家族,32768晶振设计误区与误解资料下载2021-04-03 2043

-

32768晶振要求配15pF电容吗?2021-02-24 3550

-

32768晶振不起振应该如何解决2020-08-15 12178

-

有源晶振EMC设计的标准电路图免费下载2020-07-14 1498

-

四脚有源晶振电路图2019-11-26 42449

-

32768晶振实现秒信号2018-03-02 21658

-

32768晶振全系列技术详解(32768晶振误差与32768用于BLE)2018-02-27 35114

-

电路图晶振符号2017-04-10 7988

-

555组成晶振电路图2009-05-16 2605

-

晶振检验电路原理图2008-10-16 6647

全部0条评论

快来发表一下你的评论吧 !