格雷码转和8421码的相互转换

电子说

描述

格雷码属于可靠性编码,是一种错误最小化的编码方式。因为,虽然自然二进制码可以直接由数/模转换器转换成模拟信号,但在某些情况,例如从十进制的3转换为4时二进制码的每一位都要变,能使数字电路产生很大的尖峰电流脉冲。而格雷码则没有这一缺点,它在相邻位间转换时,只有一位产生变化。它大大地减少了由一个状态到下一个状态时逻辑的混淆。由于这种编码相邻的两个码组之间只有一位不同,因而在用于方向的转角位移量-数字量的转换中,当方向的转角位移量发生微小变化(而可能引起数字量发生变化时,格雷码仅改变一位,这样与其它编码同时改变两位或多位的情况相比更为可靠,即可减少出错的可能性。

格雷码是一种绝对编码方式,典型格雷码是一种具有反射特性和循环特性的单步自补码,它的循环、单步特性消除了随机取数时出现重大误差的可能,它的反射、自补特性使得求反非常方便。

由于格雷码是一种变权码,每一位码没有固定的大小,很难直接进行比较大小和算术运算,也不能直接转换成液位信号,要经过一次码变换,变成自然二进制码,再由上位机读取。

典型格雷码是一种采用绝对编码方式的准权码,其权的绝对值为2^i-1(设最低位i=1)。

格雷码的十进制数奇偶性与其码字中1的个数的奇偶性相同。

8421码转格雷码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY B2G IS

GENERIC(n:INTEGER :=4);

PORT(

norm : IN STD_LOGIC_VECTOR(n-1 DOWNTO 0);

grey : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0)

);

END B2G;

ARCHITECTURE behave OF B2G IS

SIGNAL temp_normal : STD_LOGIC_VECTOR(n-1 DOWNTO 0);

SIGNAL temp_grey : STD_LOGIC_VECTOR(n-1 DOWNTO 0);

BEGIN

PROCESS(norm)

BEGIN

temp_normal 《= norm;

temp_grey(n-1) 《= temp_normal(n-1)

FOR i IN n-2 DOWNTO 0 LOOP

temp_grey(i) 《= temp_normal(i+1) xor temp_normal(i);

END LOOP;

grey 《= temp_grey;

END PROCESS;

END behave;

数码管显示器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY seg7_1 IS

PORT(

A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END seg7_1

ARCHITECTURE seg7_1 _arch OF seg7_1 IS

BEGIN

PROCESS(A)

BEGIN

CASE A IS

WHEN“0000”=》B《=“1111110”; --0

WHEN“0001”=》B《=“0110000”; --1

WHEN“0010”=》B《=“1101101”; --2

WHEN“0011”=》B《=“1111001”;--3

WHEN“0100”=》B《=“0110011”;--4

WHEN“0101”=》B《=“1011011”;--5

WHEN“0110”=》B《=“1011111”; --6

WHEN“0111”=》B《=“1110000”; --7

WHEN“1000”=》B《=“1111111”; --8

WHEN“1001”=》B《=“1111011”; --9

WHEN OTHERS =》B《=“0000000”;

END CASE;

END PROCESS;

END;

四人多数表决器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY biaojueqi IS

PORT(

A3,A2,A1,A0:IN STD_LOGIC;

Y :OUT STD_LOGIC);

END biaojueqi;

ARCHITECTURE behave OF biaojueqi IS

SIGNAL comb :STD_LOGIC_VECTOR(3 DOWNTO 0);

signal d: STD_LOGIC_VECTOR(15 DOWNTO 0);

BEGIN

comb《=A3&A2&A1&A0;

PROCESS(comb)

BEGIN

CASE comb IS

WHEN“0111”=》Y《=’1’;

WHEN“1011”=》Y《=’1’;

WHEN“1101”=》Y《=’1’;

WHEN“1110”=》Y《=’1’;

WHEN“1111”=》Y《=’1’;

WHEN OTHERS =》Y《=‘0’;

END CASE;

END PROCESS;

END behave;

格雷码转和8421码的相互转换

用与非门74LS00和异或门74LS86设计一可逆的4位码变换器 设计要求:在控制信号C=1时,将8421码转换为格雷码;C=0时,将格雷码转换为8421码;写出设计步骤,列出码变换关系真值表并画出逻辑图,并用multisim进行仿真

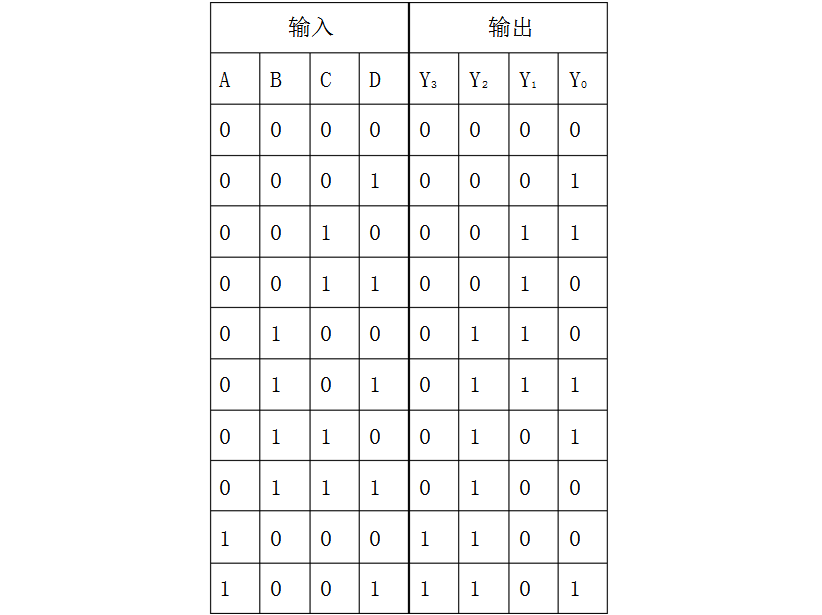

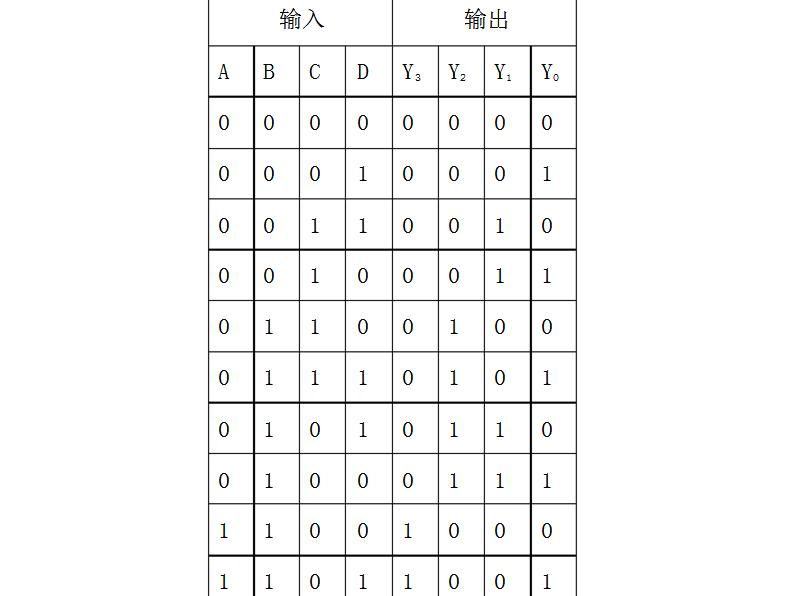

解:根据组合逻辑电路的设计方法设输入变量分别为A,B,C,D输出变量分别为Y3,Y2,Y1,Y0;高电平用“1”表示,低电平用“0”表示。 (1)列出真值表

当C=1时将8421码转换为格雷码

当C=0时将格雷码转换为8421码

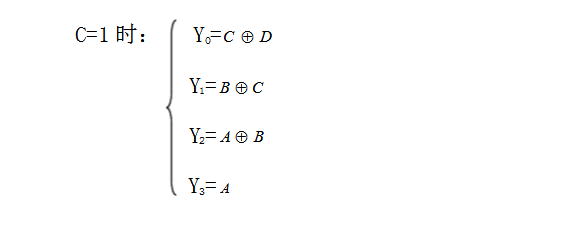

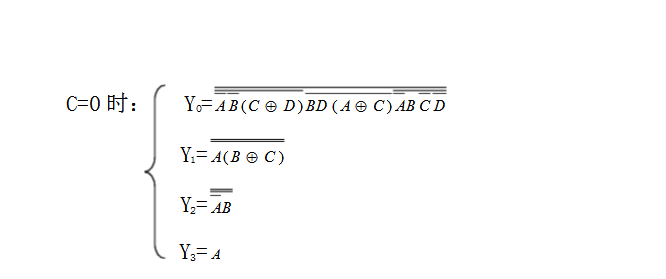

(2)根据真值表写出逻辑函数表达式并化简

(3)根据化简后的逻辑函数表达式设计出实现该逻辑功能的数字逻辑电路

-

8421BCD码与二进制原码的相互转换2022-01-17 1840

-

如何把二进制转换为格雷码?格雷码是如何判断读空写满呢?2018-09-15 9073

-

余3码至8421BCD码的转换_8421BCD码转换成余3码2018-03-02 200845

-

什么是BCD码、8421码、余三码、格雷码2011-11-03 27689

-

二进制代码与格雷码相互转换2010-05-02 1782

-

格雷码简介及格雷码与二进制的转换程序2009-01-16 5422

全部0条评论

快来发表一下你的评论吧 !