常用的译码电路有哪些

数字电路图

描述

1、继电器译码电路

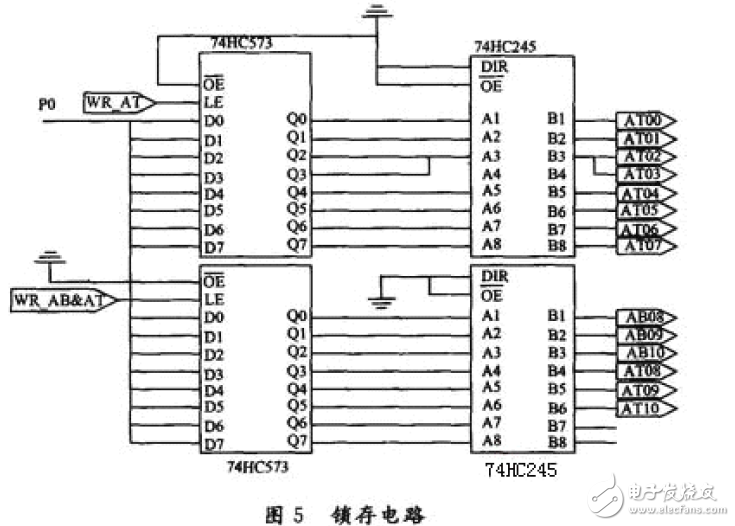

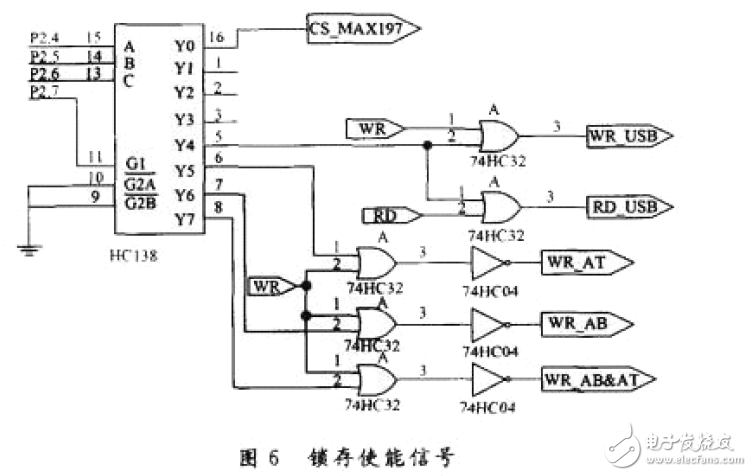

继电器译码电路的作用是在单片机的控制下将1 536个测试点中的某两个测试点接入相应的测试电路。比如译码电路选中测试点1的输入继电器Kat和测试点2的输出继电器Kab,外部的被测电缆通过这两个测试点接入相应的测试电路,从而实现了导通或者绝缘测试。为了实现这样的功能译码电路可以分为地址锁存电路,输入继电器译码电路和输出继电器译码电路。以输入地址锁存电路为例,其原理如图5,图6所示。

单片机P0口作为数据总线将地址信号送给锁存器74HC573,同时P2.4,P2.5,P2.6,P2.7驱动HC138译码器形成锁存有效信号,使地址信号锁存在74HC573,由于地址信号为11位,所以需要单机发送两次地址信息。当11位地址准备完毕后,由单片机发送地址有效信号,将地址信号送给译码电路。

输入继电器译码电路和输出继电器译码电路具有相同的电路结构,以输入继电器译码电路为例,可以分为三级译码电路,每一级译码电路由总线隔离芯片74HC245,3~8线译码器74HC138和其他逻辑控制电路组成。第一级译码电路由11位地址信号中AT10,AT09,AT08,AT07组成,负责选择12块单板中的某一块;第二级译码电路由AT06,AT05,AT04,AT03组成,负责选择某块单板中的某一行;第三级译码电路由AT02,AT01,AT00组成,负责选择某块单板中的某一列,这样行列交叉就选中某一个测试点的输入继电器驱动电路,从而将该测试点接入了测试电路。地址信号在单板与单板之间经过74HC245的隔离,防止其驱动能力下降。

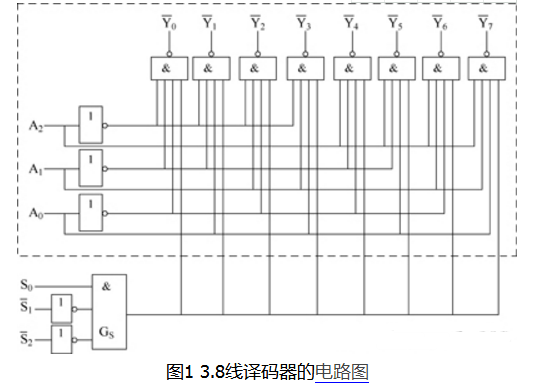

2、3.8线译码器电路

74LS138是一种集成的3-8线译码器芯片。它的逻辑电路如图1所示。

从图1可以看出,74LS138电路除了双点画线框内的译码电路外,还包含了由GS门组成的控制电路部分。

74LS138有3个附加的控制端S0、S1、和S2。当S0=1、/S1=/S2=0时,GS输出为高电平(1),译码器处于正常工作状态;否则,译码器被禁止,所有的输出被锁定在高电平。这3个控制端又称“片选”输入端,利用片选的作用可以将多片连接起来以扩展译码器的功能。

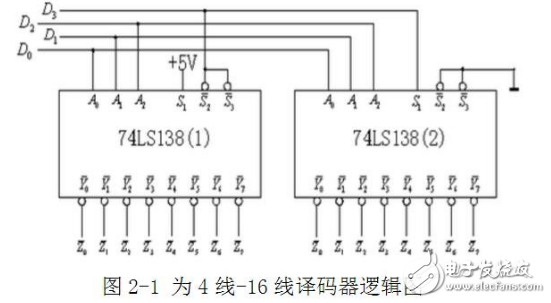

3、4线16线译码电路

在输入端输入D3、D2、D1、D0相对应的二进制编码(0/1),通过译码器“翻译”得出输出端的结果 Y0-Y15,如:当D3、D2、D1、D0分别为1010时,输出端为Y10(10)。

工作原理

用两片3线-8线译码器&TImes;138构成4线-16线译码器的逻辑图如图2-1所示。利用&TImes;138(1)的控制端S1’、S2’与&TImes;138(2)的控制电路S1相连,接入四位输入D0、D1、D2、D3的最高为A3可以完成译码器的扩展。当D3=0时,&TImes;138(1)工作,而×138(2)处于禁止状态,输出为高电平;而当D3=1时,×138(2)工作,×138(1)处于禁止状态。×138(1)输出为Y0’~ Y7’×138(2)输出为Y8 ~ Y15。

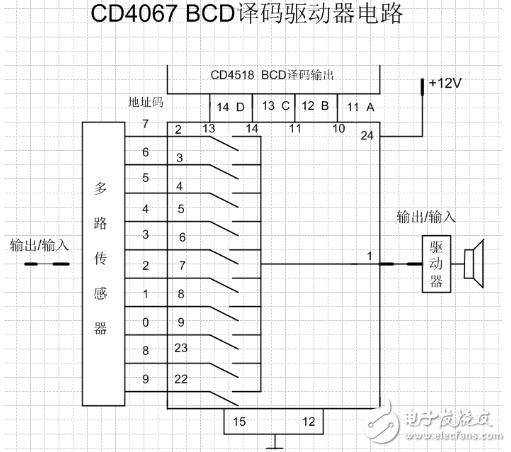

4、BCD译码驱动器电路

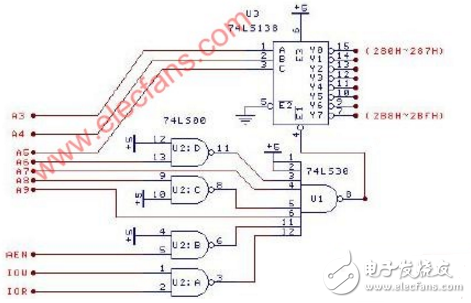

5、IO接口地址译码电路

如图所示地址空间280H~2BFH共分8条译码输出线:Y0~Y7 其地址分别是280H~287H、288H~28FH、290H~297H、298H~29FH、2A0H~2A7H、2A8H~2AFH、2B0H~2B7H、2B8H~2BFH,8根译码输出线在实验台I/O地址处分别由自锁紧插孔引出供实验选用。

-

常见译码器工作原理介绍2023-04-26 8729

-

这三本PCB我觉得可以看看,常用电源电路,常用驱动电路,常用控制电路,常用控制电路里面甚至有飞控2022-01-10 1111

-

地址译码电路设计实验报告2018-03-02 12299

-

译码器,译码器是什么意思2010-03-08 5880

-

计数/译码显示电路2009-12-20 6005

-

ADPCM编译码系统电路2009-10-11 1712

-

简易编、译码电路图2009-05-27 1453

-

4017译码电路2009-04-18 1653

-

PLL译码电路2009-04-12 724

-

集成电路译码器2009-04-07 9922

-

控制信号译码电路2009-02-25 760

-

计数译码显示电路2008-10-09 2995

-

译码器2008-09-27 14347

全部0条评论

快来发表一下你的评论吧 !