传统线路和埋线路区别

描述

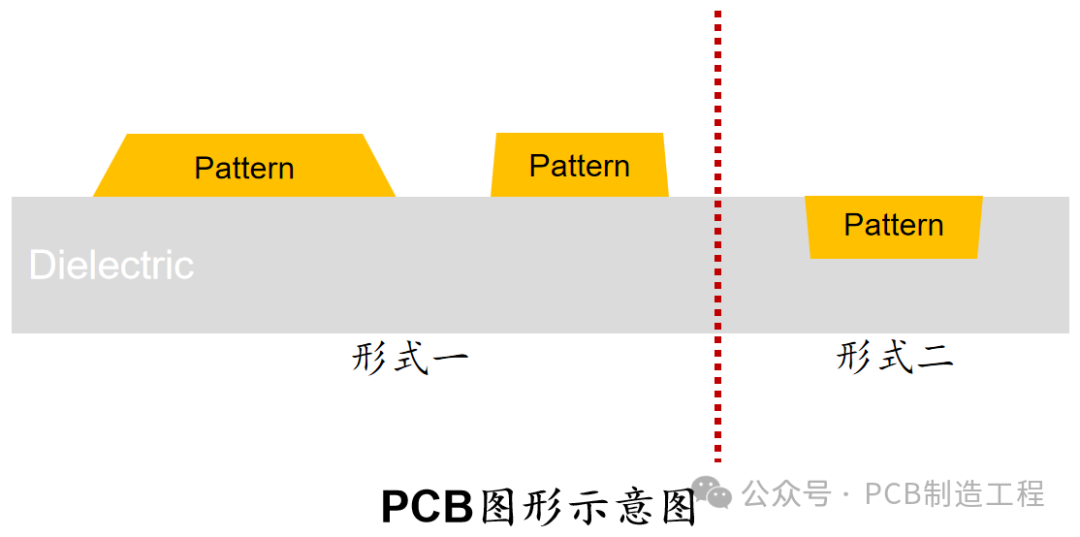

如上图所示,PCB板上的图形在被蚀刻出来之后,存在两种不同的形式:

形式一:图形位于介电层表面之上,其底部附着于介电层表面。

形式二:图形嵌入到介电层之中,其底部与介电层表面齐平或略低于介电层表面。

“形式二”的图形在PCB业界多称为埋线路,而“形式一”的图形没有查到相关的称呼,我们暂且称之为传统线路。

传统线路

PCB制造行业的图形制造工艺,不管是减铜法和加成法(全加成和半加成mSAP/SAP)均可以实现传统线路的制作。

传统线路PCB板的生产制作,PCB板厂通常基于PCB板设计工艺和制造成本的综合考量而采取不同的图形工艺,以实现品质与成本的平衡。

埋线路

埋线路的制作涉及埋入线路技术ETS或EPP技术。

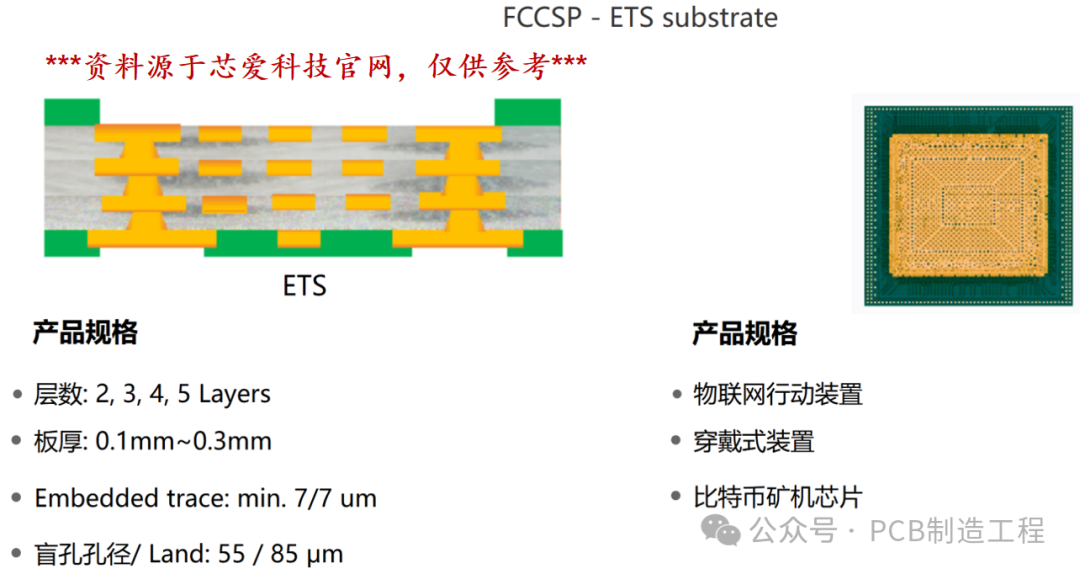

ETS:Embedded Trace Substrate

EPP:Embeded Pattern Process

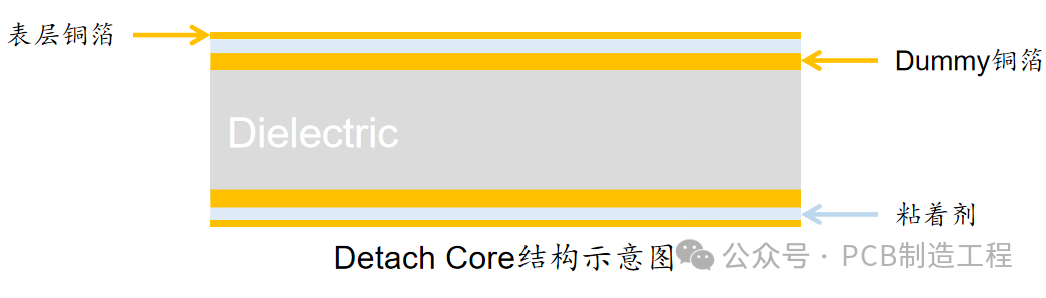

ETS/EPP技术也是一种无芯基板Coreless工艺, 其与常规Coreless工艺的区别在于:有一层表层图形形成在Detach Core材料的表层铜箔上,并利用压合工艺将图形埋入介质层中(常规Coreless工艺是直接在铜箔上增层);再在Detach Core基板分离后,通过闪蚀Flash Etching将底铜咬蚀掉形成埋入式图形。

Detach Core结构如下,其作为支撑辅助层材料,以实现超薄、细线路PCB板的制作。

ETS/EPP技术可以做到最小线宽/线距15μm/15μm以下,线路控制精度高,而且线路嵌入树脂中。

所谓“线路嵌入树脂中”是指线路的上面被树脂包覆,线路结合力大;这也是埋线路的优点之一。

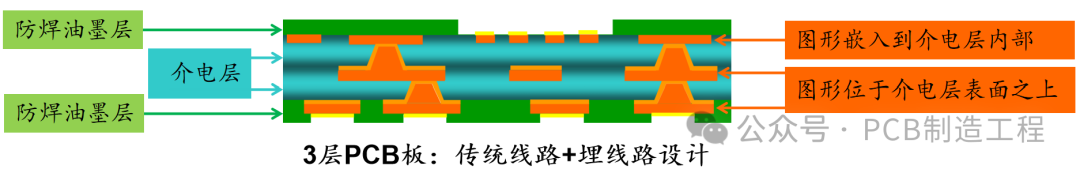

埋线路PCB板

市场上使用ETS/EPP技术的PCB板,通常被称为埋线板或平齐板。

埋线路设计走mSAP或SAP工艺。

多为薄板,超薄板设计,如CSP(Chip Scale Package)封装基板。

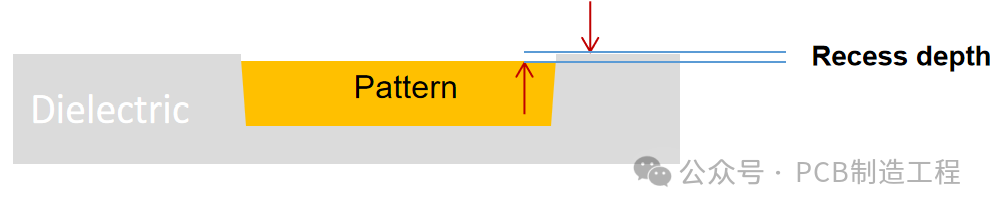

挑战点:在产品封装过程中,埋线深度会影响锡球与焊盘的焊接,尤其是当埋线深度较大时,可能会导致焊接不良和产品失效等异常。

特殊管控点:图形表面与介电层表面的深度差Recess depth (常见规范<=5um)。

如前所述,埋线路设计之PCB板需要使用无芯基板Coreless工艺,但其流程与常规Coreless工艺PCB板的区别如下:

常规Coreless工艺PCB板:直接在Detach Core表面铜箔上增层。

埋线路Coreless工艺PCB板:Detach Core的表层铜箔是埋线路层别。

埋线路PCB板的具体制作流程相对比较复杂,本文会结合如下案例进行简单说明,欢迎感兴趣的朋友斧正及交流。

案例(***资料源于网络,仅供参考***):埋线路设计之2层PCB板,Layer 1层为埋线路设计。

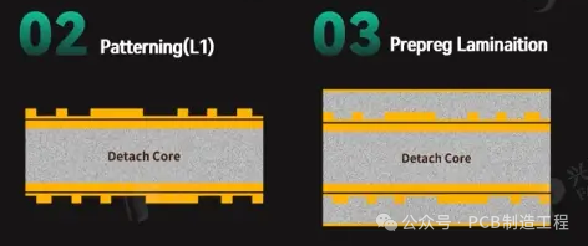

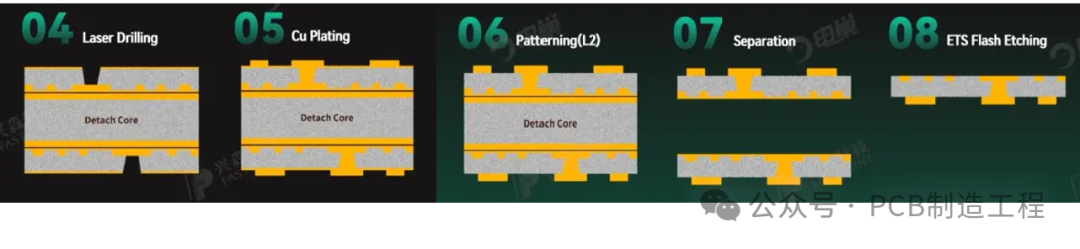

Pattern图形L1层走mSAP/SAP流程(Detach Core表面铜箔形成之层别):

->化铜->压膜->曝光->垂直显影->图形电镀->去膜->烘烤->棕化->叠板->压合->

Pattern图形L2层走mSAP/SAP流程(压合增层之层别):

->Laser drilling->化铜->压膜->曝光->显影->图形电镀->去膜->烘烤->Detach Core分板->Flash Etching->

埋线板产品示例

-

盲孔与埋盲孔电路板之前的区别2017-10-24 5023

-

高阶hdi线路板跟普通线路板的区别有哪些2020-04-17 3071

-

HDI埋盲孔线路板的生产工艺流程2020-06-08 7088

-

陶瓷线路板与传统FR4线路板的区别在哪里?2023-05-15 2751

-

盲埋孔线路板的基本概念和应用领域2023-08-17 5550

-

单相交流线路与三相交流线路的区别2023-11-16 2231

-

地埋线路的守护者:电缆行波故障预警与定位装置2024-01-23 1224

-

线路板的层和阶有什么区别?2024-02-23 2326

-

vty线路和console线路的区别2024-08-07 2691

-

埋盲孔PCB线路板加工流程2024-09-07 2256

-

hdi盲埋孔线路板生产工艺流程2024-10-23 8193

-

PCBA板与传统线路板区别2024-11-18 2535

-

HDI线路板和多层线路板的五大区别2024-12-12 5360

-

盲埋孔线路板在通信设备中的应用2025-08-12 837

-

盲埋孔线路板加工工艺介绍2025-11-08 1982

全部0条评论

快来发表一下你的评论吧 !