一种用于高精度DAC的实用型CMOS带隙基准源

电子说

描述

前言

随着电子信息产业、数字技术的蓬勃发展和IC制造工艺方面的快速发展,在信息数字化的大背景下,DAC有着良好的市场环境,比如在手机制造、无线网络等领域。因此,在更新速率和稳定性以及功耗方面有着良好性能的DAC将会有更好的市场前景。由于工艺技术到今天已经进入纳米级阶段,所以DAC的研制在工作速度和功耗性能上都有大幅度的提高。而想要获得一个高性能的DAC,除了工艺制造技术以外,关键还在于带隙基准源的稳定性等方面。由于带隙基准源的低温度系数的特性,被广泛应用于模拟和混和信号电路系统中,所以基准电压源产生的参考电压联系着模拟信号和数字信号。如果基准电压产生了+1%误差,则DAC模拟输出增加1%,原因为DAC产生的模拟输出与基准电压和输入数字量的乘积成正比。所以,基准源的精度指标必须好于DAC设计精度指标。为此设计一种功耗低、温度系数低和电源抑制比较高的电压基准源是有必要的。而为提高基准源的性能,减小误差技术成为关键。在降低功耗上,提出利用所有MOS管都工作在亚阈值状态,从而实现低功耗。还提出利用MOS管在不同工作区域的不同导电特性,设计了一种全MOS结构的电压基准源,虽然在低功耗方面基准源的性能有了很大的提升,但是在电源抑制特性方面都有待做出调整和改进。在提高电源电压抑制比方面,提出利用带隙电压基本原理,结合自偏置电流镜以及适当的启动电路,获得一个高电源抑制比的电压基准电路。还提出综合考虑设计电路,消除传统带隙基准电压源中运放的失调电压及电压抑制比对基准源指标的限制,其仿真结果显示在电路性能上依然有着提升的空间。

在综合上述提高带隙基准电压源性能的方法、优缺点和DAC的实际应用需求后,本文采用40 nm CMOS工艺,在传统的设计原理基础上,为了得到更加稳定的PTAT电流,利用了负反馈原理和基本电流镜等工作机理,同时采用了呈等比例的电阻值设计,来提高电路的稳定性。版图设计中,为了减小MOS管的失配性和版图面积,用电阻代替了电流镜结构的自偏置,使得电路结构更简单,实用性更强。

1 带隙基准源的基本设计原理

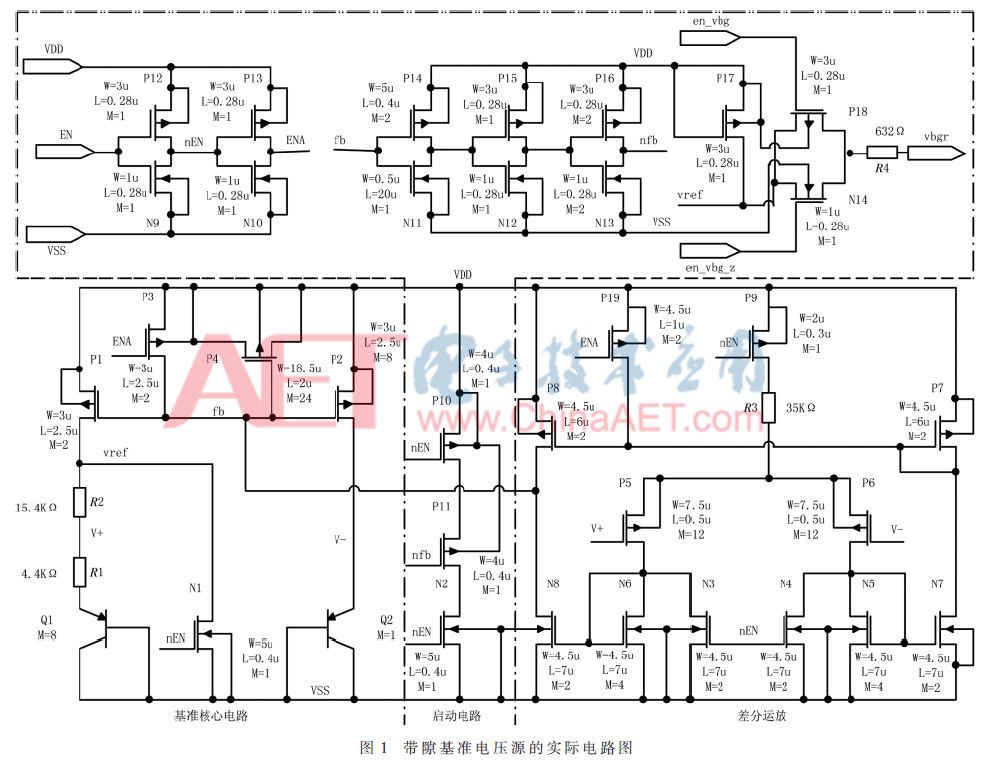

传统的带隙基准源的基本设计原理是利用运算放大器正负两输入端静态工作点相同的特性,还同时利用双极性晶体管VBE具有负温度系数和处在不同的集电极电流下工作的两个双极性晶体管的ΔVBE具有正温度系数的特性,通过调节电阻值的大小来完成一个带隙基准电压源的设计[8]。基于40 nm CMOS工艺,设计了一种高稳定性的带隙基准电压源电路。图1为带隙基准电压源的实际电路。

1.1 基准核心电路图分析

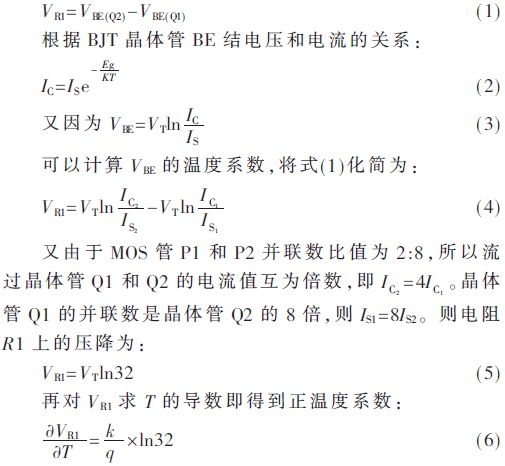

如图1所示,可以看出此设计的整体架构,在有电源电压和有效的使能信号提供时,且在整个带隙基准电压源正常工作的情况下,利用文献[9]中的公式进行电路分析。其中电阻R1上的压降为:

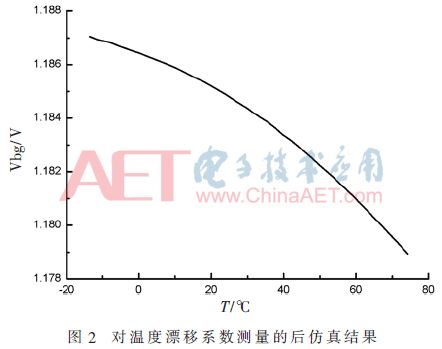

由于BJT晶体管的VBE(Q1)具有负的温度系数,在当VBE(Q1)约为750 mV,T为300 K时大约负温度系数为-1.5 mV/K;而ΔVBE具有正的温度系数,在室温时大约为+0.087 mV/℃,所以通过适当地选取R1和R2的电阻值,可以使两项之和达到零温度系数,从而得到温度特性较好的基准电压:

1.2 启动电路分析

如图1所示,输入电源电压VDD为2.5 V时,当EN为低电平时,nEN为高电平,则ENA为低电平。MOS管P9关断即运放电路无偏置电流提供,并且由于MOS管N3、N4开启,导致N5、N6被地线短路即整个运放电路处于不工作状态。由于P3开启,fb(feedback)信号被上拉到VDD,即为高电平,P11为开启状态,P10由于nEN为高电平则为关断,N2为开启状态,VDD和VSS未短路。由于N1的栅极输入为nEN则开启将Vref下拉到VSS,所以输出电压为低电平,运放和V+、V-提供电路均不工作,所以偏置电流源和基准核心关断。当EN为高电平时,nEN为低电平,则ENA为高电平。MOS管P9开启,允许电流流进放大器。当电流稳定后,通过电阻R3启动运放电路。同时N3、N4、P3关断,则基准核心电路可以正常工作。MOS管N1为关断状态,允许正常Vref输出。若en_vbg、envbg_z使得传输门模块处于关闭状态,则即使Vref有正常输出值,最终的输出信号vbg亦为低电平电压值。启动电路增加了电路自身的稳定性和容错性;对于DAC的功耗降低,亦有一定的帮助作用。

1.3 OPAMP实际电路图分析

如图1中所示的OPAMP实际电路,其在正常工作时,处于深度负反馈状态,也就是将其正负两端输入电压钳制在相同的电位上,在带隙基准电压源中就是充分利用运算放大器的这一特性来实现与温度无关的带隙电压输出[9]。此为一种典型的两级运放的电路结构,P5、P6和N5、N6以及P9、R3组成第一级,N7、N8和P7、P8MOS管组成第二级。其中P9、N3和N4为开关管,控制此两级运放的工作状态,当P9开启时,偏置电流通过电阻R3产生。N3、N5处于关断状态运放可正常工作。当输入端口VDD为2.5 V时,经测试差分运放的增益为67.8 dB,满足设计要求。

2 仿真结果和版图

2.1 版图和后仿真结果分析

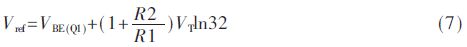

实际电路和版图及其前后仿真均基于40 nm的CMOS工艺,利用cadence对电路进行仿真。首先针对不同的测试参数搭建不同的测试电路,再利用Spectre软件进行仿真[10],将传输门的两个时钟控制信号en_vbg、envbg_z分别设为低电平和高电平使得传输门为开启状态,将使能信号EN设为低电平,即可让运放和PTAT模块能够正常工作。电源电压VDD输入为2.5 V,VSS输入为0 V,经测试在各个模块都正常工作的情况下,电流为156.74 μA,输出电压为1.184 V;启动时间为0.5 μs。

从图2中可以看出电源电压为2.5 μV,温度在-15 ℃~75 ℃范围内线性变化输出电压随温度的变化曲线。由仿真结果得到的数据经计算得后仿真温度漂移系数为8.7×10-5/℃。

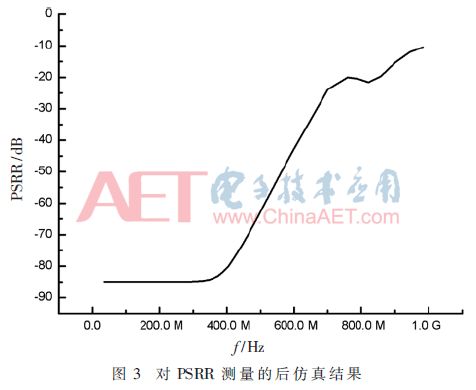

从图3中可以看出在温度为室温下,在低频时PSRR为-85 dB,结果显示带隙基准电压源有良好的电压抑制特性。

根据40 nm工艺的设计规则,绘制了如图4所示的版图,对于沟道较宽的MOS管采用了叉指结构绘制,以期减小由于工艺限制对电路性能的影响;对于差分运放的版图绘制,为了减小其输入失调电压,整体呈对称结构;为了得到更好的匹配,对9个双极性晶体管的布局做了调整,并且在一些器件的四周加了虚拟MOS管。

2.2 与其他文献参数对比及分析

从表1可以看出本文与各参考文献对比的优缺点,本文在温度稳定性方面的缺点尤为明显,还存在着诸多问题,确实有待改进电路中的正温度系数和负温度系数的权值,在电源抑制特性上具有一定的参考价值的。

3 结论

本文根据基准源的精度必须好于DAC设计精度指标。利用负反馈和基本电流镜等原理,合理设计电路的情况下得到了稳定的PTAT电流,并根据带隙基准电压源的设计原理得到一个高精度和快速启动的CMOS带隙基准电压。同时,在版图面积和电路性能方面,在满足DAC指标要求的情况下,以尽力减小MOS管的使用个数,以减少版图中寄生参数的产生,如省去了用于产生自偏置电流的MOS管。最终,得到了一款参考输出电压为1.184 V,启动时间为0.5 μs,电源电压抑制比为-85 dB,版图面积为7531.9 μm2,并且能够集成于高速DAC芯片内部的带隙基准电压源。此带隙基准源被一种高速、高分辨率的DA转换器应用。

-

一种高精度BiCMOS电流模带隙基准电路设计2019-07-12 2938

-

基于LDO稳压器的带隙基准电压源设计2018-10-09 3112

-

关于一种用于高精度DAC的实用型CMOS带隙基准源2018-06-22 4831

-

带隙基准电路_cmos无运放带隙基准源2018-01-11 18332

-

cmos带隙基准电压源设计2017-11-24 24785

-

一种低功耗差动CMOS带隙基准源2017-01-14 1167

-

一种改进型低温度系数带隙基准源电路_范建功2017-01-08 904

-

一种带曲率补偿的高精度带隙基准源2017-01-07 888

-

一种高精度带隙基准源2012-02-13 1158

-

一种高PSR带隙基准源的实现2011-08-23 3991

-

一种高精度BiCMOS带隙电压基准源的设计2010-08-03 949

-

一种结构简单的CMOS带隙基准电压源设计2010-01-11 895

-

一种抵消曲率系数的高精度低温漂CMOS带隙基准的设计2009-12-21 676

全部0条评论

快来发表一下你的评论吧 !