使用FPGA对40G以太网接口芯片Serdes进行测试的方法

描述

带Serdes的高速以太网接口流片后如果功能不正常,可以采用带有相同接口类型的FPGA进行测试定位问题。本文简单的介绍一种通过FPGA来对基于四通道serdes的40G/10G以太网接口PMA和PCS层进行链路连接测试的方法,欢迎大家留言讨论指导。

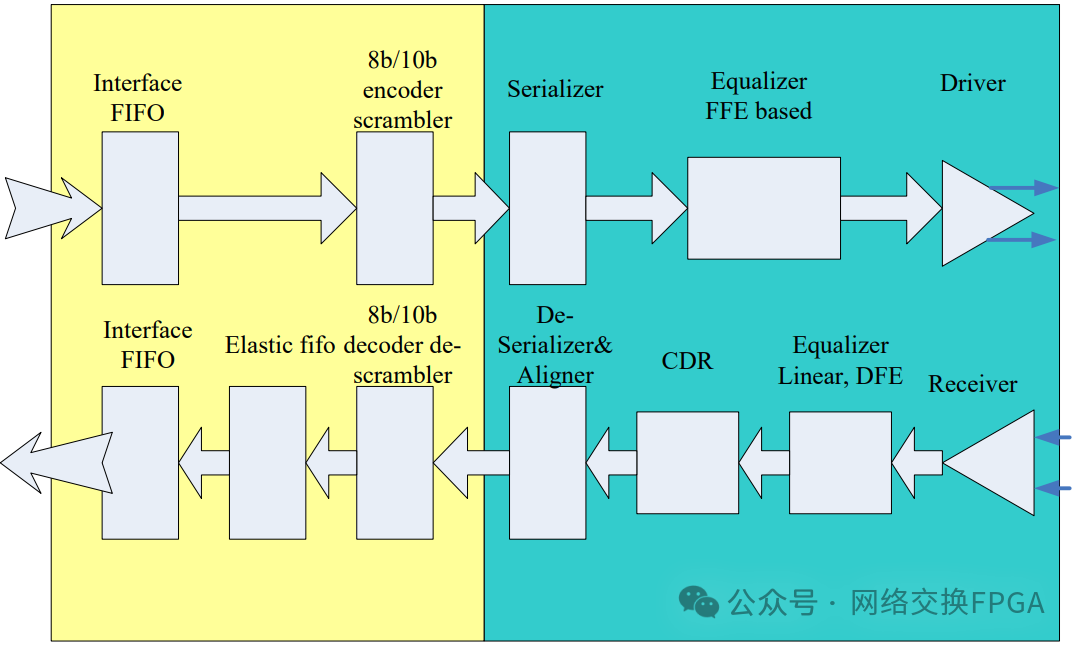

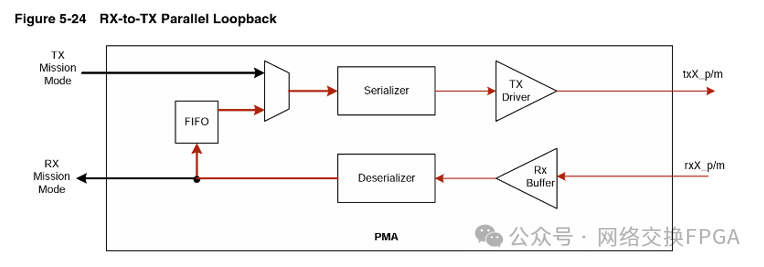

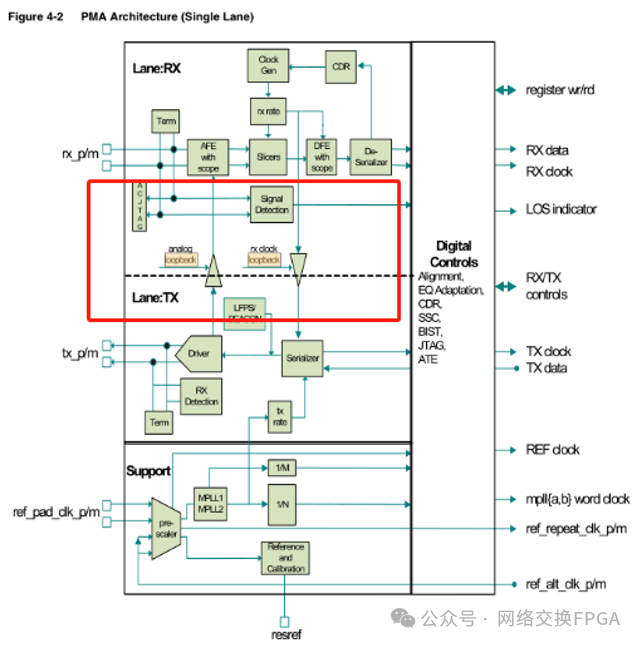

SERDES 是英文 SERializer(串行器)/DESerializer(解串器)的简称。它是一种时分多路复用(TDM)、点对点的通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而减少了传输线之间的干扰,增大了背板传输距离,并且大大降低通信成本。同时带来了诸如减少布线冲突、降低开关噪声、更低的功耗和封装成本等许多好处。而 SERDES 技术的主要缺点是需要非常精确、超低抖动的元件来提供用于控制高数据速率串行信号所需的参考时钟。即使严格控制元件布局,使用长度短的信号并遵循信号走线限制,这些接口的抖动余地仍然是非常小。 SERDES 主要由物理介质相关( PMD)子层、物理媒介附加(PMA)子层和物理编码子层( PCS )所组成。PMD 是负责串行信号传输的电气层,PMA 负责串化/解串化,PCS 负责数据流的编码/解码,在 PCS 的上面是上层数字 IP 功能。一般的高速接口均是由 2 个 IP(时钟域)组成,上层是数字 IP,一般执行接口协议相关的处理,下层为 SERDES 层,主要执行串并,并串转换的处理。 如下图所示,蓝色背景子模块为 PCS 层,是标准的可综合 CMOS 数字逻辑,可以硬逻辑实现。褐色背景的子模块是 PMA 层,是数模混合 CML/CMOS 电路,是理解 SERDES 区别于并行接口的关键,也是本文要讨论的内容。

发送方向(Tx)信号的流向: 处理器软逻辑(fabric)送过来的并行信号,通过接口FIFO(Interface FIFO),送给 8B/10B 编码器(8B/10B encoder)或扰码器(scrambler),以避免数据含有过长连零或者连一,之后送给串行器(Serializer)进行 并->串 转换,串行数据经过均衡器(equalizer)调理,由驱动器(driver)发送出去。 接收方向(Rx)信号的流向, 外部串行信号由线性均衡器(Linear Equalizer)或判决反馈均衡器(Decision Feedback Equalizer)调理,去除一部分确定性抖动(Deterministic jitter)。CDR 从数据中恢复出采样时钟,经解串器变为对齐的并行信号。8B/10B 解码器(8B/10B decoder)或解扰器(descambler)完成解码或者解扰。如果是异步时钟系统(plesio-synchronous system),在用户 FIFO 之前还应该有弹性 FIFO 来补偿频差。 在测试前,可以先搭建仿真验证环境,对FPGA和芯片版本的40G/10G接口进行仿真。

仿真目的:

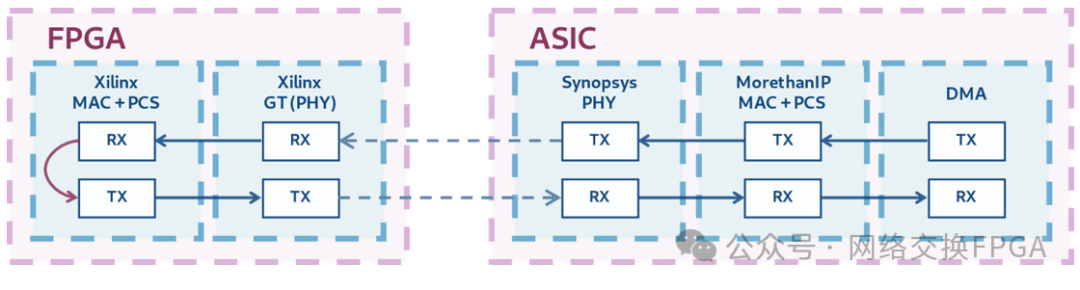

确定FPGA在10GBASE-KR与10GBASE-R模式下与ASIC连接链路的稳定,以及链路具体状态。

连接关系与数据通路:

FPGA与ASIC两侧的PCS均显示每个bus的四个lane进入锁定状态(xl_block_lock为高),但四个lane对齐的标志位xl_align_done为0。与实际测试表现一致。

通过仿真进行异常定位:通过FPGA侧的PCS RTL信号追查链路无法对齐、aligndone标志无法产生的原因。

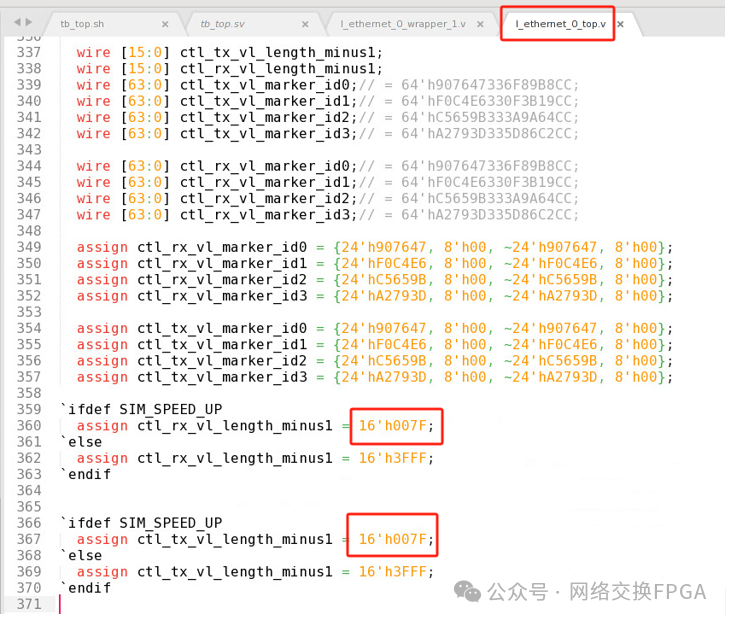

在FPGA的PCS的对齐逻辑中发现其检查对齐标志(alignmarker)之前,需要lane保持同步锁定一定时间,该时间由代码如下位置指定:

(1)当仿真环境未添加SIM_SPEED_UP宏定义,仿真中PCS检查align marker的时间间隔设置为3FFF(16383)个block,RTL仿真跑到这个时间间隔需要花费极大的时间。另外观察到,FPGA一侧添加SIM_SPEED_UP宏定义后,上述参数为3F(原代码中),该参数与ASIC中PCS的vl_intvl寄存器配置的7F值非常像,而且结合PCS手册描述和网表反推,vl_intvl同样是与对齐标志间隔相关的寄存器,该寄存器在实际上板、仿真时应当设置不一样的值:对于满足802.3的40GBASE-R标准的情况,需要设置为16383,对于仿真,需要减小该数值以缩短仿真的链路对齐时间。

(2)在FPGA中打开SIM_SPEED_UP宏定义进行仿真。FPGA侧对齐标志间隔参数(ctl_Xx_vl_length_minus1)设置为3F,ASIC的vl_intvl寄存器保持7F值。进行仿真,追查对齐相关信号,找到FPGA侧PCS查找align marker的逻辑,PCS找到第一个marker后,在下一个应当检测到marker的位置没有继续找到marker,因此PCS的连接状态从ALIGNING(对齐中)和IDLE(失去对齐)中反复跳转,无法进入ALIGNED(已对齐)状态。该现象直接说明了对端(ASIC侧)的PCS在链路中插入align marker的间隔与FPGA侧的不一致,因此两设备无法建立对齐链路。

(3)将仿真中的FPGA的ctl_Xx_vl_length_minus1与ASIC的vl_intvl寄存器设置为同样的值(7F),让两侧的PCS在相同的7F个block间隔后插入或检测align marker。仿真观察到FPGA的PCS对齐状态机成功进入ALIGNED状态,表明4个lane的对齐基本条件能够满足。结合以上仿真结果,可以得知之前ASIC侧的vl_intvl寄存器值配置为7F为快速仿真设置,与802.3要求的3FFFF(16384)不符,实际芯片测试中需要将vl_intvl寄存器配置为3FFF进行测试。

40G线速仿真:通常在ASIC IP核中,PHY和MAC接口处寄存器用来配置是否工作在40G线速状态,如MAC没有配置tx_ipg_comp_reg寄存器,该寄存器用于补偿PCS插入对齐标志造成的40G满速时的线速损耗,那么MAC就无法运行在40G线速模式。此时,对齐标志占比1/16384,导致损失速率的实际速率为0.999938*40Gbps,实际芯片测试中,最高速率能够达到0.999928*40Gbps不丢帧,该比例与对齐标志损耗接近。若配置相关寄存器后,则链路中对齐标志就会删除,此时芯片实际测试可以跑满40G线速。如下视频是A芯片实际测试40G打流99%不丢帧的视频:

由于仿真无法百分百跟真实场景对应,尤其是PMAC侧数模混合部分,在仿真环境中往往被简化模型替代,仿真通过,但实际上板或流片则可能会有问题。以下介绍FPGA与ASIC实际上板测试情况。

1、硬件连接方式

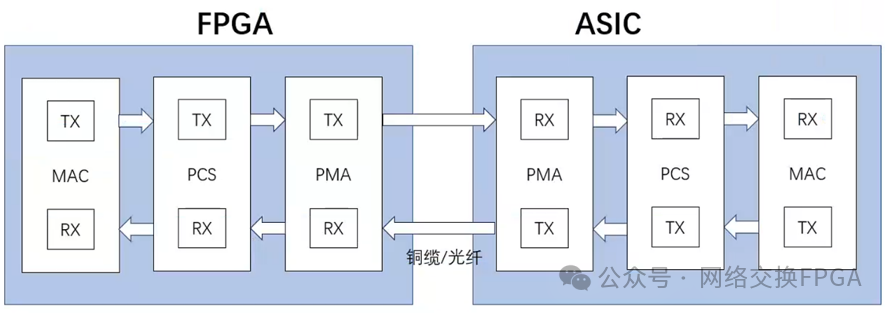

使用铜缆或者光纤将FPGA和ASIC侧的光口进行连接。ASIC侧的IP需要根据需求或者手册配置成正常工作模式。FPGA侧只用例化相关IP,并进行管脚约束。FPGA侧可使用IP参考第二部分。

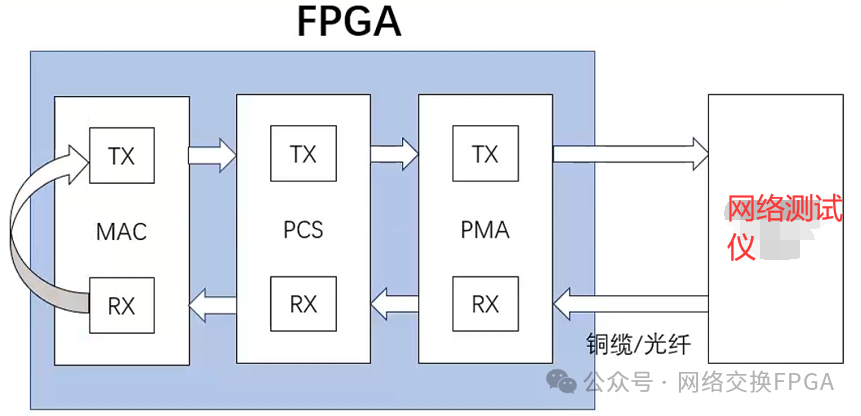

使用上述方式进行监测时首先要保证FPGA侧正常工作。可以通过连接网络测试仪进行打流回环来验证。如下图所示。本文针对40G/10G高速以太网接口利用FPGA对同样接口速率的40G/10G以太网接口serdes和PCS层进行互连互通,进而对流片后的serdes芯片进行调试(也可能是芯片的serdes或PCS工作模式配置不正确)或故障定位。FPGA侧40G/10G可以参考xilinx官方的两个文档pg211和ug578,其中pg211介绍40g/50g的MAC+PCS等相关的知识点,ug578介绍GTY的知识,具体可以到官网下载,学习查看。FPGA侧40G/10G接口工作是否正常可以参考文章:UltraScale+FPGA中Serdes的多lane对齐异常解决方案。

同时由于PCS的工作机制,其必须在链路正常稳定的情况下才能对数据进行正常传输。所以如果链路有问题,PCS部分会有相关寄存器反映当前状态。具体寄存器或者内部信号参考第三部分。

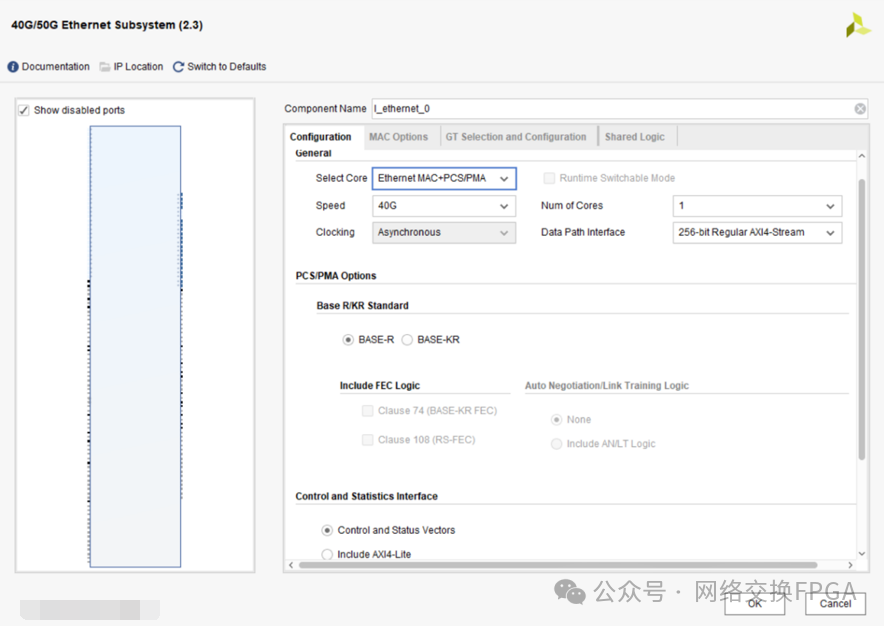

2、FPGA使用IP

1)对端是40G以太网接口(4lane 40)

示例工程如下:(略)

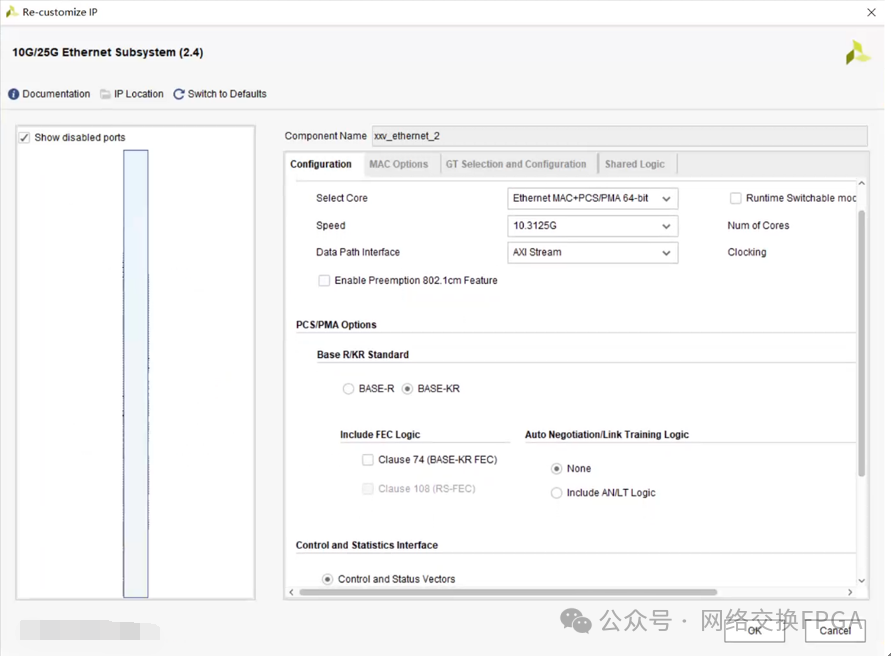

2)对端是10G以太网接口(单lane 10)

3)对端是10G以太网接口(4lane 10)

3、信号抓取说明

1)如果使用40G/50G Ethernet Subsystem或者10G/25G Ethernet Subsystem,直接监测相关状态寄存器。

| RX PCS通道对齐状态 | ||

| 寄存器 | 含义 | 备注 |

| stat_rx_synced[3:0] | 字边界已同步。这些信号用于指示 PCS 通道是否已完成字边界同步。值为 1 表示对应 PCS 通道已实现字边界同步,并且已接收到 PCS 通道标记。对应于第 82.3 条中所定义的管理数据输入/输出 (MDIO) 寄存器位 3.52.7:0 和 3.53.11:0。此输出对电平敏感。 | |

| stat_rx_synced_err[3:0] | 字边界同步错误。这些信号用于指示在相应的 PCS 通道内进行字边界同步期间,是否发生错误。值为 1 表示由于同步报头成帧位错误或者从未收到 PCS 通道标记,对应 PCS 通道已丢失字边界同步。此输出对电平敏感。 | |

| stat_rx_mf_len_err[3:0] | PCS 通道标记长度错误。这些信号用于指示相应通道内是否发生了 PCS 通道标记不匹配(即,接收到的 PCS 通道标记间隔字数并非 ctl_rx_vl_length_minus1)。值为 1 表示对应通道接收 PCS 通道标记的间隔错误。它将保持高电平,直至消除错误状况为止。 | |

| stat_rx_mf_repeat_err[3:0] | PCS 通道标记字错误。这些信号用于表示在相应通道内检测到构成的 PCS 通道标记字错误。值为 1 表示发生了错误。此输出将脉冲 1 个时钟周期,以指示错误状况。脉冲可在不间断的连续周期内发生。 | |

| stat_rx_mf_err[3:0] | 当 stat_rx_aligned 值为 1 时,表示全部通道都已对齐/去歪斜,并且接收器已准备好接收包数据。 | |

| stat_rx_aligned_err |

当 stat_rx_aligned_err 值为 1 时,将发生以下 2 种情况之一: • 通道对齐经多次尝试后失败。 • 通道对齐已丢失(stat_rx_aligned 断言有效,随后被取反) |

|

| stat_rx_misaligned | 对齐错误。此信号表示通道对齐器并未在所有通道上都接收到期望的 PCS 通道标记。在所有通道上都至少接收到 1 个 PCS 通道标记并且至少接收到 1 个错误的通道标记后,此信号才会断言有效。此状况的发生比错误晚 1 个元帧。如果从未正确接收到任何通道标记,则此信号不会断言有效。通道标记错误通过对应的 stat_rx_mf_err 信号来指示。此输出将脉冲 1 个时钟周期,以指示错误状况。脉冲可在不间断的连续周期内发生。 | |

|

stat_rx_framing_err_[3:0][3:0] stat_rx_framing_err_valid_[3:0] |

这组总线旨在用于保留同步报头错误记录。每个 PCS 通道都有一对输出。 stat_rx_framing_err_[PCSL_LANES-3:0] 输出总线用于指示已接收到的同步报头错误数量,当对应 stat_rx_framing_err_valid_[PCSL_LANES-3:0] 采样为 1 时,此输出总线合格(即,仅限在此情况下其值才有效)。 | |

| stat_rx_vl_number[3:0][1:0] | 每个总线所指示的特定 PCS 通道的状态反映在特定状态管脚上。例如,stat_rx_vlane_number_0 所指示的 PCS 通道的状态反映在其它状态信号的管脚 0 上。这些总线可用于检测是否尚未找到 PCS 通道或者是否某一 PCS 通道已映射到多个状态管脚。 | |

| stat_rx_vl_demuxed[3:0] | 在每个通道上都达成字边界同步后,如果该总线的位为 1,则表示已正确查找到对应 PCS 通道,并且已对其正确完成逆多路复用。 | |

| stat_rx_block_lock[3:0] | 每个 PCS 通道的块锁定状态。值为 1 表示对应通道已达到第 82 条中定义的块锁定状态。对应于第 82.3 条中所定义的 MDIO 寄存器位 3.50.7:0 和 3.51.11:0。此输出对电平敏感。 | |

| stat_rx_aligned | 所有 PCS 通道均已对齐/去歪斜。此信号表示是否所有 PCS 通道均已对齐并去歪斜。值为 1 表示所有 PCS 通道均已对齐并去歪斜。当此信号为 1 时,表示 RX 路径已对齐并且可接收包数据。当此信号为 0 时,表示存在本地故障状况。这也对应于第 82.3 条中所定义的 MDIO 寄存器位3.50.12。此输出对电平敏感 | |

| stat_rx_hi_ber | 误码率 (BER) 过高指示符。设置为 1 时,BER 过高(根据 IEEE 802.3-2015 标准的定义)。对应于第 82.3 条中所定义的 MDIO 寄存器位 3.32.1。此输出对电平敏感。 | |

| stat_rx_status | PCS 状态。值为 1 表示 PCS 已对齐且未处于 hi_ber 状态。对应于第 82.3 条中所定义的 MDIO 寄存器位 3.32.12。此输出对电平敏感。当 stat_rx_aligned 为 1 且 stat_rx_hi_ber 为 0 时,此输出设置为 1。此设置由 IEEE 802.3-2015 标准定义。 | |

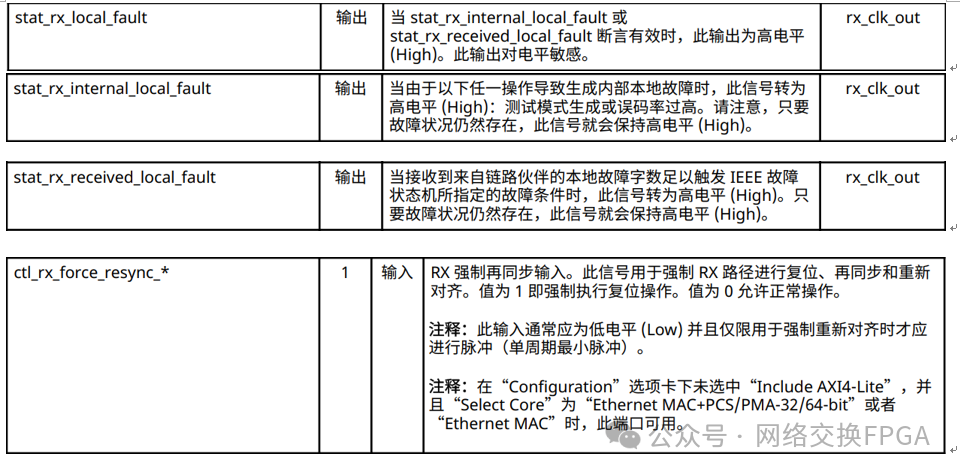

| stat_rx_local_fault | 当stat_rx_received_local_fault 或stat_rx_internal_local_fault 断言有效时,此输出设置为 1。此输出对电平敏感。 | |

| RX错误状态 | ||

| stat_rx_bad_fcs | 当此信号值为 1 时,表示错误检测逻辑已在接收到的包中发现接收的 CRC32 值与期望的值不匹配。当检测到 CRC32 错误时,接收到的包将被标记为包含错误,并随在上一次传输(即 rx_eopout 断言有效的周期)期间断言有效的 rx_errout 一起发送,但 ctl_rx_ignore_fcs 断言有效的情况下除外。每次检测到 CRC32 错误时,都将断言此信号有效并保持 1 个时钟周期。 | |

| stat_rx_bad_code[1:0] | 此信号用于指示RX PCS 接收状态机处于IEEE 802.3-2015 标准所定义的 RX_E 状态的周期数。 | |

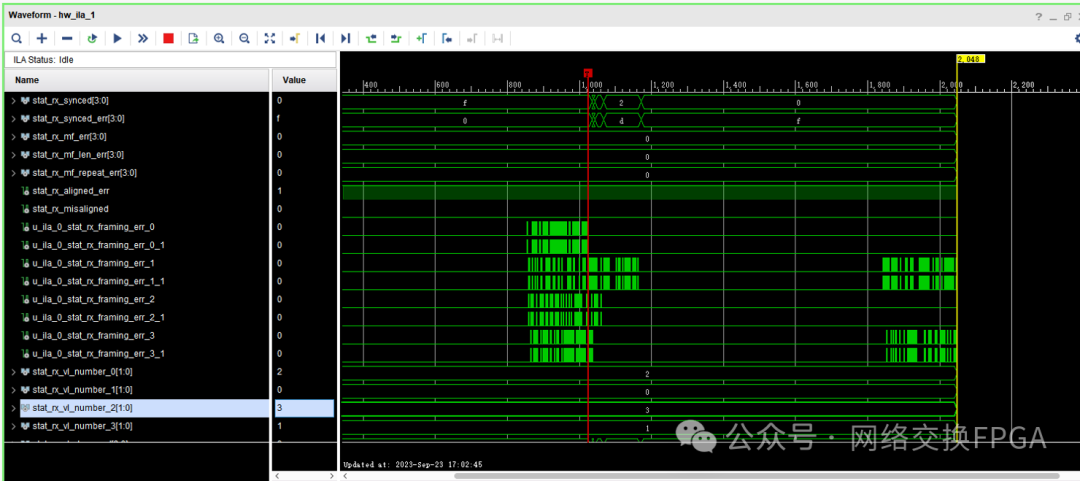

下图为A芯片 40G接口的实测截图。stat_rx_synced应始终保持4’hF,不稳定说明信号质量太差。一定程度上反映ASIC侧的时钟质量问题。

2)如果40G PCS部分使用相关代码,可以基于以下信号展开监测:

40G PCS和对端链路建立过程主要有ABC三个阶段:

A、同步头锁定:

监测信号:

/i_RX_CORE/i_RX_LANE0/i_RX_WD_SYNC_0/align_status[1:0]

/i_RX_CORE/i_RX_LANE0/i_RX_WD_SYNC_1/align_status[1:0]

/i_RX_CORE/i_RX_LANE1/i_RX_WD_SYNC_0/align_status[1:0]

/i_RX_CORE/i_RX_LANE1/i_RX_WD_SYNC_1/align_status[1:0]

正常情况下恒为1。

0表示复位,2表示锁定失败

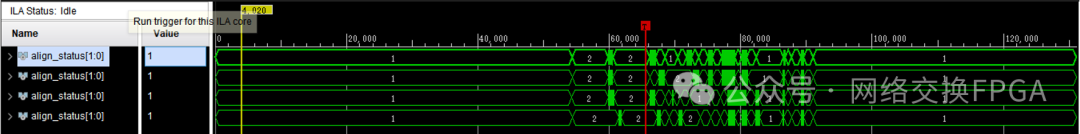

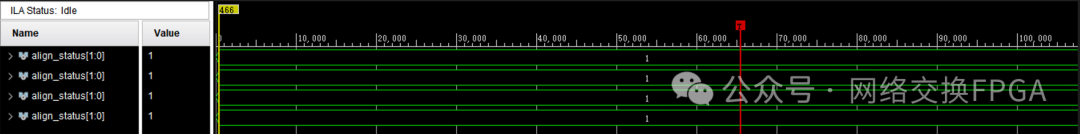

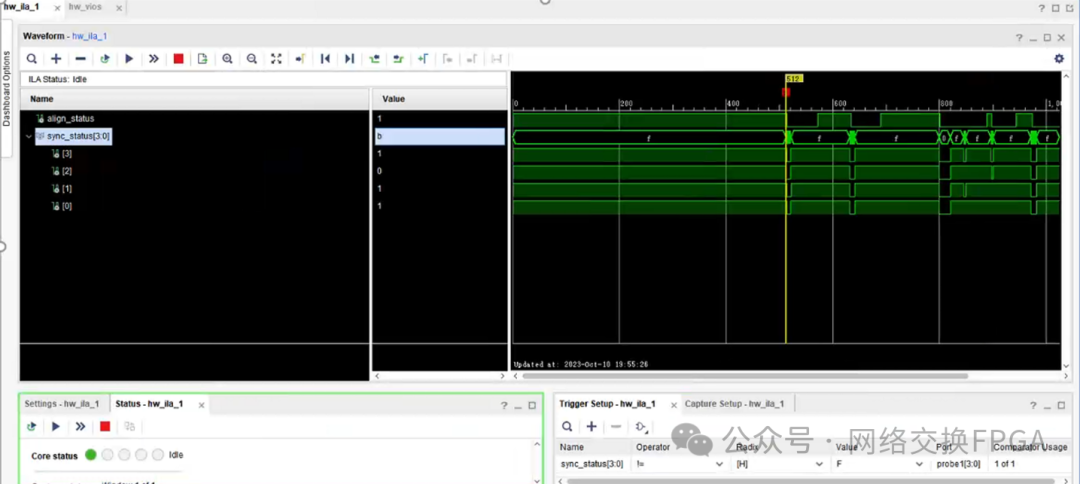

下图为A芯片40G接口的实测截图。alian_status应始终保持2’b1,不稳定说明信号质量太差。

FPGA连接网络测试仪,正常链路情况下的截图。

B、四通道各自锁定

监测信号

/i_RX_TOP/i_RX_CORE/i_RX_LANE0/i_AFINDER_0/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE0/i_AFINDER_1/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE1/i_AFINDER_0/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE1/i_AFINDER_1/word_synced

正常情况下恒为1

0表示复位或锁定失败

C、四通道实现对齐

监测信号

/i_RX_CORE/i_RX_DESTRIPER/i_RX_LANE_ALIGNER/aligned

正常情况下恒为1

0表示复位或对齐失败

B芯片40G接口芯片测试时,四通道的align_status和word_synced信号一直保持为1,说明同步头锁定和四通道各自锁定没有问题,但是aligned信号没有拉高过,说明四个通道没有实现过对齐。

继续抓取四通道对齐的前一级模块(四个缓存模块)的相关信号,发现四个通道彼此间的数据延时差异过大,通常一个通道的数据缓存FIFO溢出时,其余通道仍然没有数据进入缓存模块,导致下一步通道间对齐无法进行。

后续发现PCS的模式配置寄存器有误,默认情况下为10GBASE-CX4,将PCS正确配置为40GBASE-CR4后对齐标志可以成功拉高且保持稳定。

前面的四通道数据延时差异过大也是因为这种配置模式下对端单lane 3.125Gbps的数据在FPGA侧单lane 10.3125Gbps的数据通道上传输导致的。

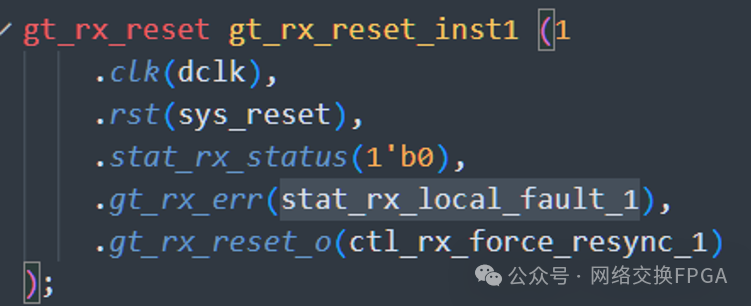

另外,如果FPGA自身四通道就没有对齐,那大概率也是由于复位没有做好,或者是复位的顺序和复位时间,以及代码中看门狗方式复位代码有问题。

扩展:FPGA版本10Gbps以上速率以太网光口热插拔问题。

在较复杂的测试环境下,即交换机光口始终有分组进入时,对交换机进行上下电或进行光口拔插,会导致交换机的40G MAC IP核会出现卡死和输出错帧的现象,若没有错帧过滤模块,错帧可能会导致交换机可编程解析器模块不能正常工作,也可能会导致地址学习表短时间内学习到大量的错误的MAC地址和端口号,因此,需要“看门狗系统”主动复位交换机出错的40G IP的MAC和GT,以及过滤MAC给出的错帧(利用rx_user信号)。

a、rx侧的时钟需要恢复训练,在连接上光纤后,tx数据中带有时钟信息,rx接收到tx的时钟信息后,需要从高速串行流中恢复时钟(锁相环稳定时钟),待时钟稳定后才能正常传输数据。

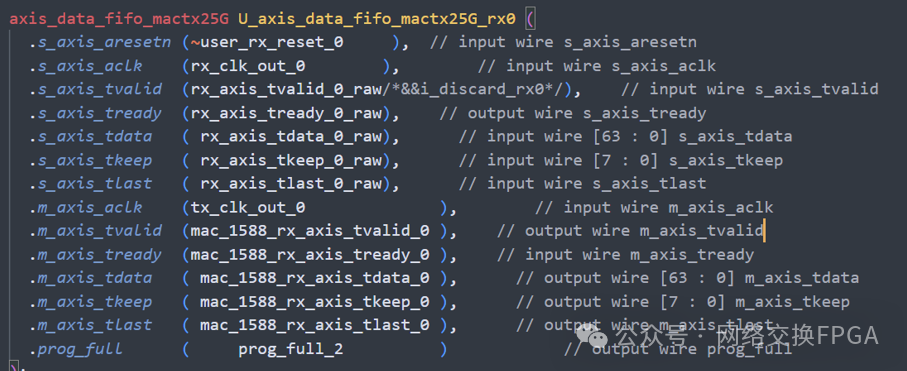

基于10G源码作者Alex(著名开源项目Corundum网卡的作者)的代码,我们在rx侧出来的axi data接异步时钟fifo,输入用rx时钟,输出用tx时钟。因为tx时钟由本地晶振给出,保持稳定,不需要训练,如下图。

b、环境比较差的时候,做光口拔插实验,会有link状态的问题,link是单方向的rx link,查看手册找到复位逻辑,做检错复位,以及link状态丢失的主动复位,主动复位时间比较长持续100ms,1s内不会重复触发。

复位模块如下:

在拔插的时候对于电路来说不是单纯的拔插,不论是拔动作还是插动作link状态都会有0-1 1-0的变化,而link状态时断时续,在拉高时会有错帧进入,需要加入错帧过滤逻辑(判断rx_user信号)。

c、打流过程中复位会产生进入错帧的问题,也就是gt侧在link状态拉高的时候,同步并不是直接正常的,刚开始的时候会有一些内容和长度有问题的帧,大概10帧,对于2层交换机来说会地址自学习产生错误的mac地址,需要在link状态稳定时让帧进入逻辑,加入端口使能。加入端口使能,不往该端口发帧和不让该端口的帧进交换,同时交换机有状态信息统计也同步停止更新或者打开,这样可以保护交换机内部逻辑不会受到影响。

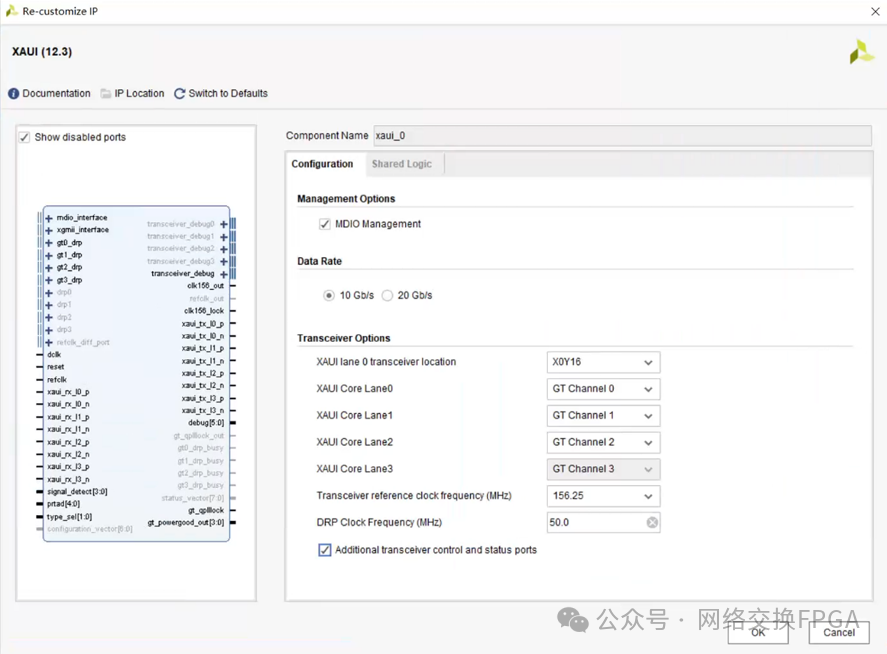

3)如果使用XAUI

主要监测align_status和sync_status[3:0]。

下图为A芯片10G以太网接口实测截图。

ILA显示align_status不恒为1,sync_status不恒为F,说明10G的链路也不稳定。

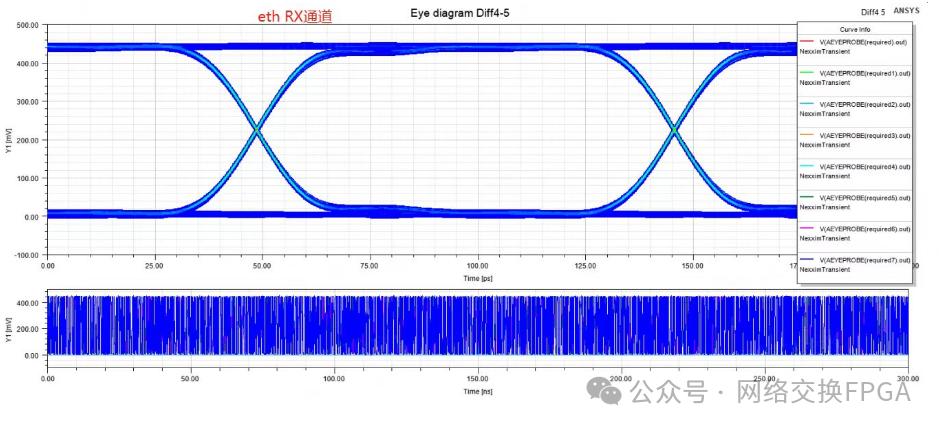

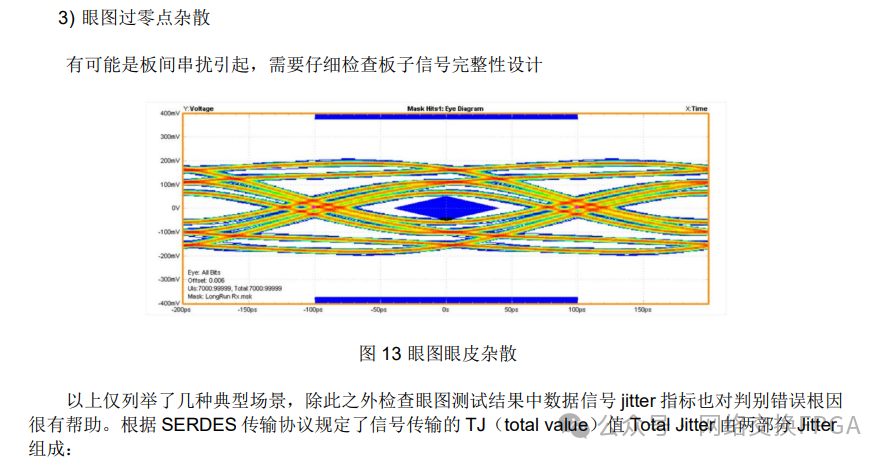

若ASIC侧Serdes测试有问题,则也可能是封装和基板带来的问题。封装时要考虑多lane之间共地,die外围共享电阻的连接方式。同时,还要注意serdes时钟是片内还是片外,在使用片内时钟(on-chip clock)时,需要将片外时钟接地或者悬空。在使用片外时钟时,也需要将片内时钟接地或者悬空。另外,基板也需要进行SI、PI等仿真,如果眼图仿真结果不好,则有可能阻抗不连续,过孔要考虑;还有等长走线,虽然走了等长,有可能两条线没有一起绕蛇形等多种可能。以下是仿真较好的情况:

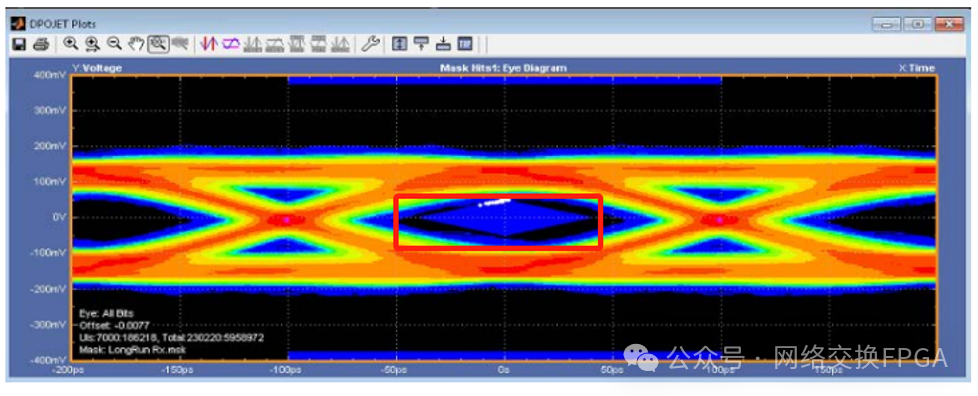

通过眼图判断serdes的情况也很重要,如下图:

正常情况下,图中眼睛区域可被包住即可。除了用专用设备看眼图外,一般IP供应商会提供MATLAB或者Python的程序,可以通过读取实际Serdes测试时对应相关寄存器的状态,绘制出对应的眼图。

4、ASIC版serdes故障定位

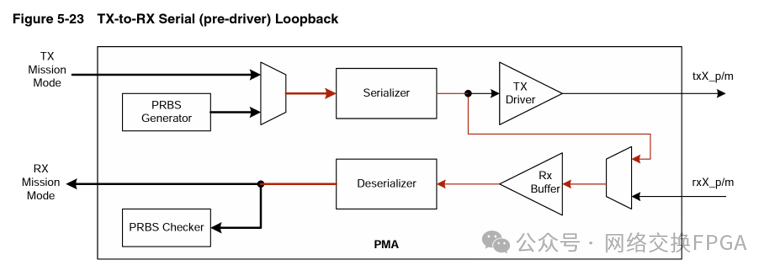

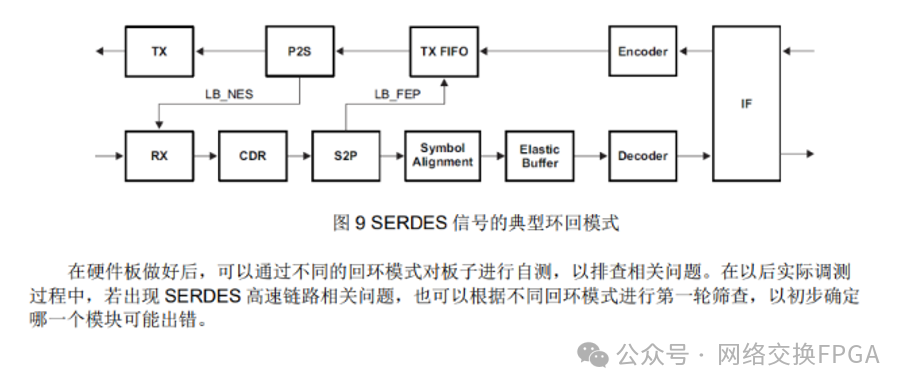

若SERDES高速链路存在问题,可通过多种回环模式进行第一轮筛查,以初步排查问题。

主要使用两种模式:

(1) 近端回环LB_NES模式,即测试芯片PHY的tx2rx loopback,PRBS;

(2) 远端回环LB_FEP模式,即测试芯片PHY的rx2tx loopback;

若在近端回环模式下,BER值(误码率)较高,主要可以检测SERDES 输入时钟相关设置,如果远端回环模式下 BER 值较高,则主要检测发送端幅值,衰减设置,发送侧滤波器参数设置,接收端DFE 设置,CDR 设置以及和时钟相位偏移相关的设置。

PRBS:串行总线的物理层测试通常分为发射机测试和接收机测试,又称为 TX 测试和 RX 测试。发射机测试通常包括眼图、抖动、信号波形、幅度、上升下降时间等测试项目,接收机测试通常包括误码率、抖动容限、接收机灵敏度等测试项目。对于眼图测试、误码率和抖动容限测试,最常用的测试码是 PRBS,主要有 PRBS7、PRBS15、PRBS23 和 PRBS31。

PRBS7 是目前 10Gbps 以下的串行总线中最常用的测试码型,在 ITU-TV.29 规范中规定。PRBS7 属于短伪随机码型,与 8b10b NRZ 编码的数据流很相似,所以,在 PCIe、SATA、XAUI、1000BASE-LX、FC、SAS 等采用 8b10b 编码的串行总线中,PRBS7 是最常用的测试码型,支持这些总线的芯片通常都可以输出 PRBS7 测试码型,用于眼图、抖动或误码率测量。PRBS31是一种较长的伪随机码型,其多项式为X31+X28+1,码长为2^31-1个比特。PRBS31的码流中最长的连1为31个,最长的连0为30个,包含了相当多的低频成分,因此适用于像SONET/SDH信号那样包含了很多低频成分的物理层测量。PRBS31也是10 Gigabit Ethernet推荐的测试码型之一。

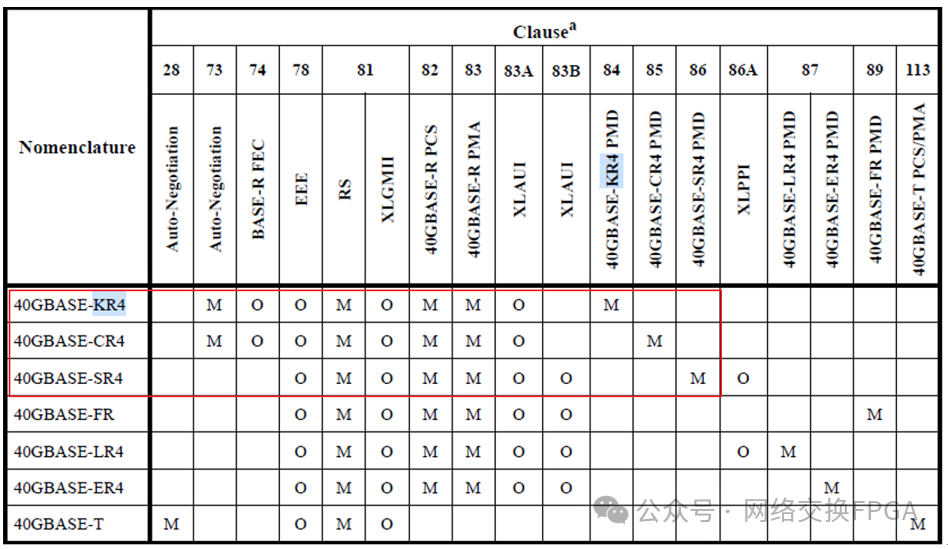

KR:背板传输;CR:铜线互联;SR:短距光纤传输。

-

基于FPGA的以太网ARP通信测试(二)2023-11-06 2824

-

Serdes到Serdes 10G以太网连接是T2080上的一个功能选项,通过光纤或跨背板时会失败的原因?2023-04-27 908

-

40G以太网光模块解决方案2022-09-08 2602

-

超远程40G以太网子系统的远端回路问题如何解决2020-05-22 1419

-

40G光模块选购指南2019-10-23 2757

-

基于FPGA的10G以太网光接口设计2019-05-31 2460

-

详解FPGA的10G以太网接口调试2019-03-03 19500

-

部署40G以太网时要考虑哪些因素?2018-12-13 2121

-

分析25G以太网架构能否取代40G2018-06-27 6236

-

英特尔低延迟 40G 以太网 MAC 和 PHY IP的延迟计算2018-06-20 7509

-

解密易飞扬40G QSFP+ PSM4光模块2017-06-05 4045

-

40G QSFP+光模块的完美链接-Cisco Nexus 6004交换机2016-08-24 3742

-

基于FPGA的万兆以太网接口的设计与实现2012-08-11 11258

-

基于FPGA的万兆以太网接口设计2011-07-20 1936

全部0条评论

快来发表一下你的评论吧 !