PCB设计经验总结

电子说

描述

我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。

和SERDES应用相关的高速系统PCB设计注意事项如下:

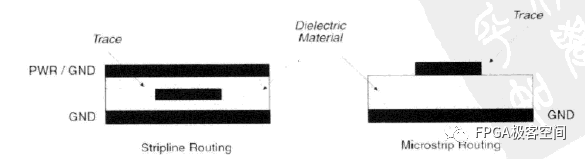

(1)微带(Microstrip)和带状线(Stripline)布线。

微带线是用电介质分隔的参考平面(GND或Vcc)的外层信号层上的布线,这样能使延迟最小;带状线则在两个参考平面(GND或Vcc)之间的内层信号层布线,这样能获得更大的容抗,更易于阻抗控制,使信号更干净,如图所示。

微带线和带状线最佳布线

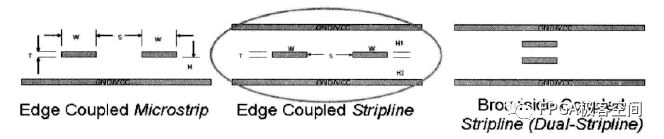

(2)高速差分信号对布线。

高速差分信号对布线常用方法有边沿耦合(Edge Coupled)的微带(顶层)、边沿耦合的带状线(内嵌信号层,适合布高速SERDES差分信号对)和Broadside耦合微带等,如图所示。

高速差分信号对布线

(3)旁路电容 (BypassCapacitor)。

旁路电容是一个串联阻抗非常低的小电容,主要用于滤除高速变换信号中的高频干扰。在FPGA系统中主要应用的旁路电容有3种:高速系统(100MHz~1GHz)常用旁路电容范围有0.01nF到10nF,一般布在距离Vcc 1cm以内;中速系统(十几兆赫兹100MHz),常用旁路电容范围为47nF到100nF钽电容,一般布在Vcc 3cm以内;低速系统(十几兆赫兹以下),常用旁路电容范围为470nF到3300nF电容,在PCB上布局比较自由。

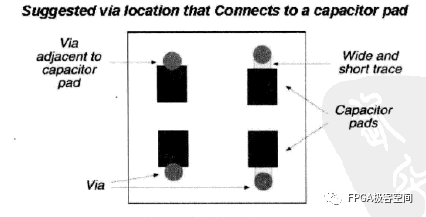

(4)电容最佳布线。

电容布线可遵循下列设计准则,如图所示。

电容最佳布线

使用大尺寸过孔(Via)连接电容引脚焊盘,以减少耦合容抗。

使用短而宽的线连接过孔和电容引脚的焊盘,或者直接将电容引脚的焊盘与过孔相连接。

使用LESR电容(Low Effective Series Resistance,低串联阻抗电容)。

每个GND引脚或过孔应该连接到地平面。

(5)高速系统时钟布线要点。

避免使用锯齿绕线,时钟布线要尽可能笔直。

尽量在单一信号层布线。

尽可能不使用过孔,因为过孔将带来强烈的反射和阻抗不匹配。

尽量在顶层用微带布线,从而避免使用过孔且使信号时延最小。

将地平面尽量布在时钟信号层旁,用以减少噪音和串扰。如果使用内部信号层布时钟线,可以使用两个地平面将时钟信号层夹在中间,以减少噪声和干扰。缩短信号时延。

时钟信号应该正确阻抗匹配。

(6)高速系统耦合与布线注意事项。

注意差分信号的阻抗匹配。

注意差分信号线的宽度,使之可以容忍20%的信号上升或下降时间。

使用合适的连接器,连接器的额定频率应该能满足设计的最高频率。

差分信号对尽量使用edge-couple方式耦合,避免使用broadside-couple方式耦合,使用3S分式法则,避免过耦合或串扰。

(7)高速系统噪声滤波注意事项。

减少电源噪声带来的低频干扰(1KHz以下),在每个电源接入端加屏蔽或者滤波电路。

在每处电源进入PCB的地方加100F的电解电容滤波。

为了减少高频噪音,在每处Vcc和GND处尽可能多地布置去耦合电容。

将Vcc和GND平面平行布置,并用电介质(如FR-4PCB)分隔,在其他层布置旁路电容。

(8)高速系统地弹(Ground Bounce)

尽量在每处Vcc/GND信号对上添加去耦合电容。

在计数器等高速翻转信号的输出端加外部Buffer,以减少驱动能力的要求。

将为使用的用户I/O设置成输出为低电平的输出信号,这相当于虚拟的GND,将这些低电平输出连接到地平面。

对于速度要求不苛刻的输出信号设置为Slow Slew (低上升斜率)的模式。

控制负载容抗。

减少时钟不停翻转的信号,或者将这种信号尽量均匀地分布在芯片的四周。

将翻转频繁的信号尽量靠近芯片的GND引脚布置。

设计同步时序电路时应该尽量避免输出瞬时全部翻转。

将电源和地引岔开布置,这样可以起到在整体上中和电感的作用。

- 相关推荐

- pcb

全部0条评论

快来发表一下你的评论吧 !