XILINX FPGA CLB单元之移位寄存器

描述

一、移位寄存器

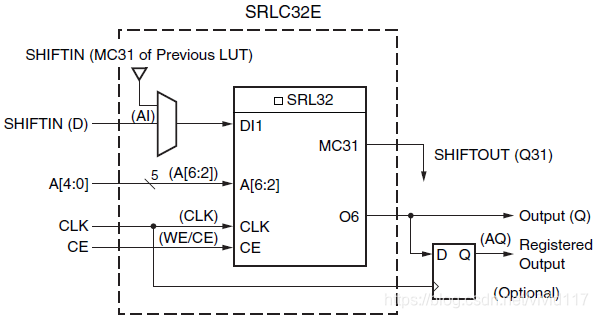

SLICEM函数发生器也可以配置为32位移位寄存器,而无需使用slice中可用的触发器。以这种方式使用,每个LUT可以将串行数据延迟1到32个时钟周期。

移入D(DI1 LUT引脚)和移出Q31(MC31 LUT引脚)线路将LUT级联,以形成更大的移位寄存器。因此,SLICEM中的四个LUT被级联以产生高达128个时钟周期的延迟。也可以在多个SLICEM上组合移位寄存器。

寄存器,LUT B / C / D的MC31输出也不可用。由此产生的可编程延迟可用于平衡数据流水线的时序。

下图是SRL32位移位寄存器的框图:

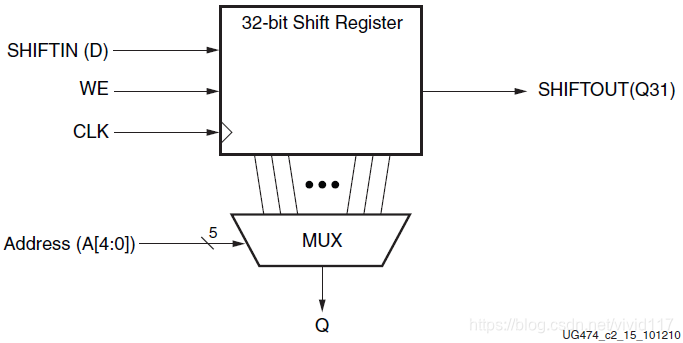

下图是占用一个32位函数发生器的示例移位寄存器配置

二、 移位寄存器的功能与应用

移位寄存器的功能

1)写操作

2)与时钟输入(CLK)和可选的时钟使能(CE)同步

3)修复对Q31的读取访问

4)动态读取访问

5)通过5位地址总线A [4:0]执行

LUT地址的LSB未使用,软件自动将其绑定为逻辑高电平。

6)通过改变地址可以异步读取32位中的任何一位(在O6 LUT输出上,在原语上称为Q)

7)此功能对于创建较小的移位寄存器(少于32位)很有用。

例如,当构建13位移位寄存器时,将地址设置为第13位。

8)存储单元或触发器可用于实现同步读取。

触发器的时钟输出决定了总延迟并改善了性能。但是,增加了一个时钟延迟周期。

移位寄存器的应用:

1)延迟或延迟补偿

2)同步FIFO和内容可寻址存储器(CAM)

三、XILINX FPGA 中LUT 中移位寄存器的复用情况

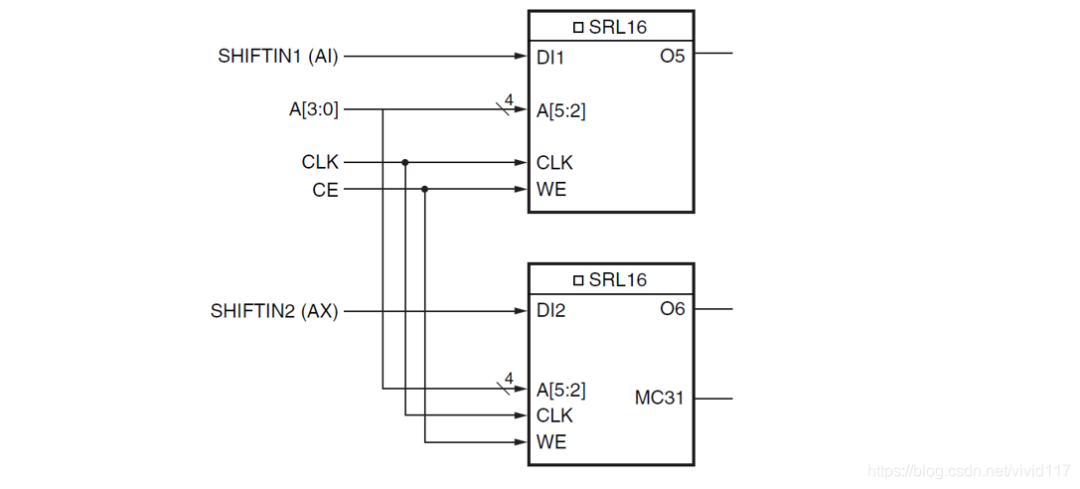

一个LUT可以用于产生2个16bit移位寄存器,地址是复用的。

用两个SRL16组成一个32位的移位寄存器

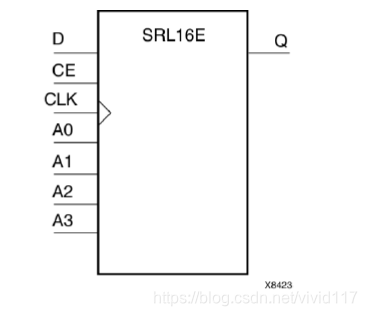

下图是一个SRL 16E 带使能信号的移位寄存器:

移位寄存器查找表,它的输入这是一个移位寄存器查找表,它的输入 A3,A2,A1和 A0选择移位输出的长度。

移位寄存器可以是固定的、静态的长度,移位寄存器的长度可以从 1位到 16位不等,由下面公式决定:

长度 =(8 x A3)+(4 x A2)+(2 x A1)+A0+1

如果 A3,A2,A1,A0都是 0(0000),移位寄存器的长度就是 ),移位寄存器的长度就是 1位长;如果它们 都是 1(1111),移位寄存器的长度就是 ),移位寄存器的长度就是 ),移位寄存器的长度就是 16位长。

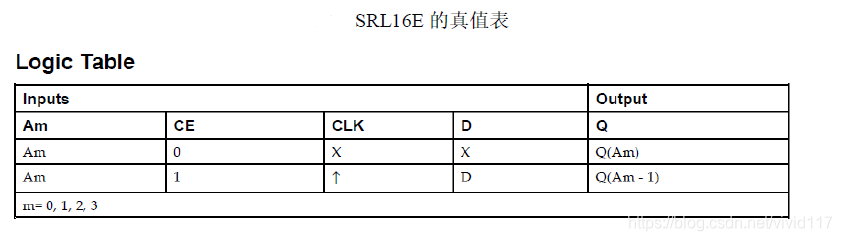

下表是SRL16E的真值表:

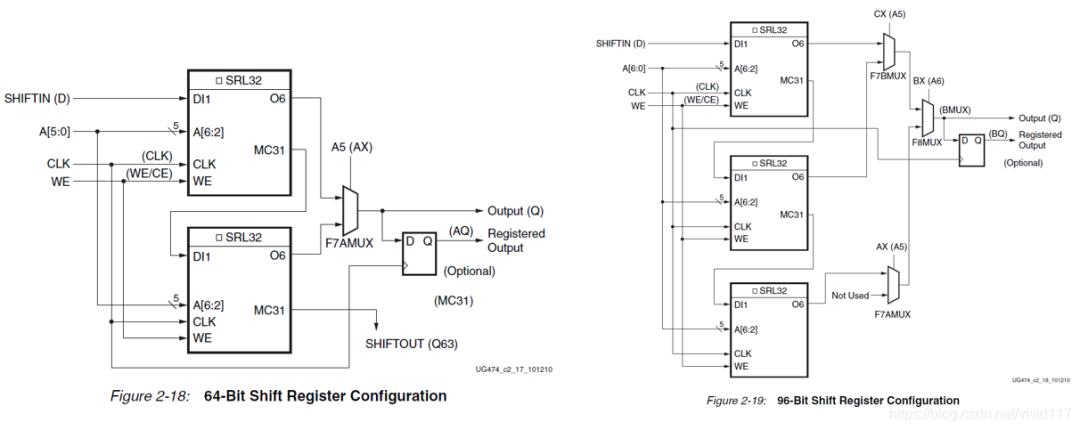

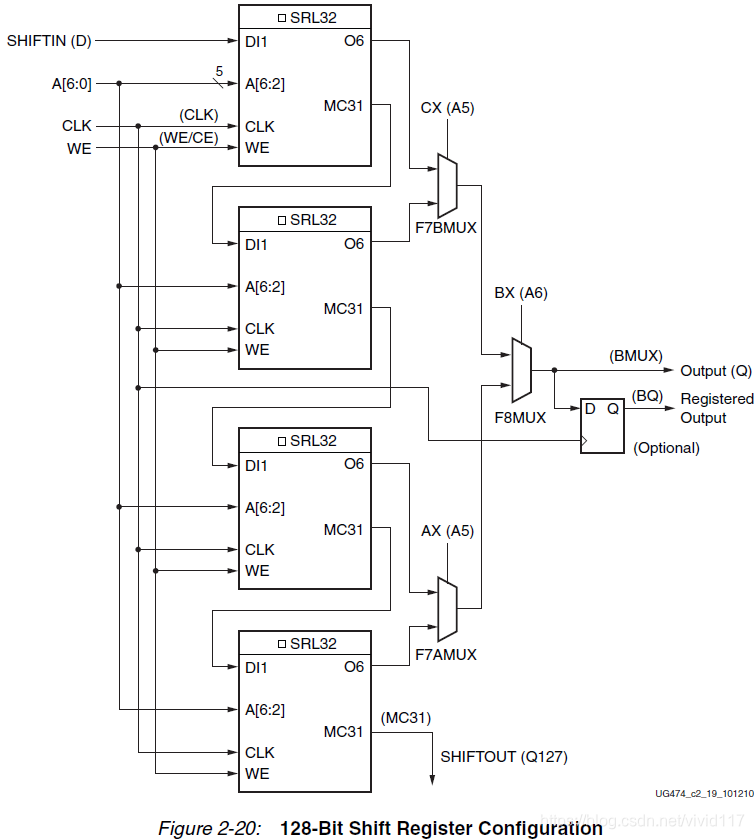

2.利用SRL32 组成 64/96/128 bit的移位寄存器,利用地址A5和F7AMUX切换SRL32

四、移位寄存器数据流

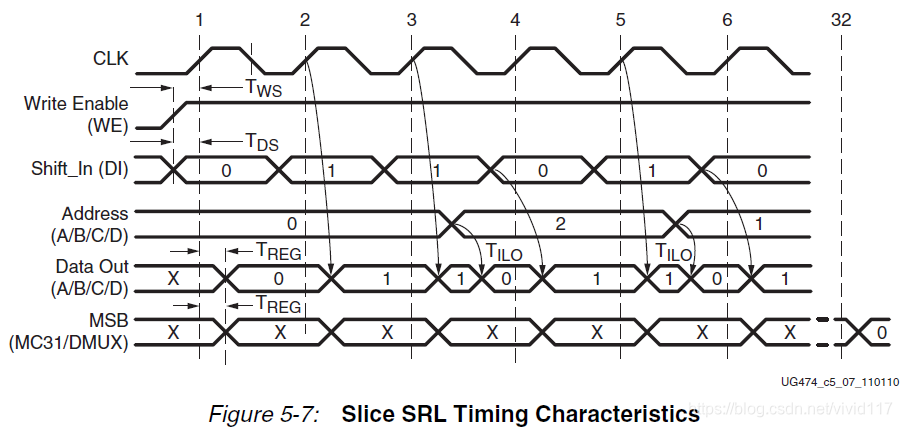

下图举例说明在7系列FPGA Slice(一个配置为SRL的LUT)中实现的移位寄存器的时序特性:

-

移位寄存器右移是怎么移位的2024-07-12 5278

-

移位寄存器的工作原理 移位寄存器左移和右移怎么算2024-01-18 14891

-

Xilinx SRL16E如何实现16移位寄存器2022-08-27 1943

-

Xilinx FPGA中SRL移位寄存器的资源介绍2020-12-31 2428

-

移位寄存器的原理2019-07-15 77635

-

移位寄存器实验报告_移位寄存器原理2017-12-22 29639

-

寄存器与移位寄存器2016-05-20 1320

-

基于FPGA的可变长度移位寄存器优化设计2011-07-23 6097

-

移位寄存器,移位寄存器是什么意思2010-03-08 18278

-

线性移位寄存器2010-01-12 2294

全部0条评论

快来发表一下你的评论吧 !