MOS管特征频率与过驱动电压的关系

描述

文章来源:学习那些事

原文作者:赵先生

本文简单介绍了MOS管特征频率与过驱动电压的概念以及二者的关系。

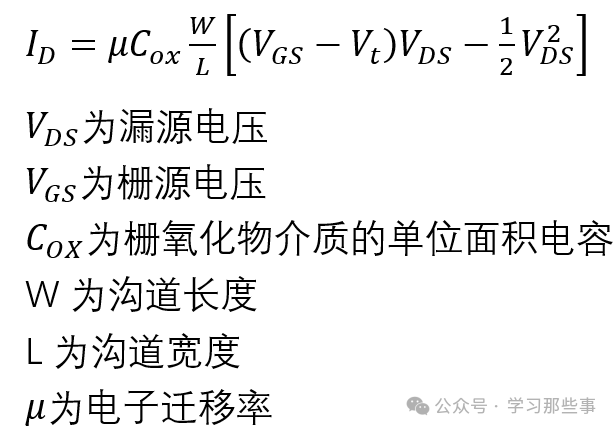

跨导效率的定义

针对放大器的设计,在满足特定的增益与带宽要求时,追求低功耗是至关重要的。从晶体管的微小信号模型参数来看,理想状态是晶体管在提供所需跨导gm(跨导与本征增益及带宽呈正相关)的同时,保持较低的电流消耗ID(与功耗直接相关)。基于此,我们引入了晶体管的跨导效能概念,它定义为晶体管跨导gm与电流ID的比率。结合如下长沟道模型的公式:

我们可以进一步推导出:

通过该式可以看出晶体管的跨导性能主要依赖于其过驱动电压VOV的大小。如果要增强晶体管的跨导性能,理论上应尝试减小其过驱动电压VOV。但是长沟道模型并不精确,特别是在VOV较低的情况下,上式不成立。在实际电路设计实践中,不能单纯通过降低VOV来无限制地提高跨导性能,因为还需要兼顾晶体管的其他关键参数,例如特征频率。因此,跨导性能的优化应在确保晶体管综合性能合理的范围内进行。

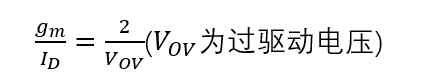

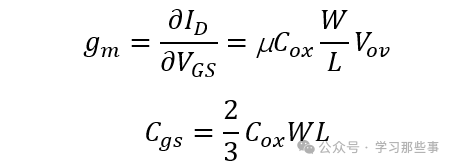

特征频率的定义

除了追求高效的跨导效率,放大器的高带宽特性同样重要,这要求晶体管的本征电容C保持在较低水平。为此,我们设定了一个新的性能指标:晶体管跨导gm与电容Cgs的比值,该比值以弧度每秒(rad/s)为单位,称为特征角频率ωT。为了更直观地理解,我们也可以将其转换为赫兹(Hz)作为单位,即特征频率fT。据以下两个式子

我们可以得到特征角频率的具体表达式为

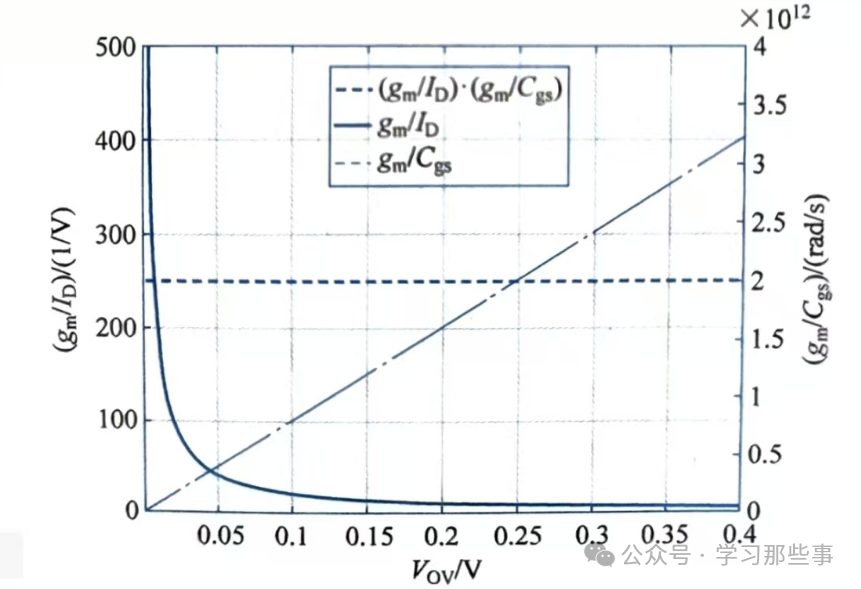

与跨导效率相似,在特定工艺条件下,固定长度的晶体管其特征频率也主要由过驱动电压VOV来决定。为了获得既低功耗又高速的优异性能,我们期望这两个参数都能尽可能大。然而,根据计算结果,它们随VOV的变化趋势却是相反的,如下图所示。具体而言,当VOV较低时,晶体管的gm/ID比值较高,意味着功耗较低、能效较高,但此时gm/Cgs比值较小,意味着电容较大、带宽较窄、速度较慢。相反,当VOV较高时,虽然电路的速度快,但能效降低、功耗增加。这凸显了电路设计中一个固有的矛盾,即在能量效率与速度之间需要进行折中(trade-off)。这种特性不仅限于模拟电路,在数字电路中同样存在。例如,数字电路中的“近阈值计算”技术,就是通过减小晶体管的过驱动电压来提高能效,但这同时也会降低电路的运行速度。

晶体管性能指标随过驱动电压的变化趋势

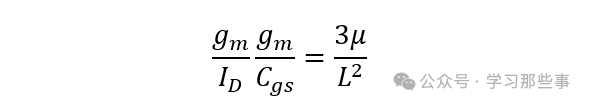

为了全面评估这两个参数的综合影响,我们可以将它们相乘,可得

观察上式可以发现,两个参数的乘积主要取决于迁移率μ以及晶体管的沟道长度L,这是两个仅与器件本身特性相关的因素,而与过驱动电压VOV无关。因此,为了进一步提升晶体管的综合性能,我们希望迁移率μ尽可能高,同时晶体管的沟道长度L尽可能短。

迁移率的高低在很大程度上受到制作器件所选材料的影响。半导体工艺中广泛应用了各种具有高迁移率的材料,如砷化镓(GaAs)、磷化铟(InP)等III-V族化合物,以显著提升器件性能。相比之下,薄膜晶体管、有机化合物晶体管等由于迁移率较低,其应用范围相对有限。而晶体管的沟道长度则由集成电路的工艺水平决定。随着工艺的不断发展,晶体管沟道的最小长度逐渐减小,从而推动了晶体管整体性能的提升。这使得我们可以在保持相同能量效率的同时提高电路速度,或者在保持相同速度的同时降低电路功耗,这就是工艺进步所带来的显著优势。当然,工艺进步对模拟电路设计的影响相当复杂,并非总是像对数字电路那样带来直接的好处。随着学习的深入,我们将会发现工艺进步也会给模拟电路设计带来不少挑战。

提到工艺的进步,就不得不说起“摩尔定律”。英特尔的创始人之一戈登·摩尔曾预言,晶体管沟道的最小长度大约每4年就会减半。在过去的几十年里,集成电路产业一直沿着这一预测的速度发展。1970年,集成电路工艺的特征尺寸为10微米,而到了2017年,这一数字已经缩小到10纳米,与摩尔定律的预测基本相符,不过如今我们正逐步进入超摩尔时代。关于工艺进步的内容这里就不再过多赘述。

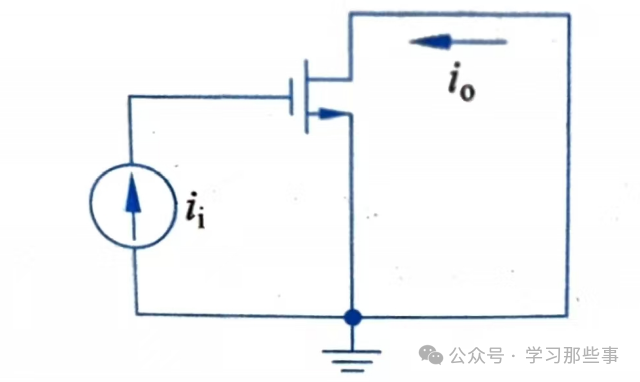

特征频率是衡量电路速度的一个关键指标,从器件物理学的角度来看,它是晶体管的一个核心参数。考虑图示的电路,其中省略了偏置电路部分。

晶体管特征频率的测试电路示意图

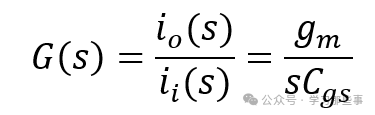

将晶体管视为电流放大器,我们可以根据小信号模型推导出电流增益的表达式,即

随着频率的升高,电流增益会逐渐降低。当电流增益的幅度降至1时,晶体管将失去电流放大的功能,此时的频率即为特征频率。从这个角度出发,我们也可以推导出晶体管特征角频率的表达式。

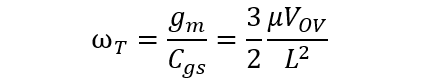

特征频率与过驱动电压的关系

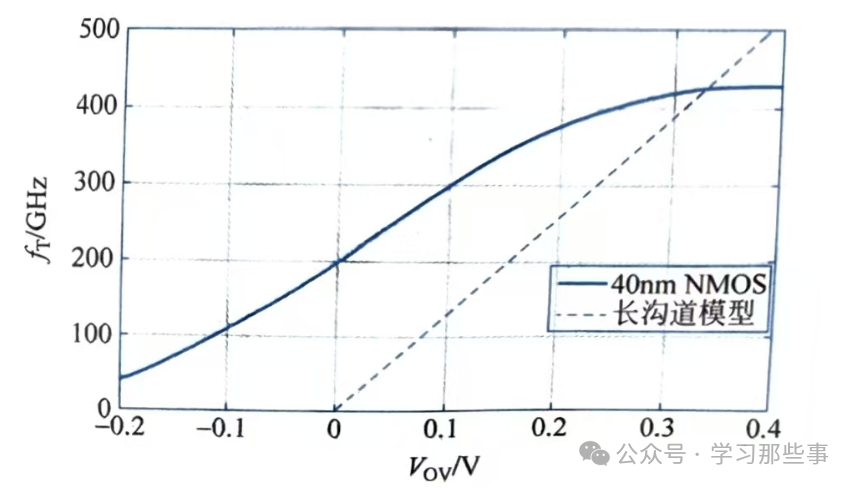

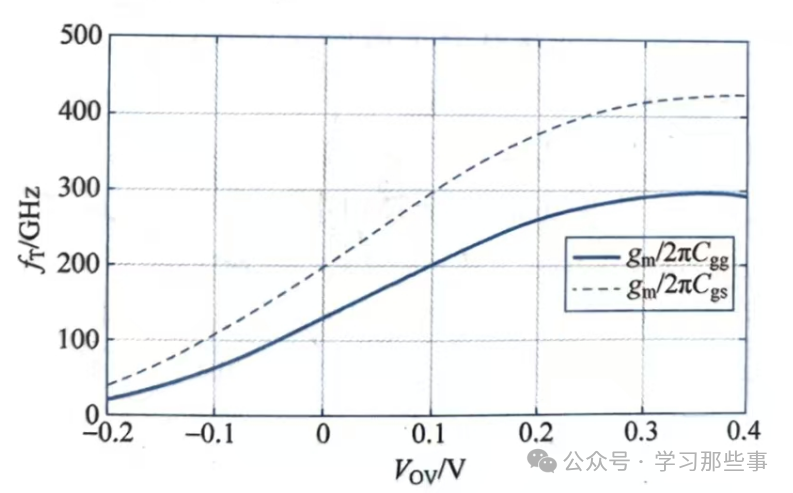

晶体管特征频率fT(fT=gm/2πCgs)随过驱动电压VOV的变化趋势如下图中的实线所示,而虚线则是基于长沟道模型的分析预测。

晶体管特征频率扫描曲线

长沟道模型的预测结果与仿真结果之间存在显著差异。在亚阈值区,长沟道模型认为晶体管处于截止状态,跨导为0,因此特征频率也为0。然而,实际上晶体管在亚阈值区仍然具有一定的跨导和电流,所以实际的特征频率fT并不为0,只是数值相对较低。值得注意的是,在40nm工艺下,即使VOV<0,fT仍然可以超过100GHz。对于许多对电路工作速度要求不高,但对功耗要求严格的应用场景,将晶体管偏置在亚阈值区工作是一个合适的选择。例如,在生物电信号(如EEG或ECG)采集电路中,由于信号频率仅在kHz量级,即使晶体管工作在亚阈值区也能满足速度要求,并且可以获得较高的跨导效率gm/ID,从而节省功耗。在中等反型区,预测曲线和仿真曲线的斜率都与VOV成正比,但数值上仍有明显差异。而在强反型区,仿真曲线出现明显的弯曲,fT呈现出饱和趋势,这是由于短沟道效应导致的下降所致。

总体来看的话,尽管长沟道模型对特征频率的预测曲线与仿真曲线存在较大差异,但两者的变化趋势是一致的(均随VOV增大而增大),这为电路设计中的参数调整提供了一定的指导方向。

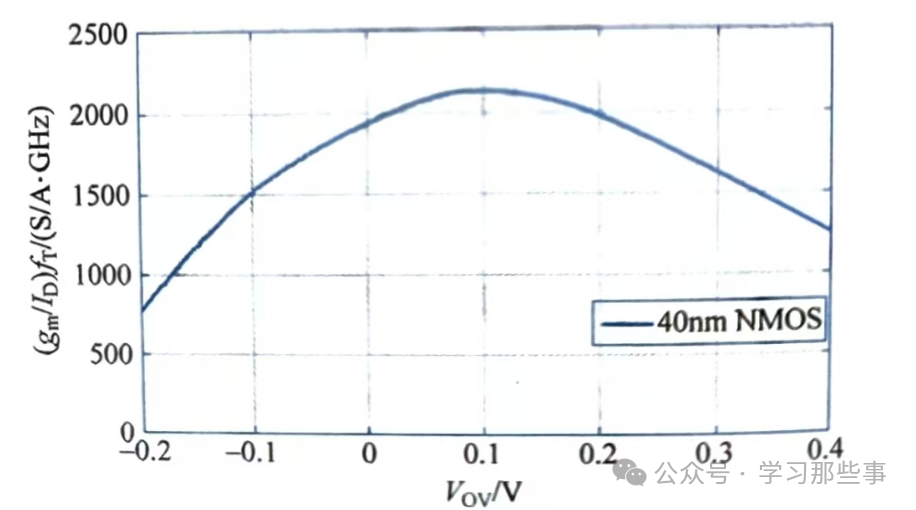

上文中提到,根据长沟道模型的预测,特征频率与跨导效率的乘积是一个与过驱动电压VOV无关的常数,仅取决于器件本身的特性。而实际器件的仿真结果如下图所示。

晶体管特征频率与跨导效率乘积的仿真曲线

在VOV较小时,仿真得到的跨导效率趋于饱和状态;而在VOV较大时,特征频率则趋于饱和。因此,在这两个区域内,跨导效率与特征频率的乘积曲线都会偏低。然而,在过驱动电压约为100mV的中等反型区,仿真曲线相对平稳且取值较高,为速度和功耗之间提供了良好的折中方案。这也是大多数模拟电路偏置设计的首选区域。相比之下,亚阈值区更适合于低功耗但对速度要求不高的模拟电路,如心脏起搏器、生物电信号采集电路等。而强反型区则更适用于对速度要求高,但对功耗相对不敏感的应用场景,例如高速有线接口电路、毫米波射频电路等。

为了更准确地分析和理解特征频率,上述定义仅考虑了晶体管的本征电容Cgs。但是在实际电路设计中,晶体管的寄生电容对电路性能也有显著影响,不能简单忽略。因此,我们需要对特征频率进行修正。

考虑晶体管的寄生电容后,特征频率随过驱动电压的变化情况如图所示。由于寄生电容的影响,晶体管的特征频率取值有所降低。

考虑寄生电容的晶体管特征频率扫描曲线

-

MOS管的导通电压与漏电流关系2024-11-05 5277

-

MOS管导通电压和温度的关系2024-07-23 9544

-

MOS管特征频率ft的影响因素是什么?2023-09-18 5445

-

什么会影响MOS管驱动电压降低呢?2023-09-05 2812

-

变频器供电时永磁电机振动噪声源的特征频率是怎样的2022-02-25 1918

-

MOS管驱动电压最大是多少2021-11-12 2034

-

MOS管驱动电压最大是多少-KIA MOS管2021-11-07 3395

-

请问带宽/特征频率/截止频率/-3dB是什么意思?2021-10-12 4540

-

MOS管驱动电路_单片机如何驱动MOS管2020-06-26 84483

-

什么是特征频率2019-08-23 6804

-

基于EMD相关去噪的风电机组振动噪声抑制及特征频率提取_李辉2017-01-08 884

-

labview中怎样获得频率-幅值曲线,从而对比故障特征频率找出故障。2015-09-08 4608

-

请问在ORCAD中如何修改三极管的特征频率参数【在线等急......2012-10-10 10280

-

什么是特征频率/截止频率2010-03-05 28409

全部0条评论

快来发表一下你的评论吧 !