FinFET制造工艺的具体步骤

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了FinFET(鳍式场效应晶体管)制造过程中后栅极高介电常数金属栅极工艺的具体步骤。

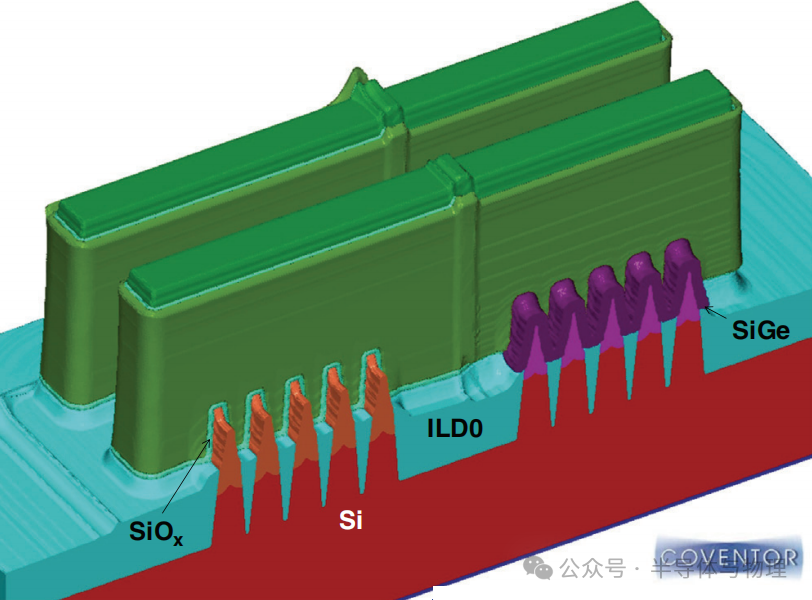

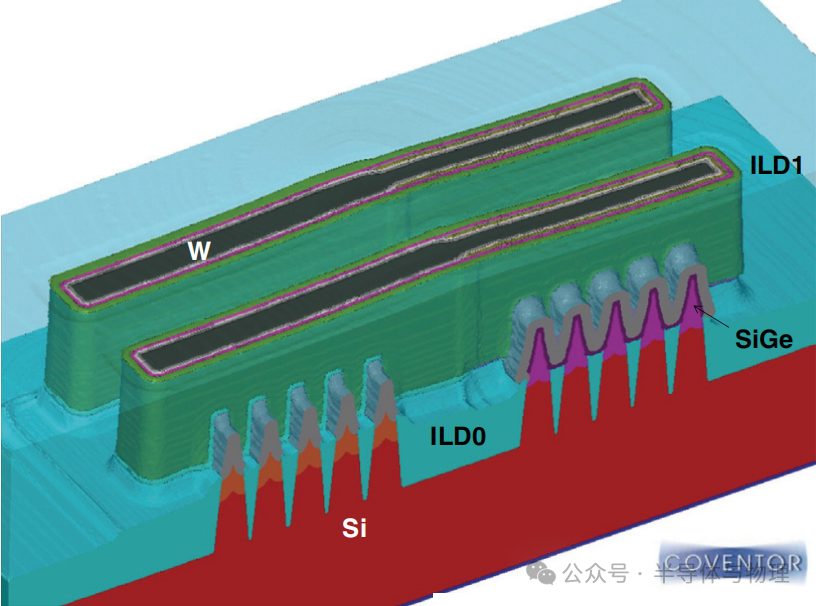

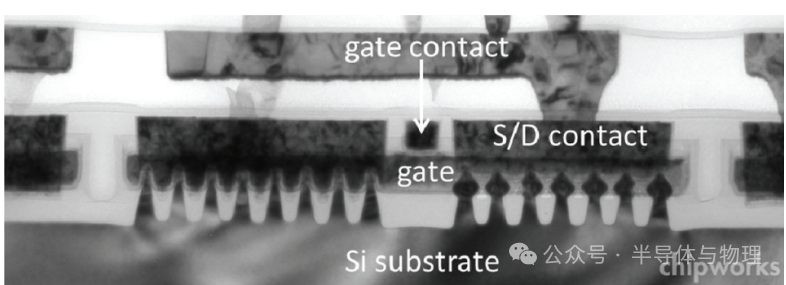

在FinFET(鳍式场效应晶体管)制造过程中,当自对准硅化物(self-aligned silicide, salicide)过程完成,在源(Source)和漏(Drain)区形成了低电阻接触之后,晶圆就准备好进入替换栅极(replacement gate)或称为后栅极(gate-last)高介电常数金属栅极(High-k Metal Gate, HKMG)工艺阶段。以下是该过程中每一步骤的具体内容及其作用:

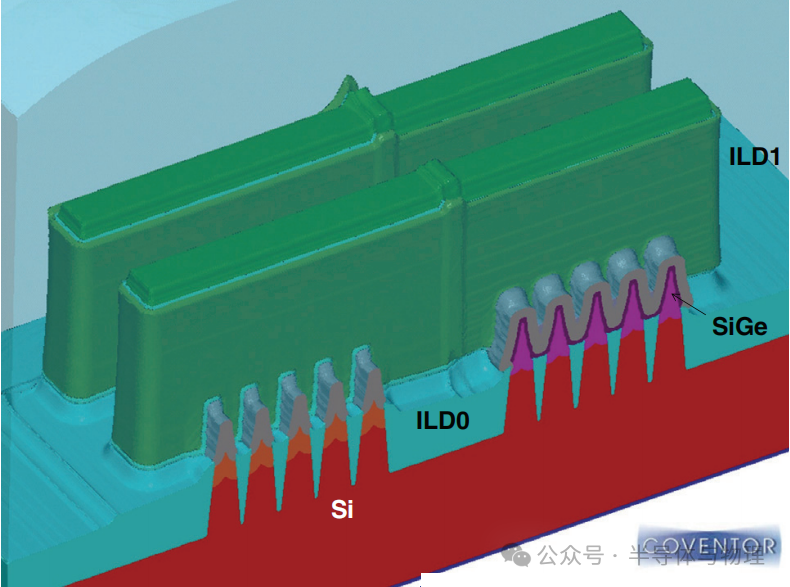

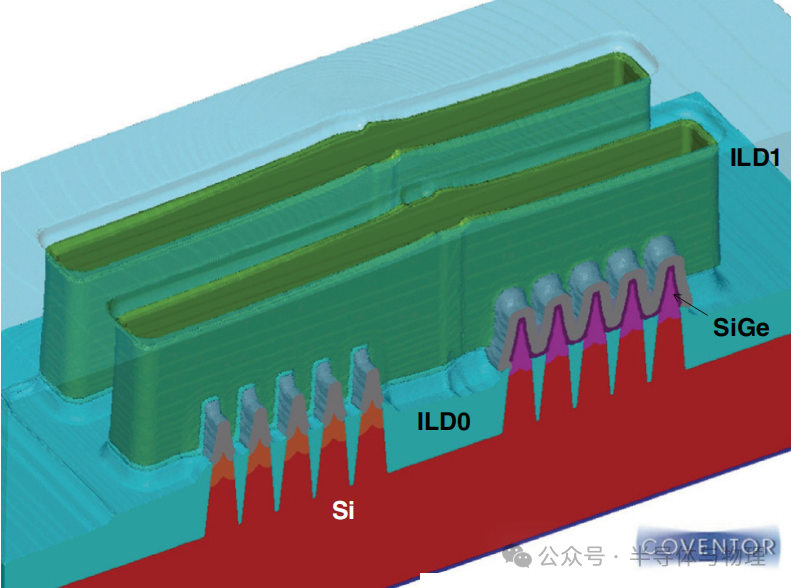

1. ILD1沉积

步骤描述:首先,在已经形成的源漏极区域上沉积一层绝缘层材料ILD1(Inter Layer Dielectric 1)。这一步骤的主要目的是为后续CMP平坦化提供一个平整的基础,并且作为栅极和其他结构之间的绝缘层。

作用解释:

提供平坦化基础: 确保接下来的CMP处理能够顺利进行。

绝缘功能: 防止不同导电层之间的短路问题。

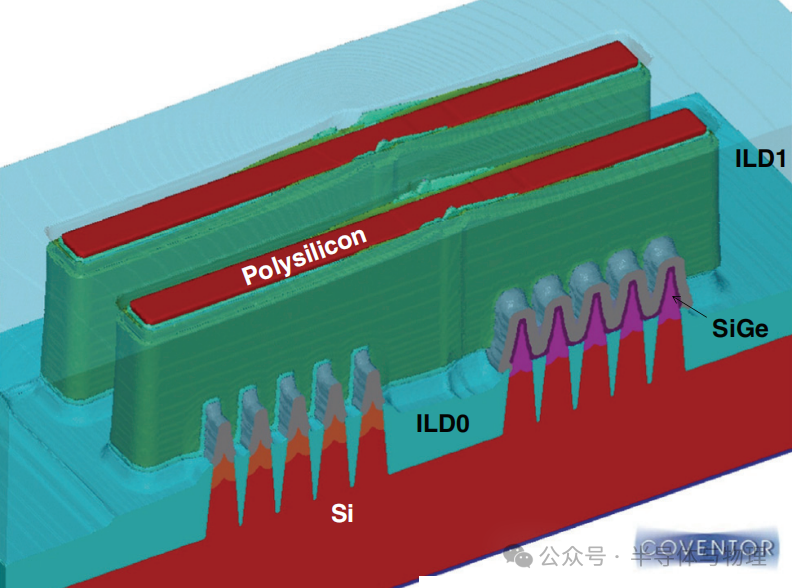

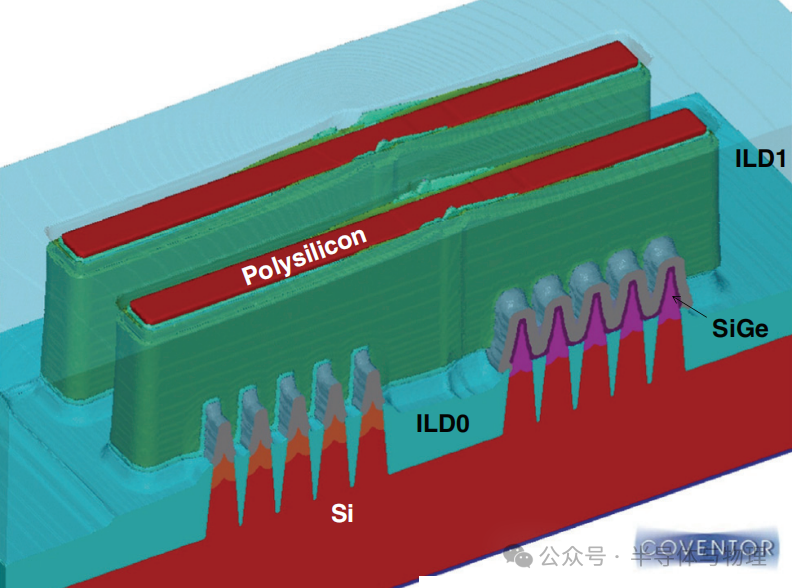

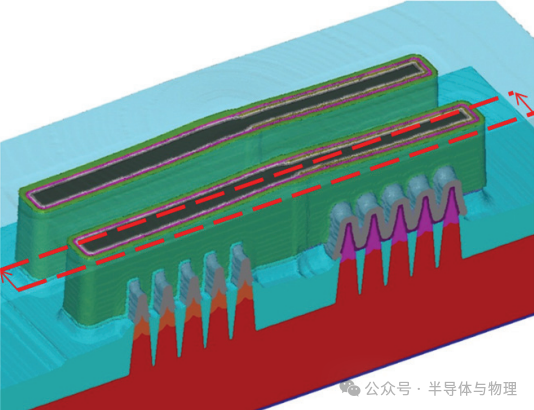

2. CMP平坦化

步骤描述:使用化学机械平坦化(Chemical Mechanical Polishing, CMP)技术去除部分ILD1,暴露出之前用作占位符的伪多晶硅栅极(dummy polysilicon gates)。

作用解释:

暴露伪栅极: 使得后续可以准确地移除这些临时栅极。

表面平整度: 确保后续工艺中材料沉积的一致性和均匀性。

3. 伪栅极移除与清洁

步骤描述:接下来,通过湿法蚀刻等工艺移除伪多晶硅栅极及其上的氧化层,并进行彻底清洗以保证界面干净无污染。

作用解释:

准备新栅极位置: 为新的HKMG结构腾出空间。

确保高质量界面: 清洁后的界面有助于提高新材料的附着质量。

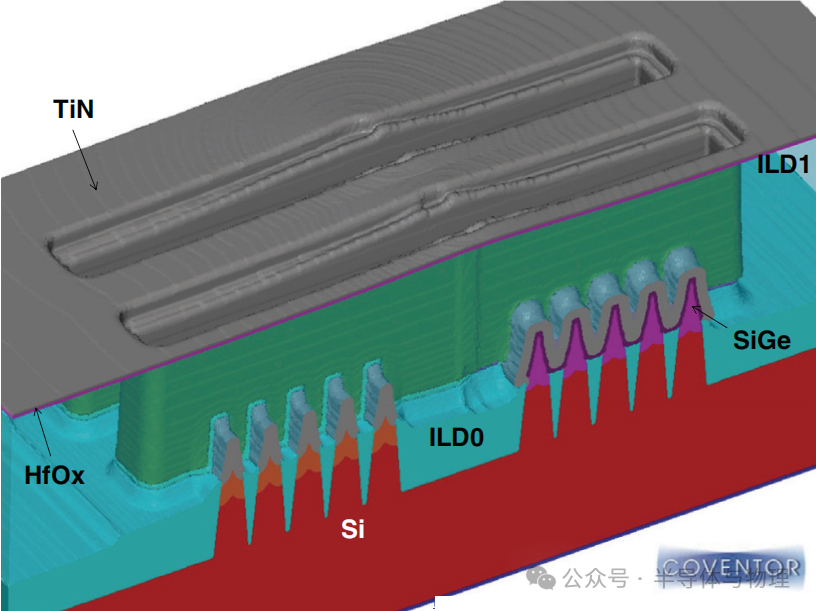

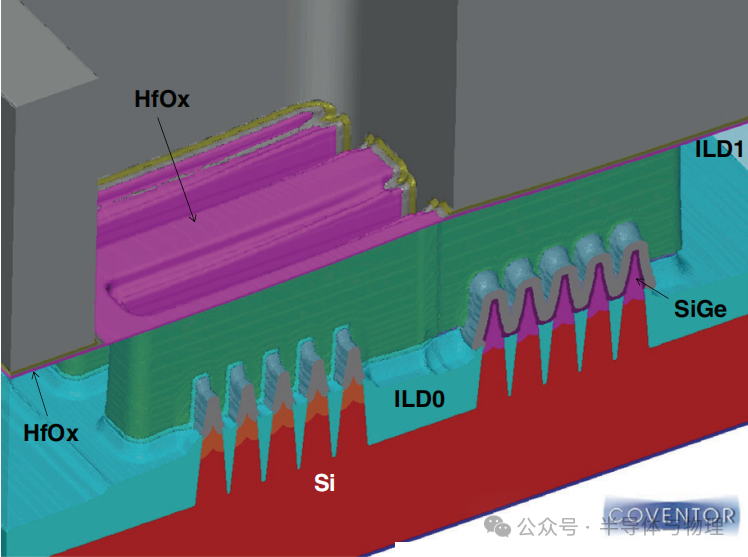

4. 高k介电材料沉积

步骤描述:采用原子层沉积(Atomic Layer Deposition, ALD)技术,在清理后的区域沉积一层铪基高介电常数材料(如HfO2),作为新的栅极绝缘层。

作用解释:

改善电气性能: 减少栅极泄漏电流并提升晶体管性能。

控制阈值电压: 高k材料的选择对于调整晶体管的工作点至关重要。

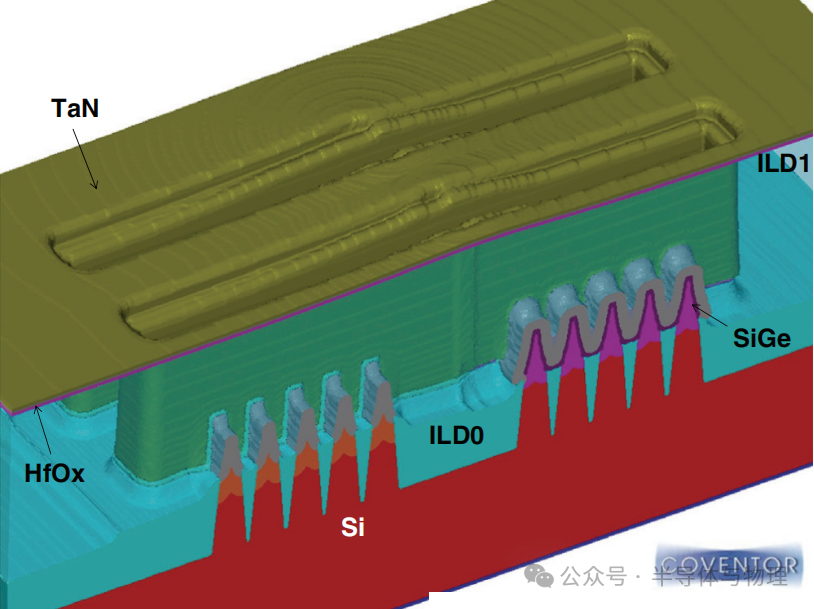

5. 功函数金属沉积

步骤描述:对于PMOS器件,接着会在其上沉积钛氮化物(TiN),它将作为调整阈值电压的工作函数金属。随后还会沉积钽氮化物(TaN)作为屏障金属,防止后续沉积的钨扩散到高k介电层中。

作用解释:

调节阈值电压: TiN用于设定PMOS器件的功函数,从而影响其开启/关闭特性。

阻挡层功能: TaN阻止其他金属成分扩散,保护高k介电层。

6. NMOS掩模应用与选择性蚀刻

步骤描述:为了处理NMOS区域,需要对整个晶圆表面涂覆光刻胶,并应用NMOS掩模来保护PMOS区域,而暴露出来的NMOS区域则会被蚀刻掉TaN屏障层和TiN PMOS工作函数金属。

作用解释:

保护PMOS: 确保PMOS区域不受下一步蚀刻的影响。

暴露NMOS: 准备NMOS区域接受特定的工作函数金属。

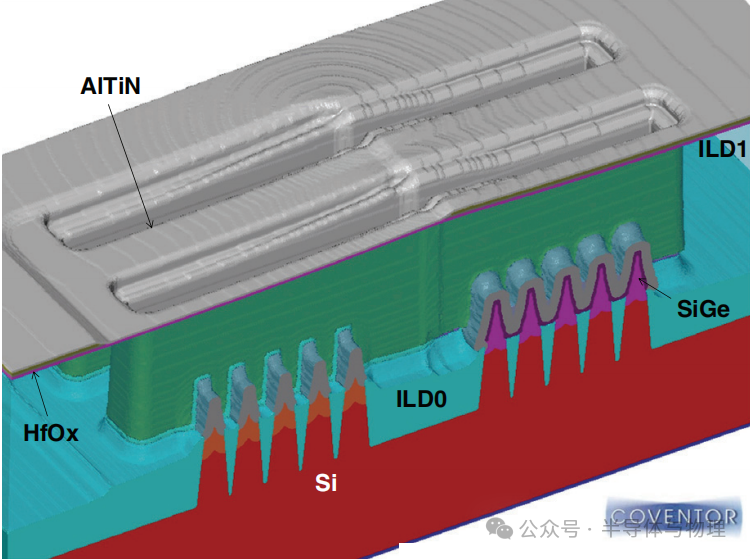

7. NMOS功函数金属沉积

步骤描述:移除光刻胶并再次清洗晶圆后,利用ALD技术在NMOS区域沉积适合的功函数金属,例如钛铝氮化物(TiAlN),用于调整NMOS器件的阈值电压。

作用解释:

定制NMOS阈值电压: TiAlN等材料用于优化NMOS晶体管的性能。

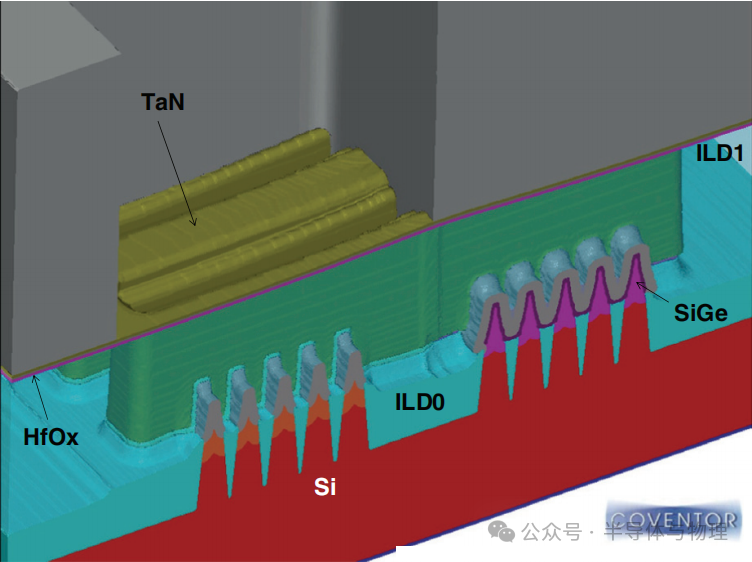

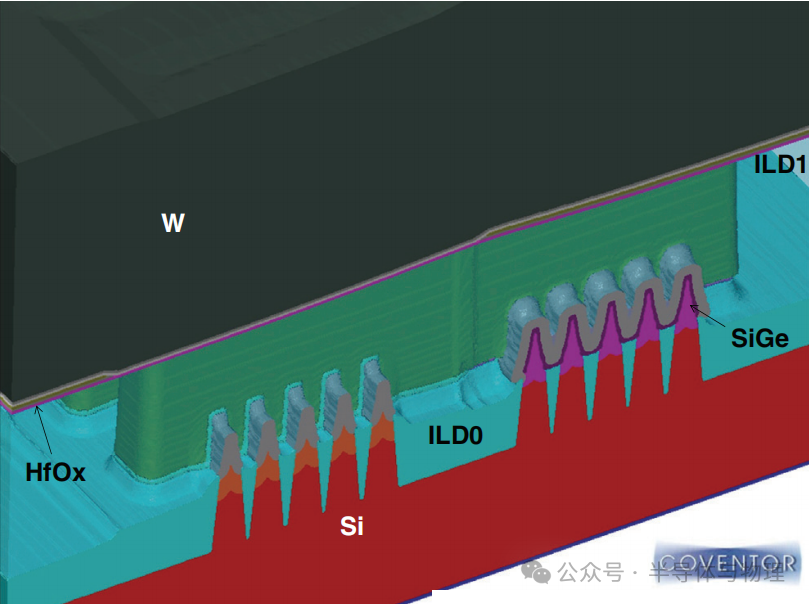

8. 粘附层沉积与WCMP填充

步骤描述:最后,沉积一层钛氮化物(TiN)作为粘附层,然后进行钨化学机械抛光(WCMP),以填充栅极沟槽。WCMP过程中,过量的钨以及其他金属层被去除,只留下位于栅极沟槽内的HKMG结构。

作用解释:

增强粘合强度: TiN作为中间层增加了金属与下方结构之间的结合力。

精确填充: WCMP确保了栅极沟槽被充分但不过度填充。

9. 过抛光

步骤描述:所有其他金属层和高k介电层都会在过抛光步骤中从晶圆表面去除,只留下位于栅极沟槽内的HKMG结构。

作用解释:

清除多余材料: 确保最终产品具有良好的电气特性和可靠性。

表面平整: 为后续工艺提供一个平滑的工作面。

-

打开FSP配置器界面的具体步骤2025-05-06 1604

-

聊聊Rust与C语言交互的具体步骤2023-07-06 2352

-

22nm技术节点的FinFET制造工艺流程2023-12-06 9064

-

STM32WB配置SMPS模块具体步骤是什么?2024-03-20 1127

-

上位机与下位机通信的具体步骤是什么?2012-12-17 8866

-

急需求教labview实例应用具体步骤?2013-12-22 2042

-

有关平衡杆小车的实验 具体步骤2015-07-18 2236

-

请问UCGUI中移植触摸的具体步骤是什么?2019-07-17 1992

-

STM32新建工程具体步骤2021-08-24 1081

-

学电机的具体步骤2021-08-31 1790

-

单片机开发环境搭建的具体步骤是什么?2021-09-30 1356

-

uC/OS-III移植的具体步骤有哪些2021-11-03 2232

-

MAVLink学习之路04_MAVLink移植到STM32具体步骤2020-03-07 5793

-

苹果智能手机点胶的具体步骤及资料2021-03-21 1456

-

西门子V20变频器PID控制恒压供水的具体步骤2023-04-10 1270

全部0条评论

快来发表一下你的评论吧 !