SPI通信总线的原理及工作过程简单分析

电子说

描述

概况:

SPI, 串行外围设备接口。高速的,全双工的,同步通信总线。有四个引脚:SDI(数据输入),SDO(数据输出),SCLK(时钟),CS(片选)。

应用:

常作为单片机外设芯片串行扩展接口,主要应用于EEPROM,FLASH,实时时钟,AD转换器,数字信号处理器和数字信号解码器之间。

通信原理:

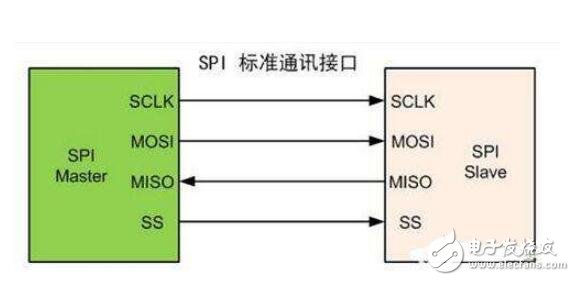

以主从方式工作

MOSI(SDO):主器件数据输出,从器件数据输入。

MISO(SDI):主器件数据输入,从器件数据输出。

SCLK :时钟信号,由主器件产生。

SPI串行传输,数据一位一位从MSB或LSB开始传输,产生相应的脉冲沿时,MOSI,MISO才进行数据传输。

CS:从器件使能信号,由主器件控制。

CS控制芯片是否被选中,只有片选信号为实现约定的使能信号时(高电位或地电位),对此芯片的操作才有效,这也就允许同一总线上连接多个SPI设备。

工作过程:

SPI可以用全双工通信方式同时发送和接收8(16)位数据,过程如下:

主机启动发送过程,送出时钟脉冲信号——>主移位寄存器的数据通过SDO移入到从移位寄存器,同时从移位寄存器中的数据通过SDI移人到主移位寄存器中——>8(16)个时钟脉冲过后,时钟停顿,主移位寄存器中的8(16)位数据全部移人到从移位寄存器中,随即又被自动装入从接收缓冲器中,从机接收缓冲器满标志位(BF)和中断标志位(SSPIF)置“1”。同理,从移位寄存器中的8位数据全部移入到主寄存器中,随即又被自动装入到主接收缓冲器中.主接收缓冲器满标志位(BF)和中断标志位(SSPIF)置“1”——>主CPU检测到主接收缓冲器的满标志位或者中断标志位置1后,就可以读取接收缓冲器中的数据。同样,从CPU检测到从接收缓冲器满标志位或中断标志位置1后,就可以读取接收缓冲器中的数据,这样就完成了一次相互通信过程。

SPI总线接口及时序

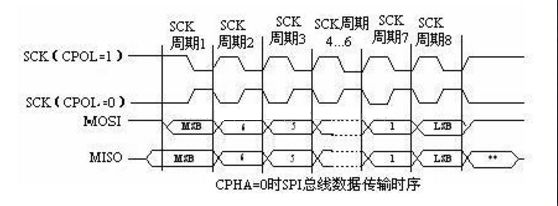

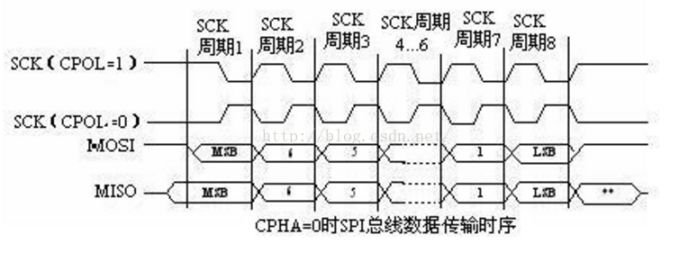

SPI输出串行同步时钟极性和相位可以根据外设工作要求进行配置。

若CPOL = 0,串行同步时钟的空闲状态为低电平;

若CPOL = 1,串行同步时钟的空闲状态为高电平;

时序如下

若CPHA = 0,在串行同步时钟的第一个跳变沿(上升或下降)数据将被采样;

若CPHA = 1,在串行同步时钟的第二个跳变沿(上升或下降)数据将被采样;

时序如下:

SPI主模块与与之通信的外设空闲状态的极性和时钟相位应该一致。

- 相关推荐

- 热点推荐

- S

-

Zeta拓扑电源原理及工作过程解析2023-11-24 7524

-

SPI总线通信例程2023-08-16 754

-

串行通信SPI总线的详解分析2023-05-05 5808

-

西门子的PLC工作过程2022-10-28 1651

-

对SPI通信模式的配置过程分析2022-02-17 1132

-

STM32 PWM工作过程2022-01-06 1756

-

DMA工作过程分析2021-12-16 1246

-

STM32串口通信的工作过程是怎样的?2021-12-06 1335

-

PLC的工作过程及扫描过程2021-02-20 4028

-

SPI总线工作过程及传输方式分析2020-09-09 4498

-

SPI总线及I2C总线工作原理2015-12-08 1452

-

IPOA的工作过程是怎样的?2010-04-07 764

-

用SPI总线实现DSP和MCU之间的高速通信2009-11-27 1035

-

数控机床的工作过程2009-05-06 5217

全部0条评论

快来发表一下你的评论吧 !