SDRAM控制器功能模块概述

描述

本教程重点

存储器简介。

介绍 SDRAM 的工作原理。

详细讲解SDRAM 控制的Verilog 实现方法。

PLL IP和FIFO IP 的调用,计数器设计,按键边沿捕获,数码管控制。

完成SDRAM控制器应用的完整案例。

Signal Tap 调试方法。

准备工作

硬件平台 :DE10-Standard 开发板(DE2-115、DE1-SOC、DE25-Standard、DE10-Lite、DE0-CV、TSP、DE2i-150 开发板也支持)

开发和调试工具:Quartus18.1

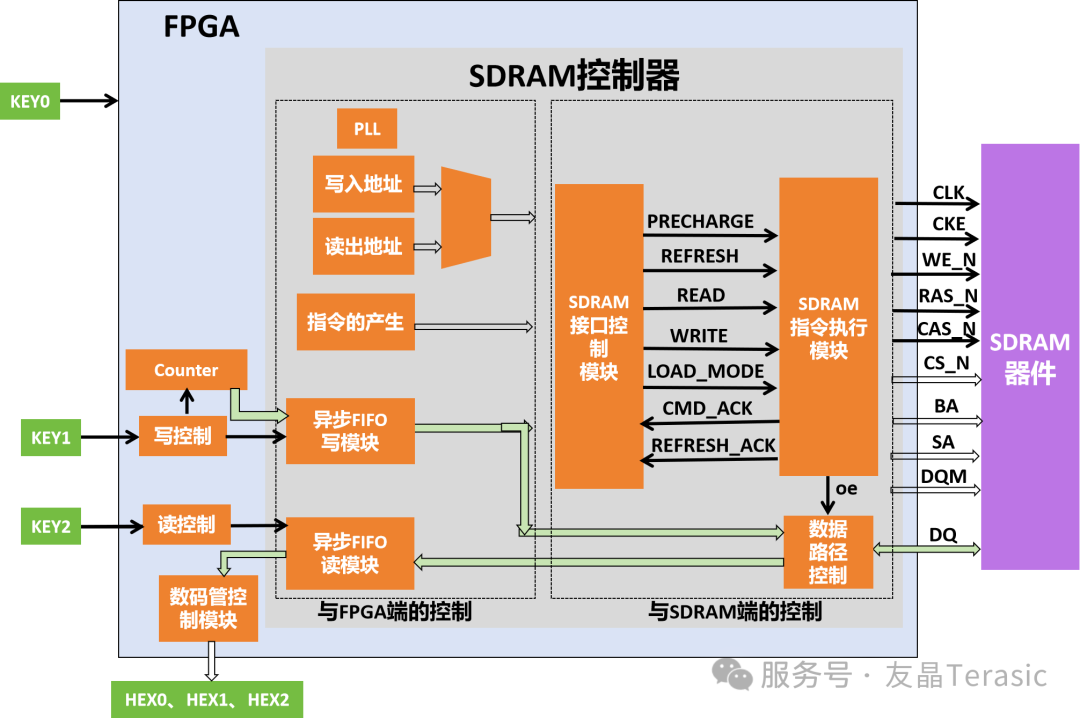

功能模块概述

按键KEY0复位。

按键KEY1触发写,将计数器产生的0到255的数据写到FIFO写模块里面,继而写到SDRAM 器件里面。

按键KEY2触发读,SDRAM的数据先读到FIFO读模块中,然后通过每按一次KEY2从FIFO读模块里面取出一个数据显示到数码管上面。

该实验的功能基本框图如下:

top文件解析:参考08-SDRAM控制器的设计——top文件代码解析 (后续发布)

SDRAM 控制器模块:该模块是本实验的重点,参考

04-SDRAM控制器的设计——control_interface.v代码解析(后续发布)

05-SDRAM控制器的设计——command.v代码解析(后续发布)

06-SDRAM控制器的设计——异步FIFO的调用(后续发布)

07-SDRAM控制器的设计——Sdram_Control.v代码解析(后续发布)

读写控制模块:参考08-SDRAM控制器的设计——按键的处理(边沿捕获电路、硬件消抖、Verilog消抖电路)(后续发布)

七段数码管控制模块:参考之前已有的推文基于FPGA的贪吃蛇游戏设计(二)——数码管驱动模块

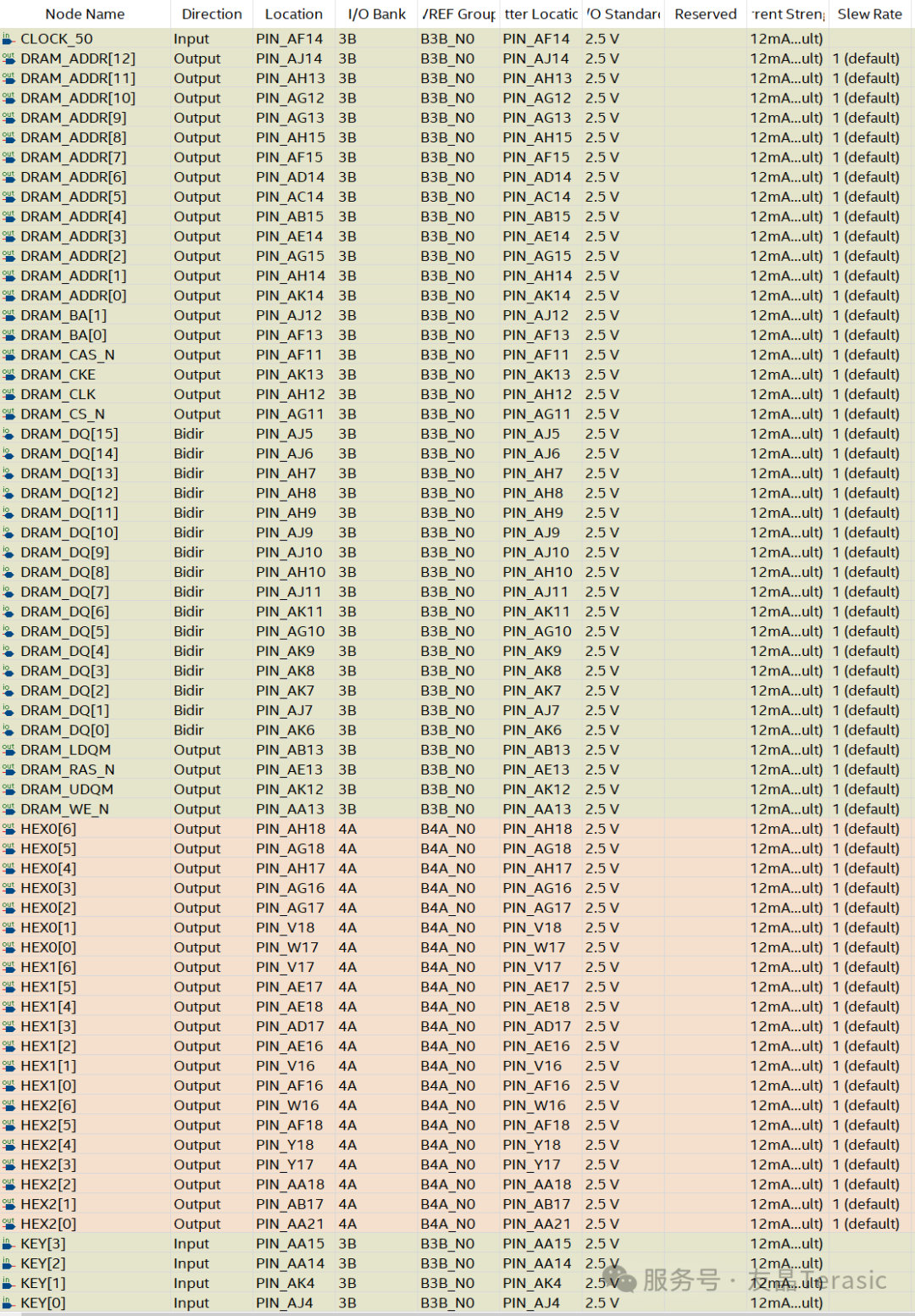

引脚分配

下面给出的是DE10-Standard 开发板对应的引脚分配,若是移植到DE1-SOC或者是DE2-115等其他开发板时,需要修改工程器件和引脚分配。

源码下载

DE10-Standard 工程链接:

https://pan.baidu.com/s/1OVFt5hH862q8BSswYwbOEg

提取码: ms3q

工程源码含详尽的中文注解。

备注

关于SDRAM基础知识请参考

02-SDRAM控制器的设计——SDRAM简介(后续发布)

03-SDRAM控制器的设计——解读IS42R16320D的数据手册(后续发布)

-

SDRAM控制器的设计——Sdram_Control.v代码解析(异步FIFO读写模块、读写SDRAM过程)2025-03-04 2635

-

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文2018-12-25 1737

-

航芯技术分享 | BMS专题之BMS基础功能模块概述2022-02-16 8590

-

【资料】SDRAM功能模块讲解—动态随即存储器HY57V6416202021-04-01 1302

-

基于Stratix III的DDR3 SDRAM控制器设计2010-07-30 852

-

使用Verilog实现基于FPGA的SDRAM控制器2009-06-20 2504

-

SDRAM控制器简易化设计2011-10-24 1197

-

DDR2SDRAM控制器IP功能测试与FPGA验证_陈平2017-01-07 929

-

基于VHDL的SDRAM控制器的实现2017-01-22 1080

-

EPM1240的SDRAM控制器的设计2017-10-31 905

-

SDRAM控制器的设计2017-11-28 1495

-

如何使用FPGA设计SDRAM控制器2020-12-18 1042

-

DDR SDRAM控制器的设计与实现2021-03-28 1222

-

基于SDRAM控制器软核的Verilog设计2021-06-30 3669

-

SSD架构与功能模块详解2024-07-27 3723

全部0条评论

快来发表一下你的评论吧 !