最佳数字主动降噪耳机设计要点

电子说

描述

前馈降噪

前馈降噪系统,由耳机输出与环境噪声频响相同但相位相反的信号来实现降噪。如图1,前馈麦克风侦测噪声并透过滤波电路产生反相信号,在耳鼓处反相信号与噪声信号抵消,从而降低人耳听到的噪声水平。这里的滤波电路主要用来补偿耳鼓和麦克风处检测到的噪声之间的差异,另外对喇叭本身对消噪信号的响应能力也有补偿作用。

图1:前馈降噪耳机

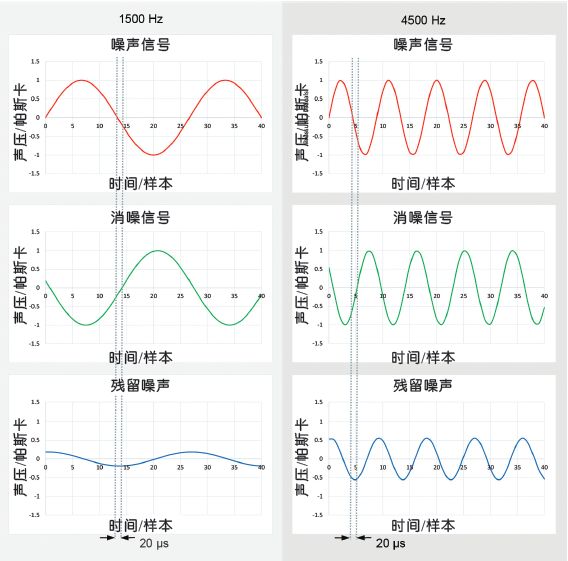

图2:两种不同频率下系统延迟的影响

前馈降噪带宽,在低频处被耳机驱动模块限制在50Hz左右,在高频处被声学结构和信号处理延迟限制3kHz。延迟会导致难以在消噪信号和噪声信号之间实现180度的相位反转,高频部分因为波长较短更难处理。图2显示了两种频率下20μs延迟对降噪效果的影响:频率为1500Hz时,残余噪声约剩1/5(14dB ANC),但频率为4500Hz时,即使延迟不变,残余噪声也已增加到3/5(仅4dB ANC)。

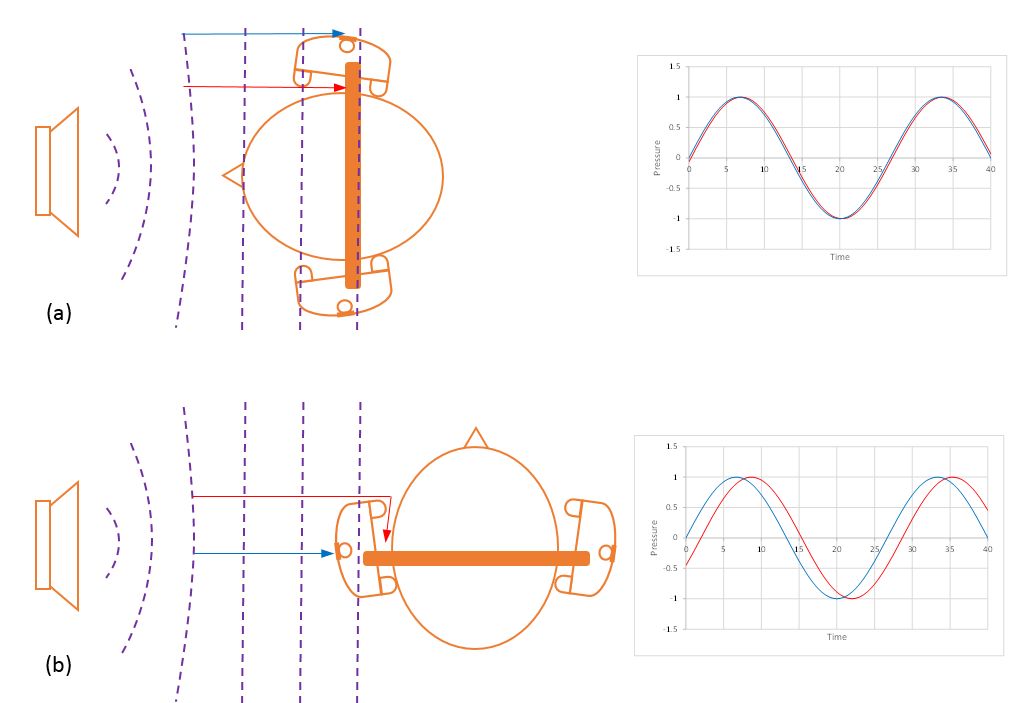

实际可以尽量提前检测环境噪声来补偿该延迟,这便于处理器有更多时间处理并输出消噪信号,另外,将降噪麦克风放置于远离耳道的入口也有利于扩大降噪的角度(图3)。

图3:前馈降噪的方向性,(a) 0度时朝向的噪声(b) 90度时朝向的噪声

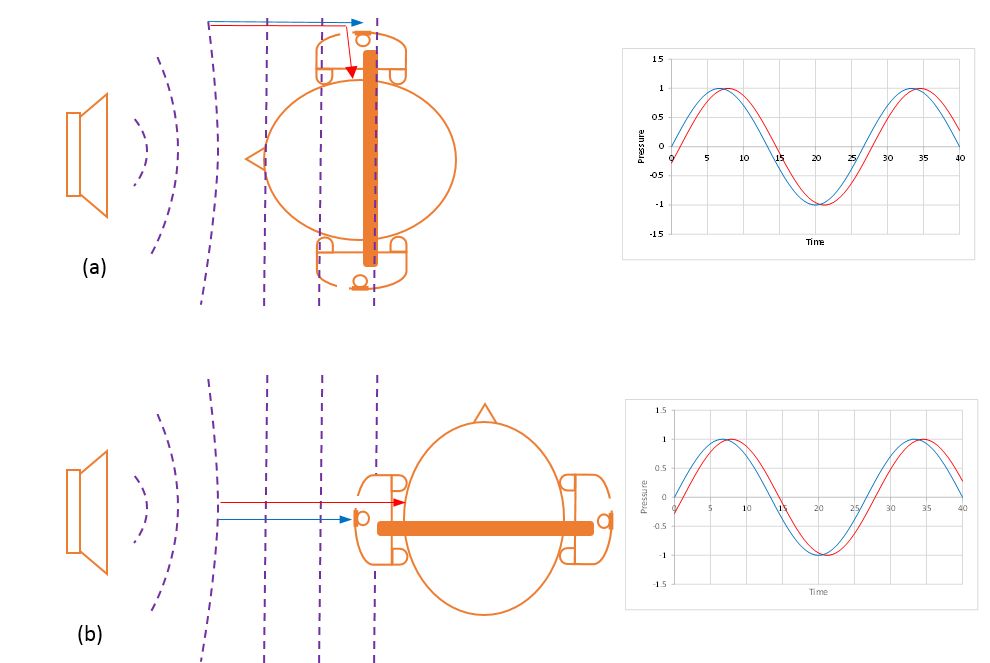

如图3,如果将麦克风放置在耳机壳外(即远离耳朵),当麦克风拾音孔与噪声的角度分别成0°和90°时,噪声进入麦克风以及人耳的时间差不同,这也意味着降噪效果会有方向性。控制环境噪声进入耳朵的路径并在靠近该路径放置麦克风则可解决此问题:如图4,一种有效的设计是在扬声器后方开泄露孔,噪声主要从该泄露孔,以及耳机驱动单元进入人耳,从而可以保证不同角度的噪声进入麦克风和人耳的时间差基本是一致的,进而保证降噪效果的一致性。

图4:靠近噪声进入耳朵的位置放置话筒(a) 0度朝向的噪声(b) 90度朝向的噪声

噪声频率高于3kHz时,声音的波长明显短于耳道和耳机腔体尺寸,在声腔以及扬声器振膜之间可能产生共振进而难以进行滤波设计,而且该带宽中的降噪也受限于系统延迟,因此主要靠被动降噪。被动降噪一般随着耳机气密性的提高而提高,比如填补或者缩小泄露孔尺寸,但同时也会降低前馈降噪在高频处的性能。因此,需要权衡该频段范围内的被动降噪和主动降噪的取舍。

有趣的是,消费者发现评估ANC效果更容易一些,因为可以通过快速开启或关闭ANC形成反差得到结果,但评估被动降噪效果就困难了,因为用户戴上耳机后在很短时间内就会忘记环境噪声的水平从而难以形成对比。

图4还可以看出,耳机在设计中还需要保证耳垫和头部之间密封的稳定性,以便用户可以得到稳定的声学特性和降噪性能。

此外,建议耳机喇叭的频率响应和被动衰减曲线要平滑(例如Q值不会太高或者太低),以便简单的数字滤波器就可以对传递函数进行补偿。

反馈降噪

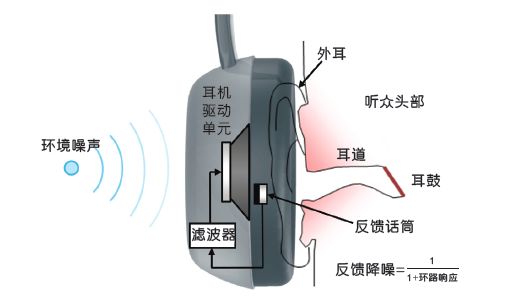

反馈降噪耳机(图5)的工作原理主要是检测耳鼓区域的噪声,然后形成一个基本的反馈回路来最大限度降低该区域的噪声水平。

图5:反馈降噪耳机

图5是反馈降噪系统设计的公式。整个“环路”是由喇叭以及麦克风的响应,以及滤波器的组成。公式表明,随着滤波器增益(及其环路增益)增大,噪声残留变小,从而降噪性能得到提升。但如果环路的相位接近±180°,“环路”信号会发生反转,分母上的“+”将变为“-”。在这种情况下,环路增益大小调节受限,因为当它从0.0增至1.0时,结果是放大,当等于1.0时,结果是“除以零”,这意味着不稳定并且经常随着频响幅度增加引起啸叫——务必要避免。

实际上,环路的相位在频率为10 Hz时趋向于180度,在频率为几kHz时趋向于 -180度。因此,在这些频率下的增益必须要尽可能大但要低于1.0。通常滤波器会将反馈降噪的带宽限制在10Hz到1kHz之间,降噪效果也可以从滤波器得出。

环路中高频部分的相位变化是由处理器中的系统延迟、扬声器以及喇叭到麦克风的距离等因素决定的。因此,减少其中任何一个因素(使用轻重量高灵敏度的喇叭;将麦克风靠近喇叭振膜放置;尽量减少处理器延迟时间)均可以提高降噪带宽上限。

由于反馈麦克风靠近喇叭放置,因此耳机播放的音乐也会被误认为噪声。结果就是,来自喇叭的音乐信号也被降噪处理,因此还需要通过电路来进行补偿。

数字信号处理

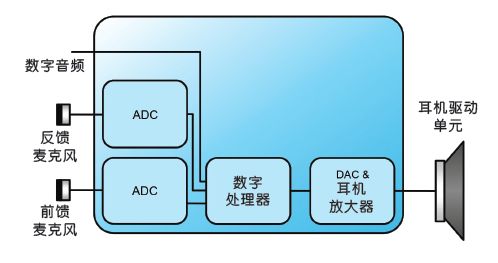

环境降噪数字系统的构建模块简单如图6。

图6:数字降噪IC的基本框图

将ANC滤波器运行在数字处理器中有多种好处:

灵活–针对不同的环境能够切换滤波器做到自适应,或者将周围环境的声音直接送入耳机(类似于助听器),也可以与蓝牙通信设备等进行数字接口通信。

开发速度更快–ANC滤波器的设计通常随着声学的调整而需要修改外围滤波电路,数字方案则可以在芯片内部快速调整滤波电路并立即投入验证。

优化了校准流程–因为声学器件的公差会影响滤波器形状。因此在生产中,声学传递函数可能存在差异,从而需要对耳机校准。校准过程需要人工手动完成并且占用大量时间,数字降噪技术可以省掉这部分资源的支出。

尺寸更小-因为芯片周边器件较少。

数字ANC的缺点如下:

功耗更高

数字系统的延迟更高 。通常延迟越低越好,20μs在整个回路延迟所占比例很小,所

以很难明显区分出可忽略延迟的模拟系统与延迟小于20μs的数字系统之间的差异。

随着无线“耳穿戴”设备越来越流行,功耗问题变得至关重要。因此,任何数字降噪解决方案都必须高效节能,尤其是其中的ADC和DAC模块部分。只运行必要的程序(例如,使用结构简单的滤波器并优化任何其它进程)并尽可能降低时钟频率,即可将数字处理器功耗保持在最低水平。加快时钟频率虽然可以显著减少处理器延迟时间,但也会增加功耗,因此需要权衡二者的关系。

电子噪声

降噪耳机的电子噪声对降噪会带来副作用。电子噪声的主要来源通常是麦克风。尽管硅麦(MEMS)最近越来越流行,但驻极体麦克风(ECM)在信噪比方面仍然优于MEMS。一般业界领先的ECM麦克风信噪比为74 dB(测试条件为94dBSPL@1KHz),也就是底噪为20dBSPL。尽管麦克风的底噪不高,但仍然建议尽可能选用高SNR的麦克风,从而避免在安静的环境中听到不期望的噪声。

如果使用数字降噪耳机聆听音乐时关闭ANC,麦克风的噪声会被系统屏蔽在外,那么整个数字系统也必须具有足够低的噪声才能确保用户欣赏到纯净的音乐。

数字系统中SNR的计算方法一般是拿最大不失真输出信号减去可辨别的最小输出信号,系统中不允许听到任何噪声。人耳听到1KHz主频的阈值下限被定义为0dBSPL,但您可能发现自己不太可能处于比25dBSPL(差不多1米处呼吸声被人耳听到的程度)还安静的环境中。尽管近期的标准(EN 50322和IEC 600065:2014)规定便携式媒体播放器最大播放音量需要限制在100dBA,但在某些频率下,耳机可输出的信号峰值可以达到约125dBSPL。

因此,DAC的规格需要定义在至少支持100dB信噪比(125dBSPL–25dBSPL)才是合理的 ,并确保数字域信噪比足够优秀。这对于现阶段的数字处理器来说不难完成,所以一般使用定点算法而不用功耗比较高的浮点算法,另外还要保证字节长度,确保量化噪声的水平低于ADC和DAC的噪声。

另外,还需要选择灵敏度好、失真度低的扬声器。扬声器的失真会导致生成的消噪信号失真从而降低降噪水平。

设计要点概述

弹性的数字降噪架构设计。

最大程度降低整个系统的声学延迟,使用低于20μs延时的芯片以保证降噪带宽。

为噪声进入人耳搭建一个可控的路径渠道,保证前馈降噪效果。

耳机的结构设计能满足所有用户佩戴均具有一致性

选择被动降噪差的大尺寸泄露孔设计搭配较强的主动降噪设计,或选择被动降噪好的小尺寸泄露孔设计搭配稍弱的主动降噪设计。

调节声腔容量、泄露孔和通气孔阻尼直到获得平滑的耳机和被动衰减响应。

尽量减少电子噪声的来源,选择高SNR的麦克风,保证人耳听不到数字和DAC部分的噪声。

-

llsluoluo33

2018-08-12

0 回复 举报我是主动降噪芯片中国原厂的,可提供降噪方案和降噪芯片,协助解决技术难点,电话和微信18503002452 qq 2208962322 收起回复

llsluoluo33

2018-08-12

0 回复 举报我是主动降噪芯片中国原厂的,可提供降噪方案和降噪芯片,协助解决技术难点,电话和微信18503002452 qq 2208962322 收起回复

-

主动降噪、高保真蓝牙耳机解决方案2018-09-07 3862

-

主动降噪蓝牙耳机怎么选?时下比较火爆的五款耳机产品2020-04-15 2965

-

设计反馈式主动降噪耳机有哪些必需的步骤?2021-06-01 1890

-

怎样去设计一款基于AS3415降噪芯片的主动降噪前馈耳机?2021-07-26 3051

-

降噪耳机设计2022-10-19 6648

-

主动降噪和被动降噪耳机的区别2017-11-09 75953

-

国产降噪蓝牙耳机推荐 高性能主动降噪耳机品牌推荐2020-05-06 6849

-

国产降噪耳机那个牌子好 实用的主动降噪耳机推荐2020-05-08 3409

-

入耳蓝牙主动降噪耳机2020-05-09 3224

-

主动降噪蓝牙耳机有哪些?哪个主动降噪耳机效果更好?2020-05-10 5499

-

有什么主动降噪耳机推荐?618降噪耳机选购指南2020-06-11 2967

-

2020有哪些降噪耳机推荐?主动降噪耳机性价比排行2020-08-25 5160

-

口碑最好的主动降噪耳机,真无线降噪耳机品牌推荐2020-09-01 5547

-

主动降噪耳机的设计要点详细说明2020-12-20 5418

-

降噪耳机是怎么降噪的?被动降噪和主动降噪的区别和原理2023-12-11 6957

全部0条评论

快来发表一下你的评论吧 !