2.5D集成电路的Chiplet布局设计

描述

以下文章来源于逍遥设计自动化,作者逍遥科技

引言

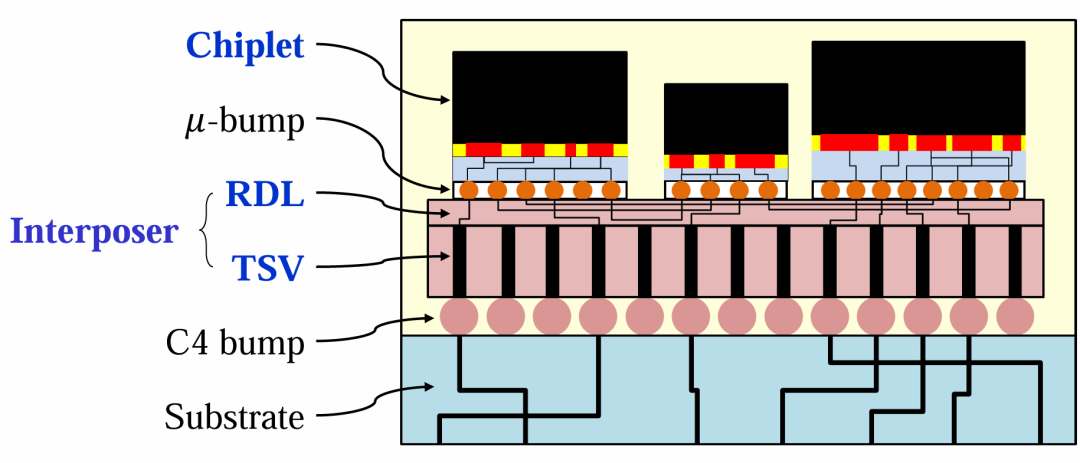

随着摩尔定律接近物理极限,半导体产业正在向2.5D和3D集成电路等新型技术方向发展。在2.5D集成技术中,多个Chiplet通过微凸点、硅通孔和重布线层放置在中介层上。这种架构在异构集成方面具有优势,但同时在Chiplet布局优化和温度管理方面带来了挑战[1]。

图1:2.5D集成电路的分层架构和各种互连组件。

1布局优化框架

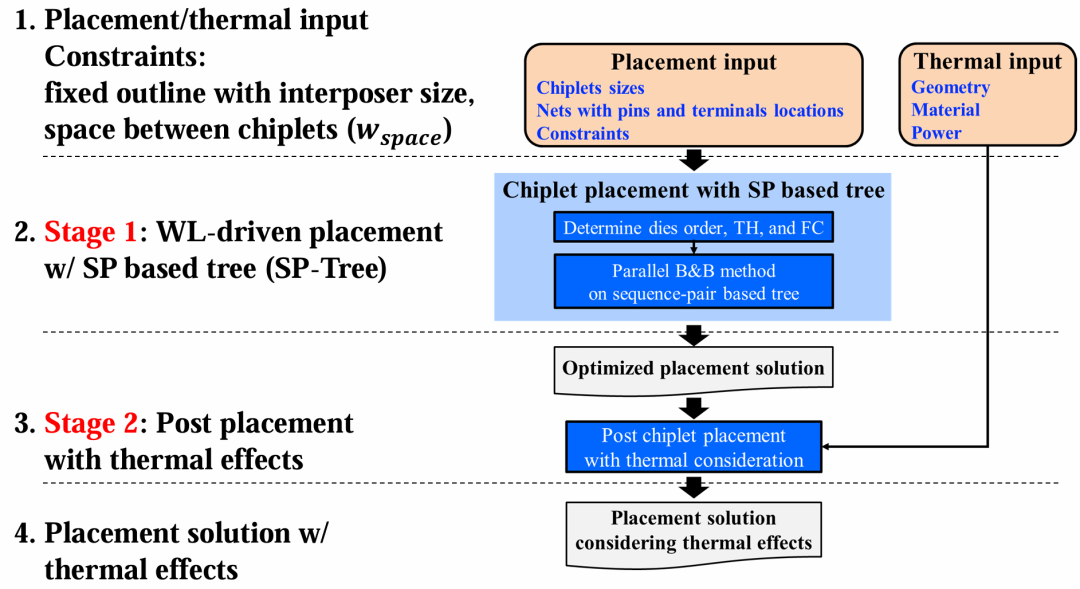

该框架分为两个主要阶段:第一阶段使用基于序列对的树结构(SP-Tree)进行布线长度优化布局;第二阶段进行考虑温度效应的后布局优化。系统首先处理输入约束条件,包括中介层尺寸的固定轮廓要求和Chiplet之间的必要间距。这些约束条件构成了后续优化决策的基础。

图2:从输入约束到最终解决方案的完整处理流程。

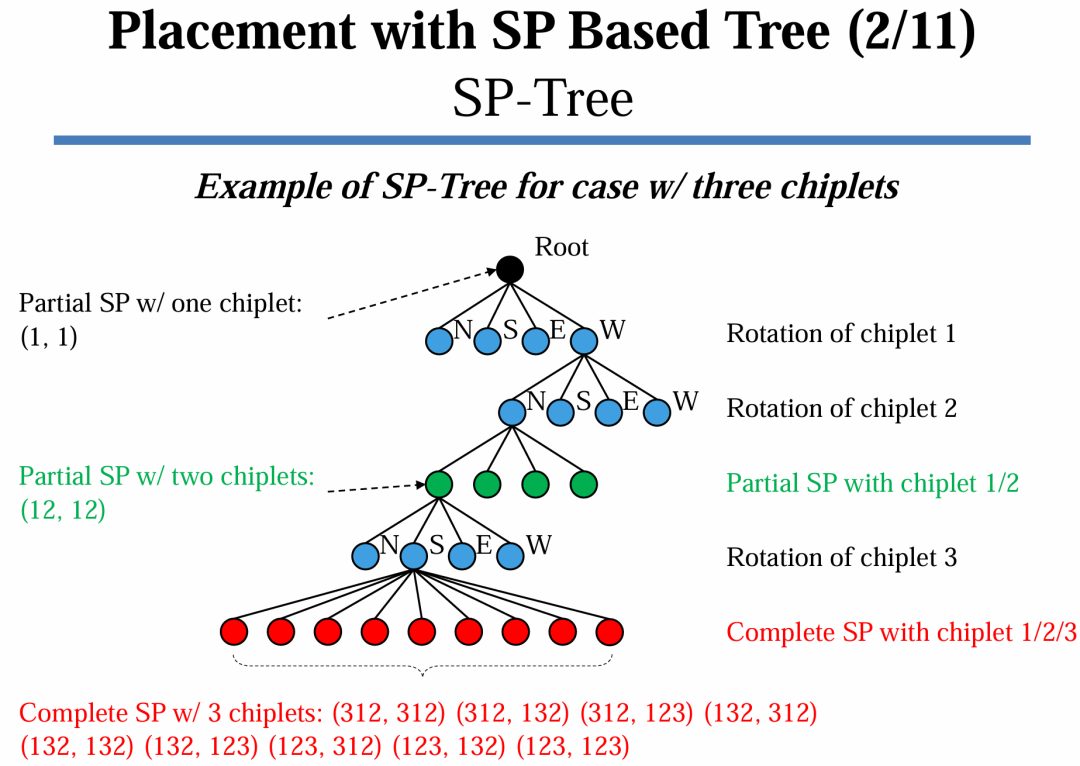

2基于SP-Tree的布局方法

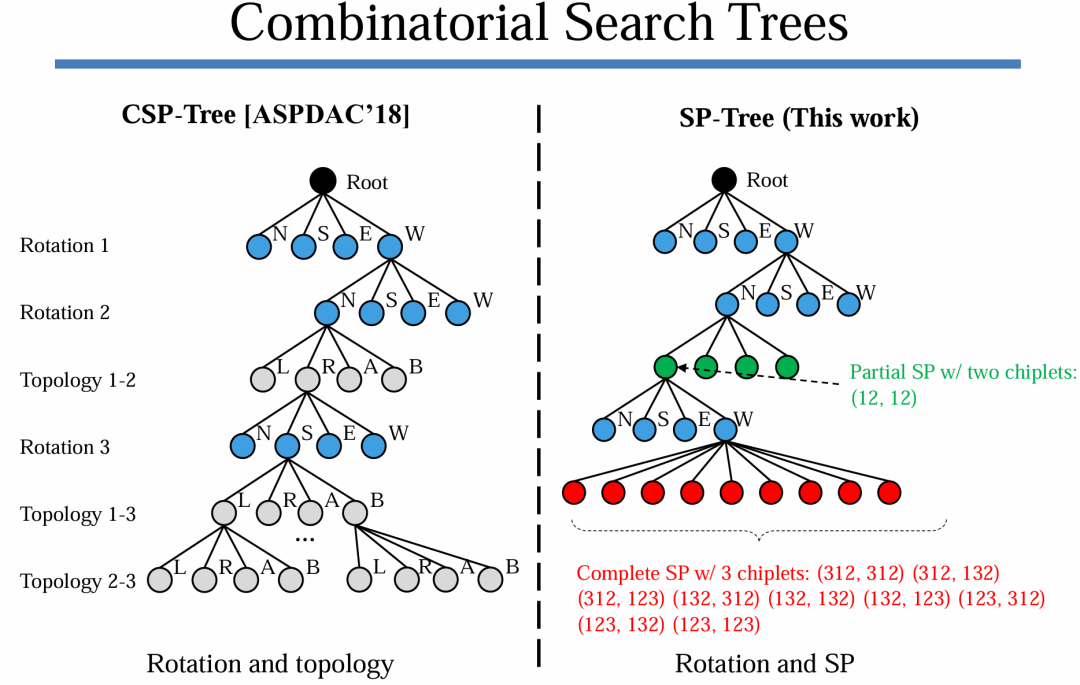

SP-Tree方法相比之前的CSP-Tree方法有显著改进。其主要优势在于能够高效表示和处理布局方案,同时消除冗余或无效配置。该方法确保生成的所有布局方案都能在物理上实现。

布局过程采用复杂的并行分支定界(B&B)方法。从树的根节点开始,通过深度优先搜索系统地探索潜在解决方案。在此过程中,算法分配旋转节点指定方向(北、南、东、西),并确定Chiplet排列的部分或完整序列对。

图3:比较SP-Tree和CSP-Tree结构,展示SP-Tree方法更高效的组织方式。

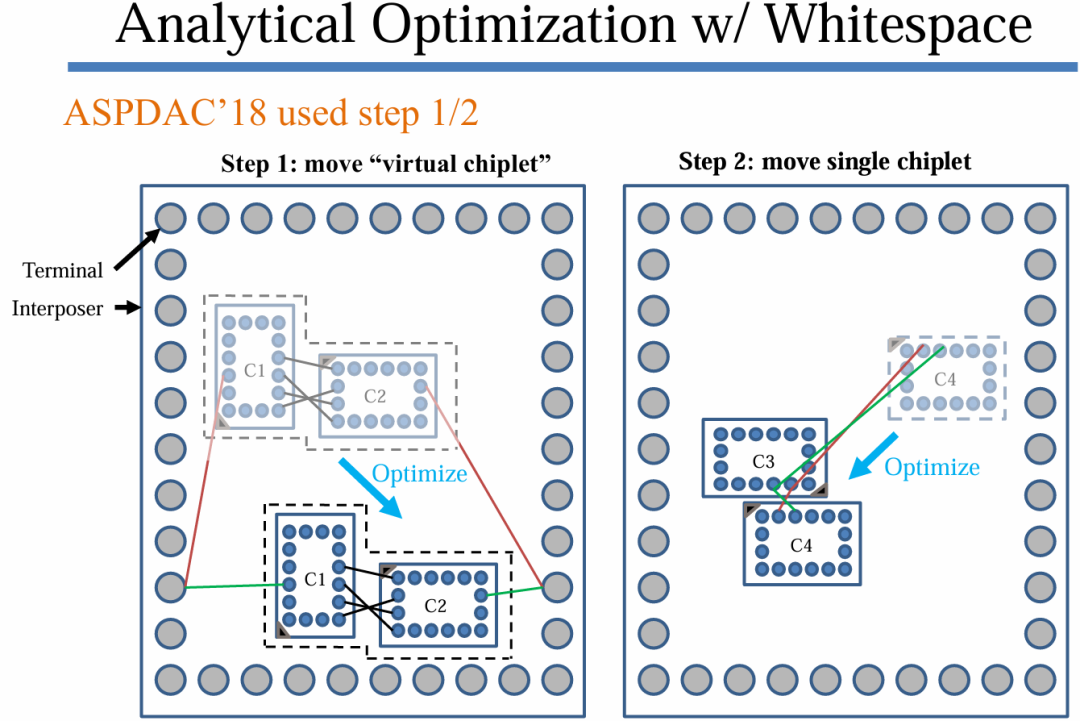

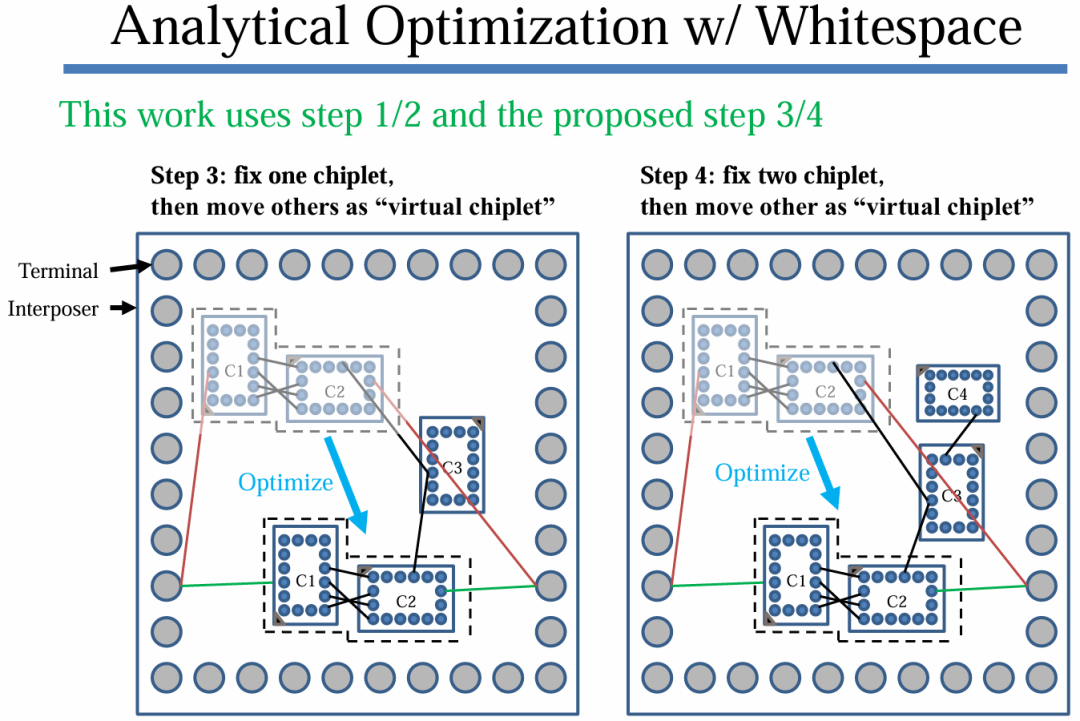

3考虑空白区域的分析优化

空白区域优化过程包含四个步骤:

1. 首先,系统处理虚拟Chiplet移动,允许在不考虑物理约束的情况下进行初步位置优化。

2. 其次是单个Chiplet优化,调整各个组件以获得最佳位置。

3. 第三步引入了固定和自由Chiplet移动策略,某些Chiplet保持静止而其他可以重新定位。

4. 最后,系统执行多Chiplet组优化,同时考虑多个组件的集体移动。这种分层方法确保了解空间的充分探索。

图4:顺序优化步骤展示不同的Chiplet移动和空白区域利用方法。

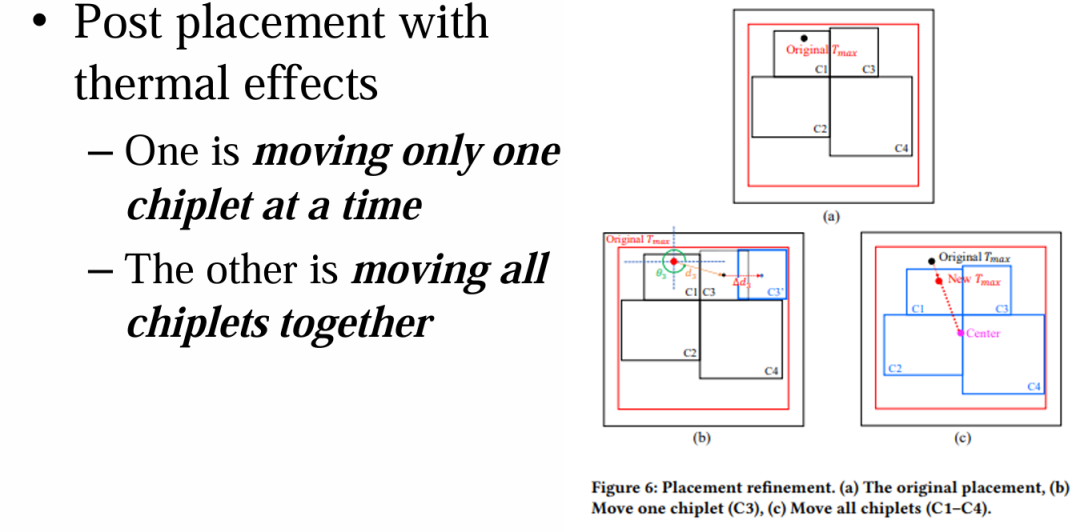

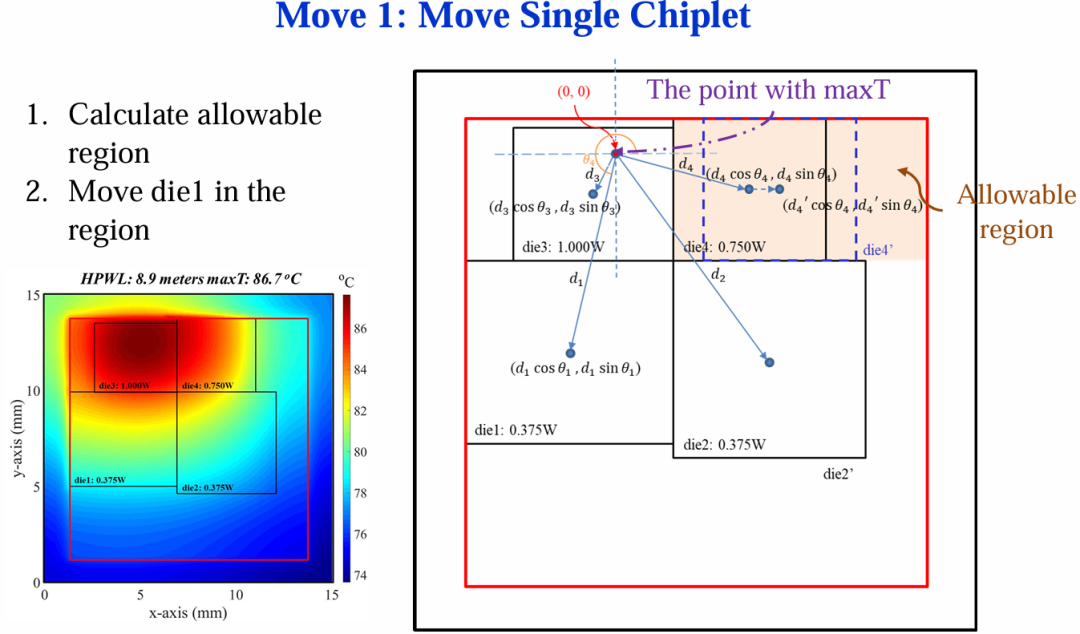

4后布局温度效应考虑

温度优化阶段采用精密的温度管理方法。系统使用64×64×5网格进行热仿真,提供整个设计的精确温度分布建模。温度计算使用SuperLU 5.3.0矩阵求解器,确保高效和准确的热分析。

优化过程实施两种不同的移动策略:第一种策略专注于在计算的允许区域内进行单个Chiplet移动,第二种策略考虑整个Chiplet组的协调移动。这些互补方法能够解决局部热点和整体温度分布模式。

图5:展示单个Chiplet和整体布局组移动策略的热优化方法。

5实验结果

使用C/C++在配备Intel Xeon处理器的Linux工作站上进行实现测试。结果显示在性能指标和处理效率方面都有显著提升。在布线长度优化方面,系统相比现有方法实现了高达1.035%的总布线长度改进,同时处理速度提高了156倍。

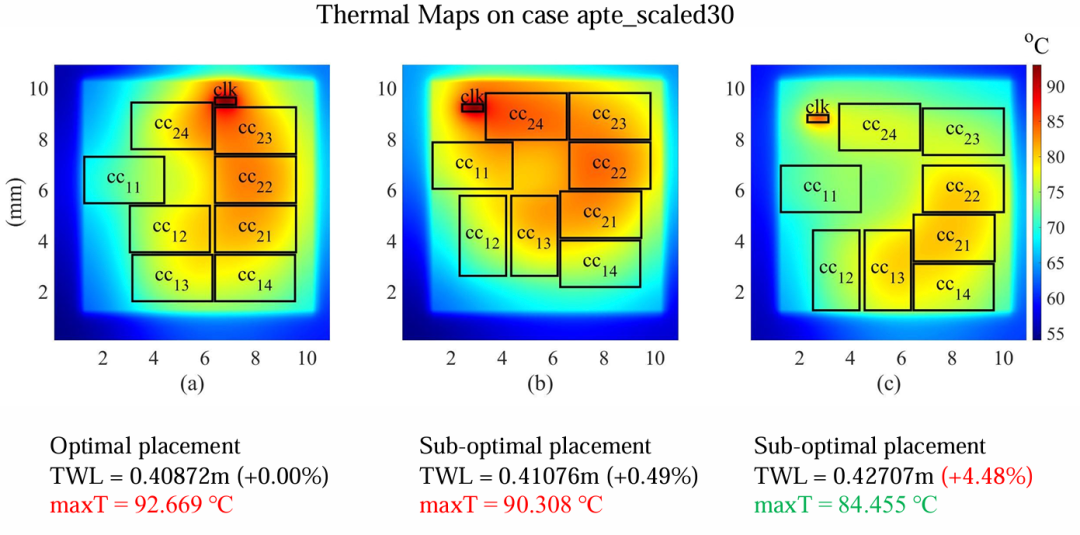

温度性能结果同样显著,在保持合理布线长度指标的同时,实现了高达8.214°C的温度降低。在大多数测试案例中,系统成功满足了85°C的温度约束,仅需要5.376%的平均布线长度增加即可实现温度合规。

图6:温度分布图展示不同布局配置下的温度改进情况。

6结论

基于SP-Tree的布局方法结合温度考虑,代表了2.5D集成电路设计方法的重要进展。该框架成功结合了高效的组合搜索技术和实用的温度管理策略,形成了理论完善且实用的解决方案。

该系统在处理约十个或更少Chiplet的设计时表现特别出色,这与当前工业需求高度吻合。通过有效平衡布线长度优化和温度约束,该框架为现代2.5D集成电路实现提供了全面的解决方案

关于我们:

深圳逍遥科技有限公司是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 1479

-

新型2.5D和3D封装技术的挑战2020-06-16 8773

-

异构集成基础:基于工业的2.5D/3D寻径和协同设计方法2021-07-05 1177

-

浅谈2.5D组态的应用案例2022-06-06 2703

-

3D封装与2.5D封装比较2023-04-03 5733

-

2.5D封装应力翘曲设计过程2023-09-07 5079

-

Chiplet主流封装技术都有哪些?2023-09-28 3249

-

奇异摩尔与智原科技联合发布 2.5D/3DIC整体解决方案2023-11-12 2209

-

2.5D和3D封装的差异和应用2024-01-07 5259

-

探秘2.5D与3D封装技术:未来电子系统的新篇章!2024-02-01 5675

-

2.5D/3D封装技术升级,拉高AI芯片性能天花板2024-07-11 9780

-

技术资讯 | 2.5D 与 3D 封装2024-12-07 3223

-

2.5D和3D封装技术介绍2025-01-14 3598

-

多芯粒2.5D/3D集成技术研究现状2025-06-16 2118

-

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm2025-08-07 4937

全部0条评论

快来发表一下你的评论吧 !