灵活性和高集成度于一身,教你ADC驱动器配置

电子说

描述

如何使用集灵活性和高集成度于一身的全能ADC—— μModule数据采集系统ADAQ798x系列呢?ADI工程师为此撰写了6篇博客,目的是帮助系统您充分利用ADAQ798x系列的灵活前端,并说明它可以如何配置以适应不同应用。

之前我们分享了该系列博客前两篇,主要介绍了两个问题

-

如何与小于ADC输入范围的单极性输入源接口?

-

为何要配置ADC驱动器?

点击可查看→ 全能ADC,你应该这样用(连载 上)即可查看。

今天,我们来看看该系列博客的第三篇和第四篇——同相求和配置以及支持衰减的同相求和配置。

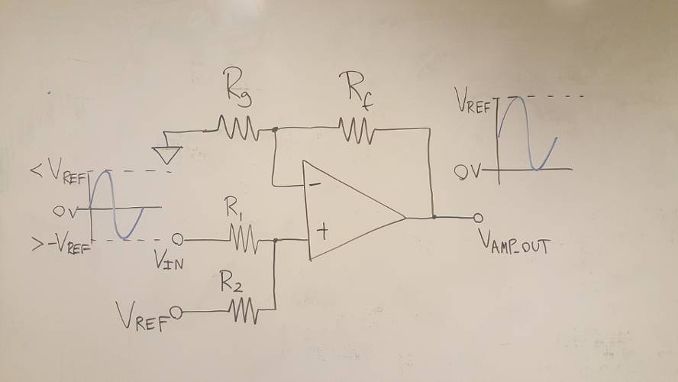

同相求和配置

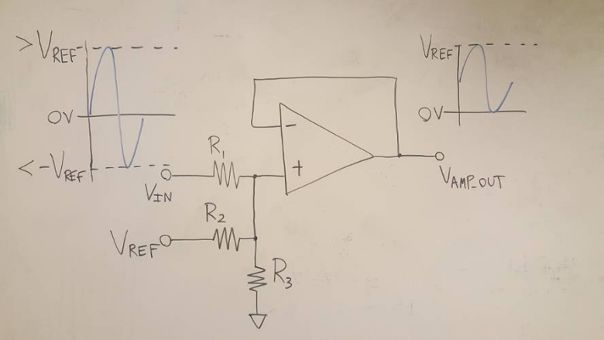

双极性信号在低电压(0 V)上下摆动。由于 ADAQ798x 集成 ADC 只能转换0 V 到 VREF 的信号,所以针对该 ADC,需要将双极性信号加以直流偏置和适当调整。为了完成这一任务,以下配置给标准同相配置增加了两个电阻(R1和R2)。

此配置将输入信号与一个单独的直流电压求和,以将ADC驱动器输出偏置到ADC中间电平输入(VREF/2),从而实现双极性到单极性的转换。基准电压(VREF)用作直流电压常常是可行的,这样就无需其他电路(反正ADAQ798x总是伴随一个基准电压源!)。它还能防止VREF偏差给系统增加失调误差,因为ADC驱动器的直流偏置总是VREF的一半。鉴于这些原因,我们将专门讨论这种将VREF用作直流“变换”电压的配置。

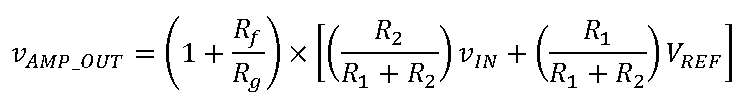

此配置的传递函数如下:

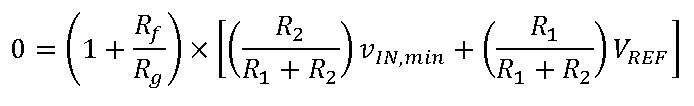

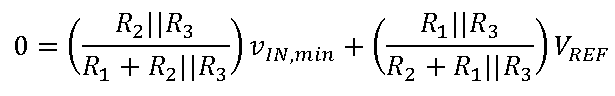

与普通同相配置类似,Rf和Rg之比决定从IN+到AMP_OUT的增益,但此比值现在也依赖于vIN的输入幅度。注意vIN为双极性,但同相节点上的电压为单极性。这意味着,对应于vIN的最小值,IN+上的电压必须为0 V:

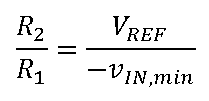

由此关系可得出R1和R2之比:

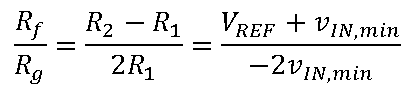

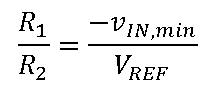

Rf和Rg可利用该配置的传递函数以及vIN为0 V时ADC驱动器输出(vAMP_OUT)等于VREF/2的条件来确定。求解Rf和Rg的方程可得:

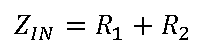

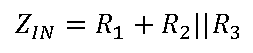

现在有了R1和R2之比及Rf和Rg之比,但我们还需要挑选特定的值。我们已在该系列博客《增加单极性输入的增益》中讨论了Rf和Rg值的选择。R1和R2的选择应基于应用的噪声、精度和输入阻抗要求确定。小电阻会改善噪声,可降低其与ADC驱动器输入偏置电流相互作用所引起的失调误差,但若要提高输入阻抗并降低基准源的输出电流,则需要大电阻。此电路的输入阻抗为:

注意,对于vIN幅度为±VREF的特殊情况,Rf和Rg之比为0。这种情况下,ADC驱动器增益为1,意味着省去Rg,Rf可以为0 Ω。

举例说明ADAQ7980需要对±1 V输入信号执行双极性到单极性转换,VREF = 5 V,使用Rf = 2 kΩ。利用上述公式,R2须为R1的5倍,Rf须为Rg的2倍。Rf为2 kΩ,所以Rg须为1 kΩ。R1和R2的具体值可根据应用要求选择。对于本例,我们希望选择R1和R2的组合来抵消输入偏置电流对失调误差的影响。技术文章《运算放大器输入偏置电流》中已经阐明,为实现此目的,R1||R2应等于Rf||Rg,故R1 = 800 Ω,R2 = 4 kΩ。

我们再考虑一个例子:vIN = ±10 V,VREF = 5 V。这种情况下,我们会遇到Rf和Rg之比为负数的问题,所以利用这种配置实际上不能实现该输入范围。事实上,适合此配置的最大vIN为±VREF,此时ADC驱动器增益等于1。幸运的是,我们会在本系列接下来的文章中讨论其他两种允许我们超出此输入范围的配置。

若将R2接地而不是接VREF,则以上配置也可用于单极性信号。这一修改对需要衰减以用于ADC的单极性输入信号(幅度大于VREF)有用。这种情况下,ADC驱动器极有可能是单位增益,故不需要Rf和Rg。

如上所述,如果应用要求高输入阻抗,则R1和R2必须很大,这可能会提高系统的本底噪声。我们可以通过增加分流电容和/或通过过采样和抽取来补偿噪声增加。两种方案均通过损失输入信号带宽来降低本底噪声。但是,对于低带宽或直流应用,输入带宽不那么重要。因此,这些配置更适合低带宽、高输入阻抗应用。我们将在下一篇文章中更详细讨论这个话题。

然而,有一个问题未涉及,那就是ADC驱动器流过电阻的输入偏置电流所引起的失调误差。电阻越大,引起的直流误差越大。通过调整R1和R2之比以补偿不需要的压降,或通过选择Rf和Rg的值来抵消R1和R2引起的失调,可以降低此误差,不过输入范围会有损失。但应注意,Rf 必须足够小以确保放大器稳定,故第二种方案并不总是可行。

支持衰减的同相求和配置

针对大于±VREF的信号,可采用以下配置来执行带衰减的双极性到单极性转换。

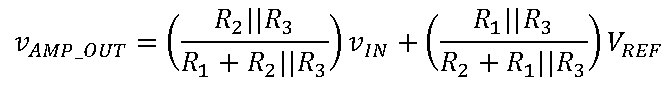

此配置与上文的【同相求和配置】讨论的配置相似,区别在于不再需要Rf和Rg,但增加了R3以提供额外的信号衰减。此配置的传递函数如下:

这次求得R1、R2和R3之比的数学计算较为复杂,但我们可以使用同之前配置相似的方法。求出电阻之比后,便可根据应用需求选择具体的值。为了简洁起见,这里不叙述推导的每一步,但我们会看到,对于vIN的最小值和最大值,传递函数的简化使我们能得出电阻比。

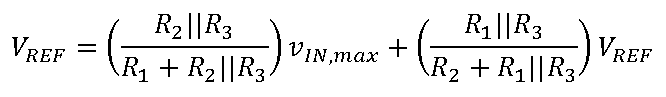

R1和R2之比是利用该配置的传递函数并代入vIN最小值(使得vAMP_OUT等于0 V)而得出:

R3不出现在公式中,求解R1和R2得到:

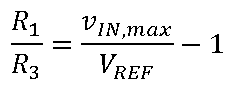

R1和R3之比是代入vIN最大值(使得vAMP_OUT等于VREF)而得出:

这一次,R2不出现,求解R1和R3得到:

此时,我们可以选择其中任一电阻的值(考虑VREF和vIN范围),然后计算另两个电阻的值。像以前一样,主要权衡因素是输入阻抗与系统噪声和失调误差。此电路的输入阻抗(ZIN)为:

再次考虑该上文【同相求和配置】部分的例子,其中vIN = ±10 V,VREF = 5 V,用1 MΩ的输入阻抗设计该配置。对于vIN和VREF的这种组合,R1须为R2的2倍,且等于R3。将R2和R3与R1的比值用于输入阻抗公式,得到R1 = 750 kΩ。因此,R2和R3分别为375 kΩ和750 kΩ。

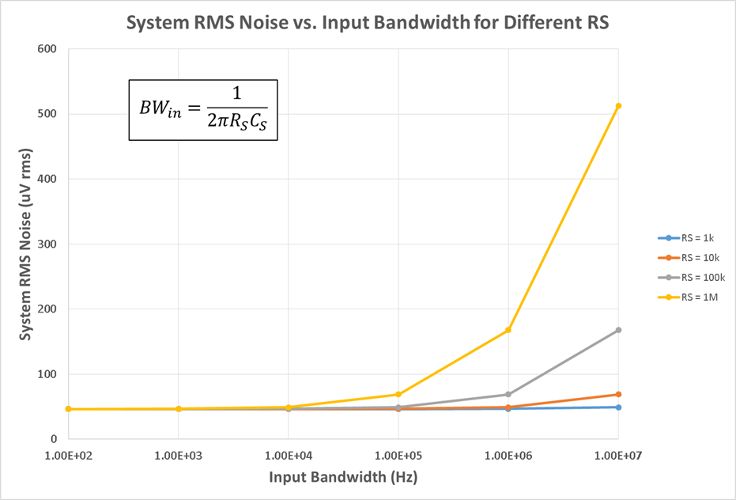

正如上文【同相求和配置】所述,需要权衡输入阻抗与系统噪声性能。实现高输入阻抗需要大电阻,而后者会产生更多热噪声,并与ADC驱动器的输入电流噪声相互作用,产生更多输入电压噪声。二者均会提高ADC输入端的有效均方根电压噪声,导致性能大幅降低。在上例中,系统总噪声约为334 μV rms(使用5 V基准源时,动态范围降低整整15.5 dB,从92 dB降至74.5 dB)!

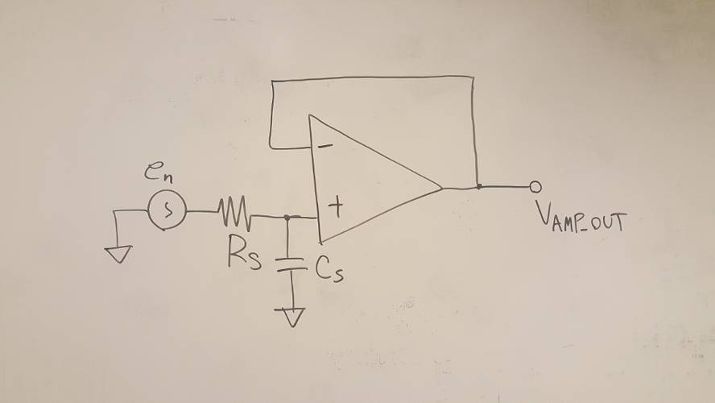

但还有希望!如果限制输入带宽,这种配置实际上可以实现接近最优的性能。例如,若将上例中的输入带宽限制为20 kHz,则全系统噪声几乎降低10倍,达到48 μV rms(对于VREF = 5 V,动态范围为91.4 dB)!我们可以通过增加分流电容CS来限制输入带宽(BWin),如下图所示。注意,对于这些噪声计算,我们可以将R1、R2和R3看作单个电阻RS,其中RS为R1、R2和R3的并联组合。

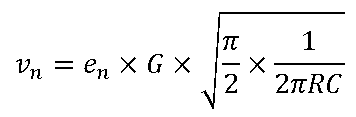

技术指南《单极点系统的运算放大器总输出噪声计算》说明了如何计算RS产生的噪声(包括热噪声及其与ADC驱动器输入电流的相互作用)。ADAQ798x 的主要区别在于噪声带宽是由集成RC滤波器设置,而不是指南中的放大器带宽。RS给ADC输入端增加的有效值噪声为:

(en为RS的约翰逊噪声,G为ADC驱动器增益。)

CS通过降低ADC驱动器的输入带宽来减小到达ADC的噪声。如果RS和CS的截止频率远小于集成RC滤波器的截止频率(4.42 MHz),则RS的噪声贡献可以利用RS和CS计算,代替上式中的R和C。

系统总噪声为ADAQ798x中各噪声源的和方根,包括RS的噪声、ADC驱动器的输入电压噪声和ADC的有效值噪声。下图显示了多个RS值对应的系统噪声与输入带宽的关系。

注意随着输入带宽降低,全系统噪声趋向于ADAQ798x的总有效值噪声(44.4 μV rms)。这意味着降低带宽所获得的减噪收益会在某一频率递减,该频率取决于RS有效值。

本部分讨论了一种允许 ADAQ798x 接受大于±VREF的双极性输入的ADC驱动器配置,并说明了如何基于电阻值(以及可选的分流电容CS)计算输入阻抗和系统噪声。

虽然已证明增加CS可降低噪声,但它也会限制可用输入带宽。因此,将此配置用于宽带宽应用时,要实现高输入阻抗常常是不切实际的。此配置仅推荐用于需要高输入阻抗的低带宽应用。

-

如何使用集灵活性和高集成度于一身的全能ADC2018-03-02 8338

-

SiLM27519AD-7G 20V, 4A/5A 灵活双输入,高速强驱的低边门极驱动器2025-07-26 972

-

寻求高集成度电池驱动方案?剖析SiLM2661CA-DG的独立双使能与高边保护架构2025-09-02 1923

-

集才华与美貌于一身是什么体验?2016-03-22 11179

-

意法半导体发布新款STSPIN电机驱动器,可简化中低功率电机驱动设计,提高电机控制的灵活性2018-08-29 3443

-

48输出LED驱动器让显示牌更加不同2018-09-12 2404

-

全能ADC的使用2019-07-24 1404

-

通过视觉和运动的紧密集成,提高准确度和灵活性2016-03-21 629

-

MCU 集成式模数转换器提供 MSP 应用灵活性2017-04-26 1125

-

利用100W的智能功率模块来提升功能集成度、能效和灵活性2017-09-21 7657

-

ADI发布同步解调器ADA2200:集成度、性能、灵活性和功耗均达行业最佳水平2018-09-13 3695

-

DN127-3V和5V 12位轨对轨微功率DAC集灵活性和性能于一身2021-05-07 642

-

意法半导体为MOLED显示器开发出高集成度电源管理芯片2022-04-25 3452

-

各行各业的数据采集:ADAQ7980 集成的灵活性2023-06-30 1147

-

沁恒网络芯片,自研技术解锁集成度与灵活性2025-12-17 415

全部0条评论

快来发表一下你的评论吧 !