Altium Designer 25.2.1版本新功能解析

描述

Altium Designer 25.2.1

发布时间:2025年1月14日

Altium Designer 25.2.1 离线包

15天免费试用 Altium Designer

PCB设计改进

ODB++有意短路(开放测试版)

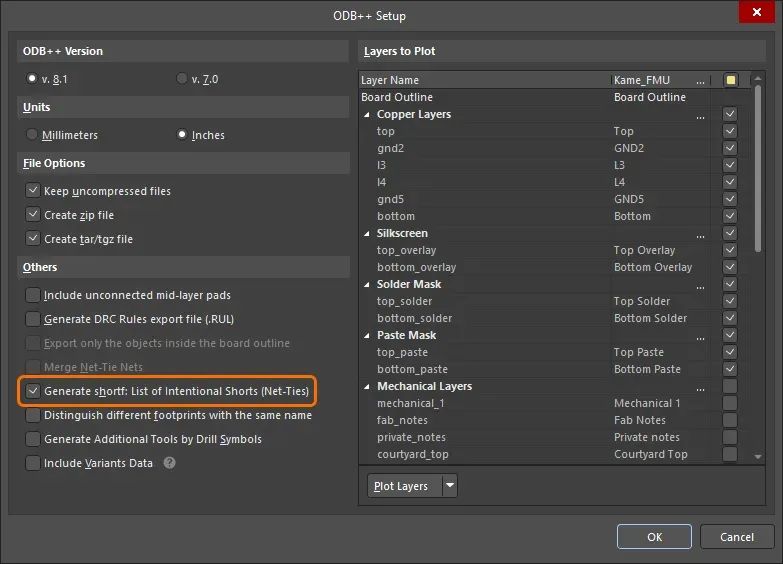

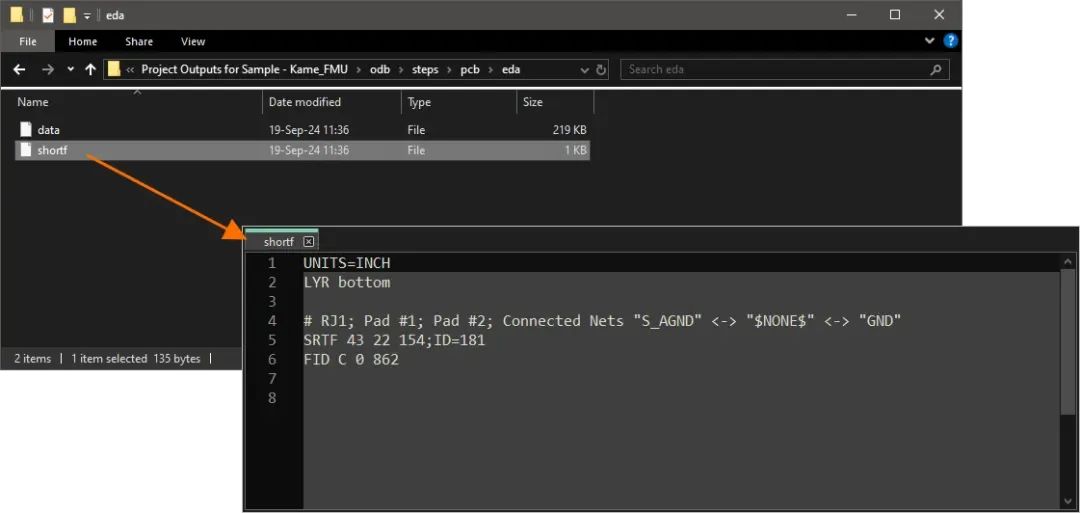

此版本增加了在生成 ODB++ v8.1 输出时生成网络和铜基元列表(故意允许短路(“网络连接”))的支持。您无需再向制造商发送两份文档,一份是包含合并网络连接的ODB++数据包用于制造,另一份是不包含合并网络连接的用于在线测试。

此功能利用了ODB++ v8.1对生成“shortf”文件的支持,该文件包含有意短路的列表。在Altium Designer中访问和使用此功能时,ODB++设置对话框中提供了一个新选项。该选项“生成shortf:有意短路(Net-Ties)列表”仅在生成v8.1格式的输出时可用。启用此选项后,合并网络连接(Merge Net-Tie Nets)选项将被禁用,反之亦然。生成的shortf文件位于步骤输出的“eda”子文件夹下。

此功能处于开放测试版阶段,并在高级设置对话框中启用ODB.IntentionalShorts选项时可用。

更多信息,请参阅准备制造数据页面。

PCB协同设计改进

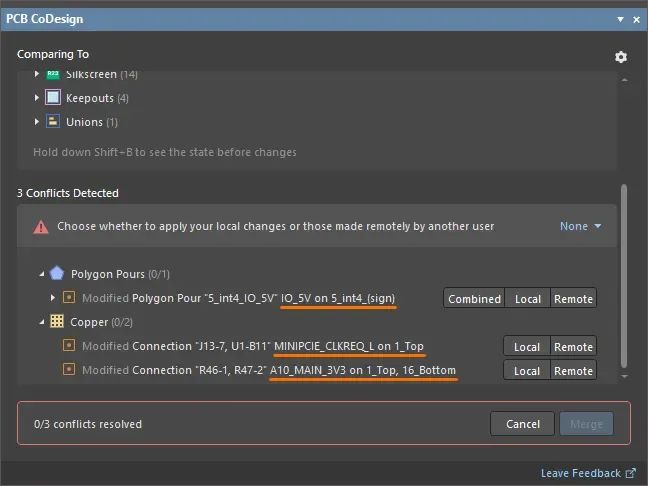

铜皮变化展示改进

对于检测到的铜皮变化(弧形、连接、焊盘、走线等),现在将在PCB协同设计面板中显示相关的网络名称。此外,对于连接,现在还会显示该连接所代表的所有层。

约束管理器改进

增强的xNet生成

现在,xNet的生成支持具有两个以上引脚的串行元件。以下串行元件受支持:

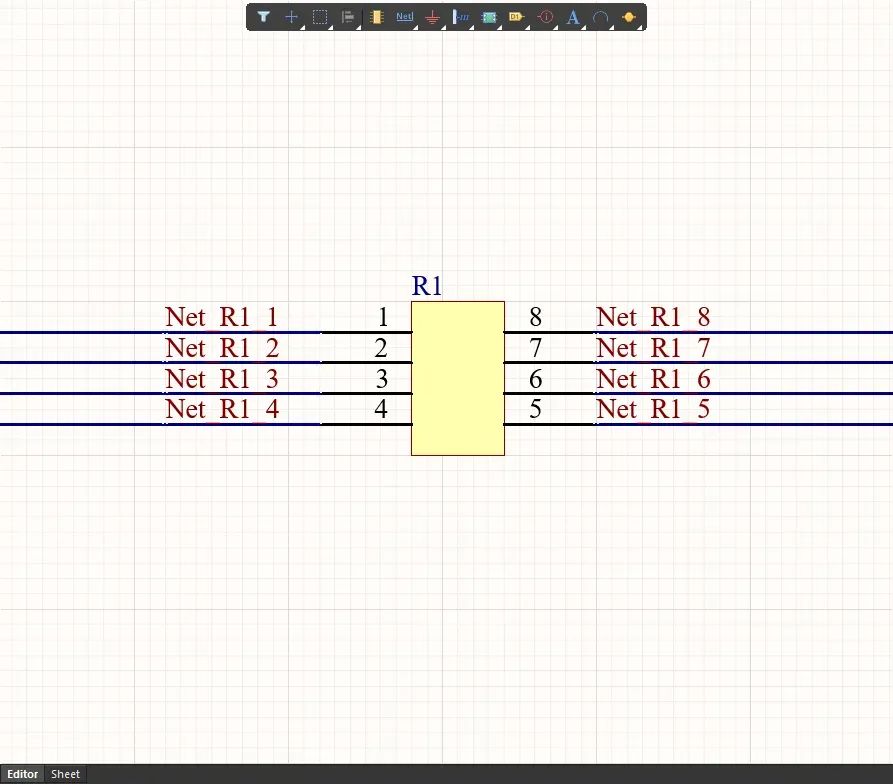

偶数引脚的双列直插式元件:从连接到元件第一个和最后一个引脚的网络开始生成xNet,然后是第二个和倒数第二个引脚,以此类推。

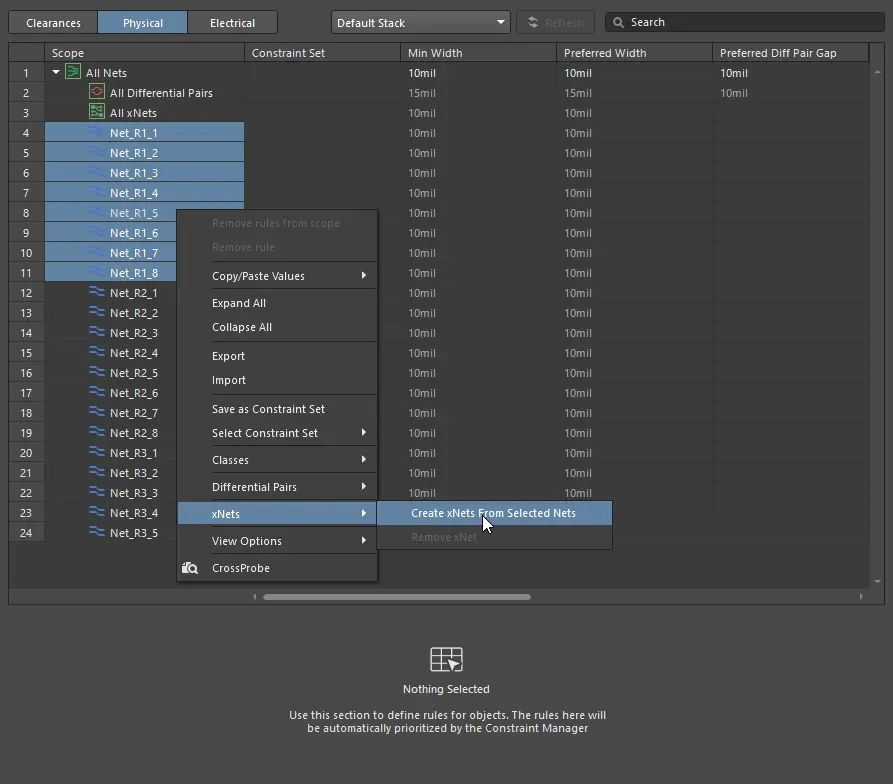

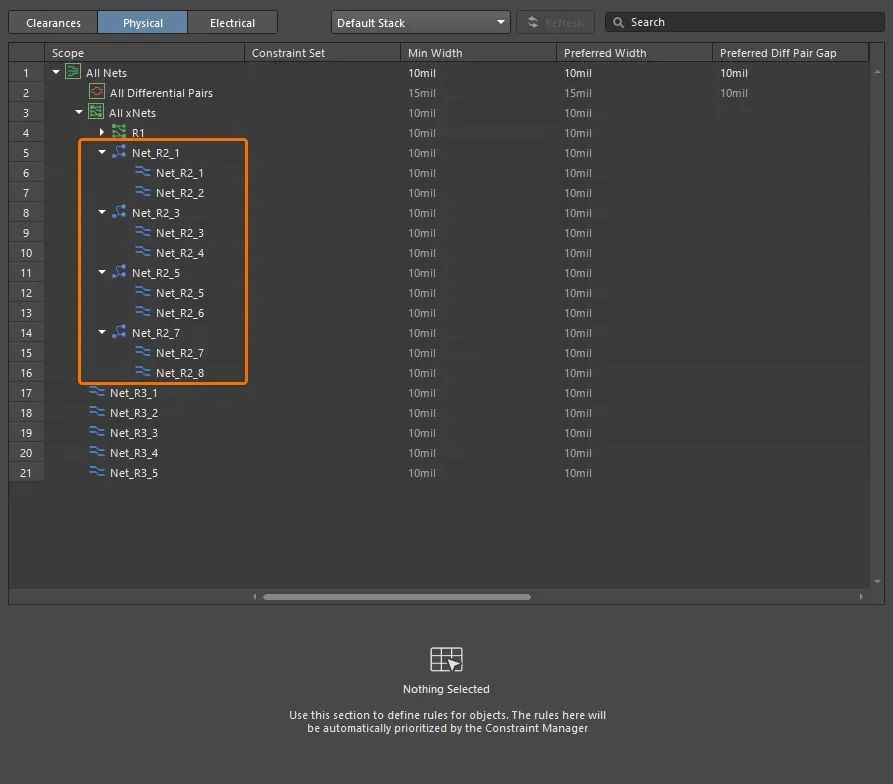

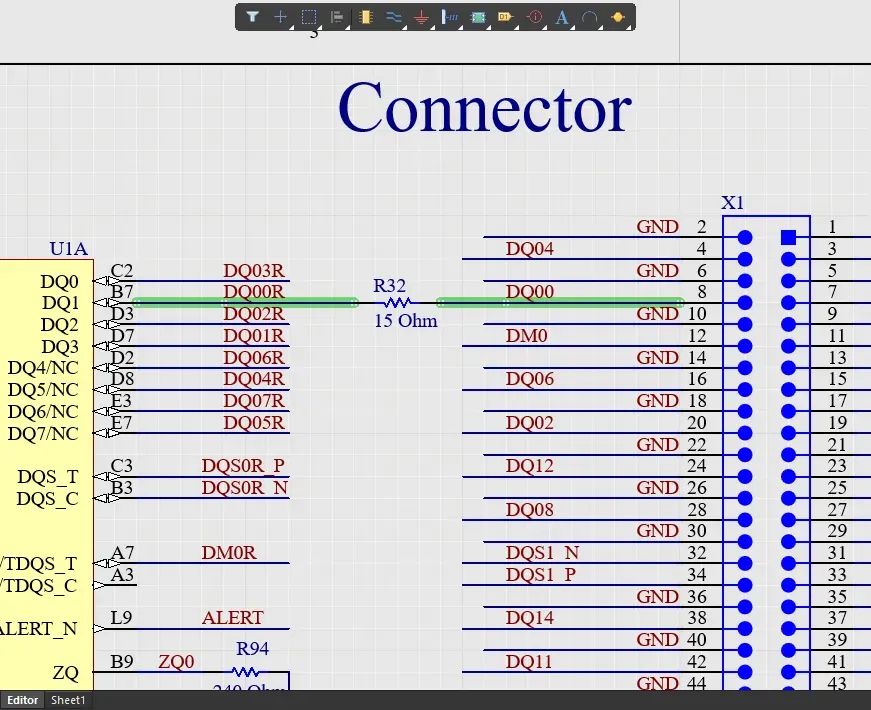

偶数引脚双列直插式元件及其连接网络的示例。

在约束管理器中选择这些网络时,将创建xNet。

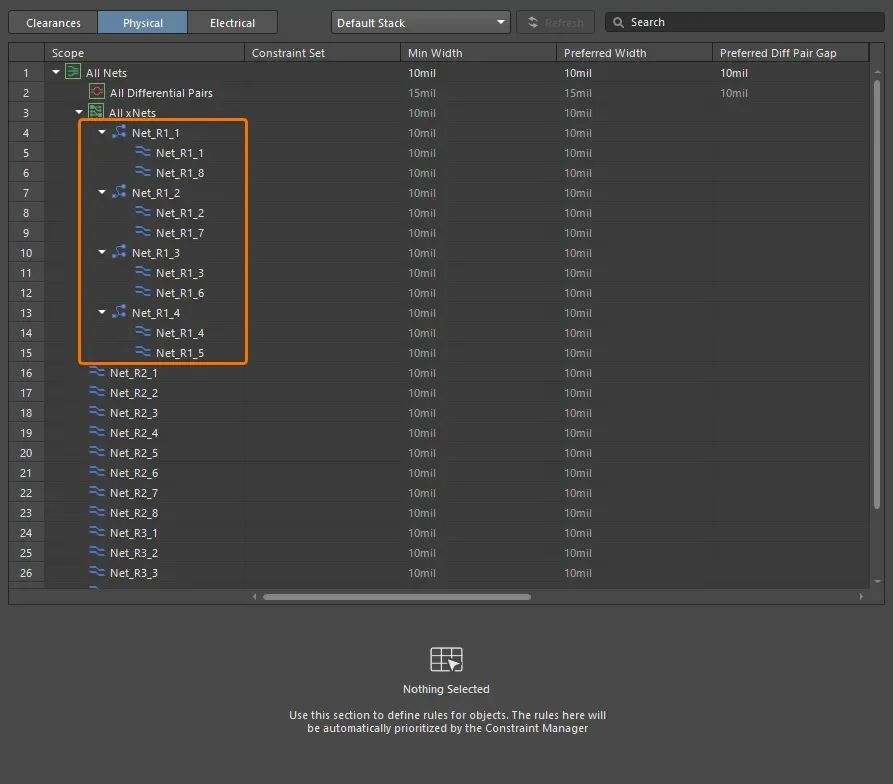

xNet是根据双列直插式元件的相应成对网络生成的。

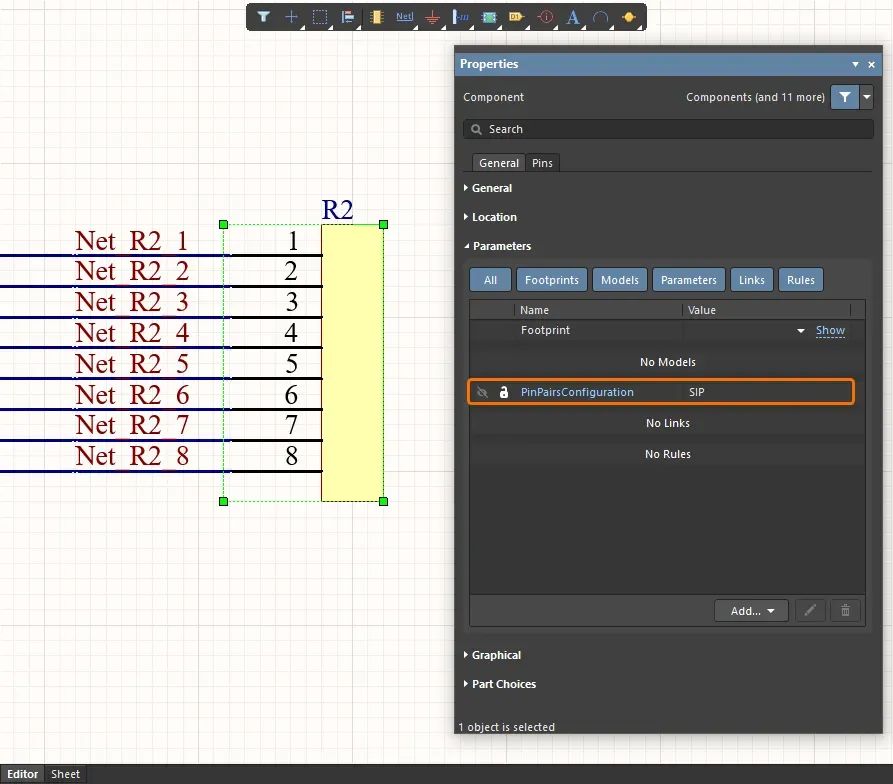

偶数引脚的单列直插式元件:从连接到元件第一个和第二个引脚的网络开始生成xNet,然后是第三个和第四个引脚,以此类推。请注意,元件必须包含一个名为PinPairsConfiguration且值为SIP的参数;否则,xNet将按双列直插式元件的情况生成。

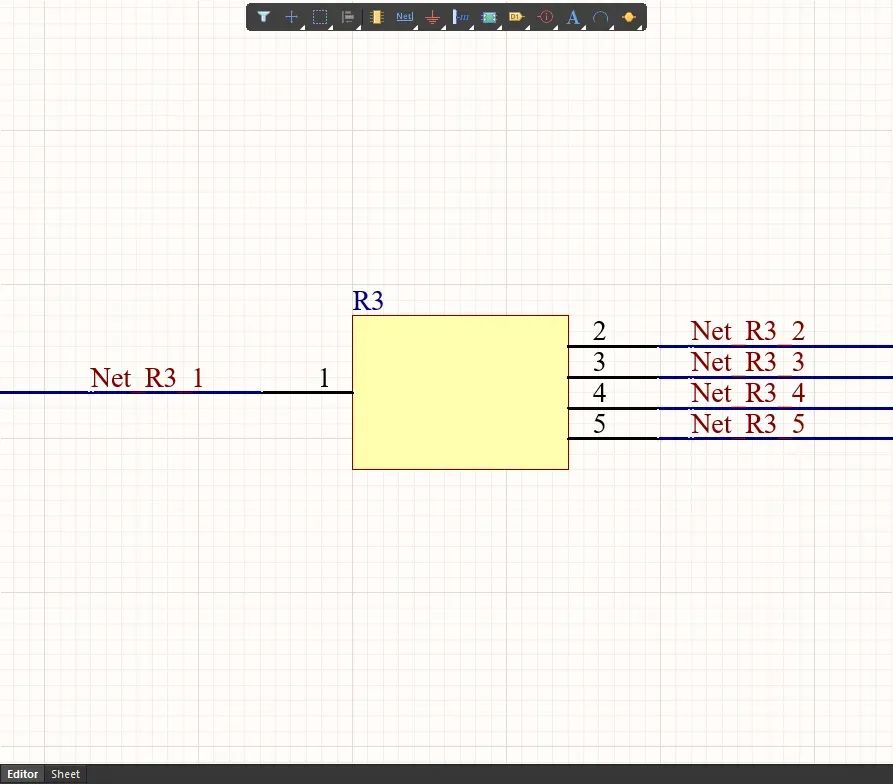

偶数引脚单列直插式元件的示例,这些引脚通过网络相互连接。请注意,该元件包含一个特殊参数PinPairsConfiguration = SIP。

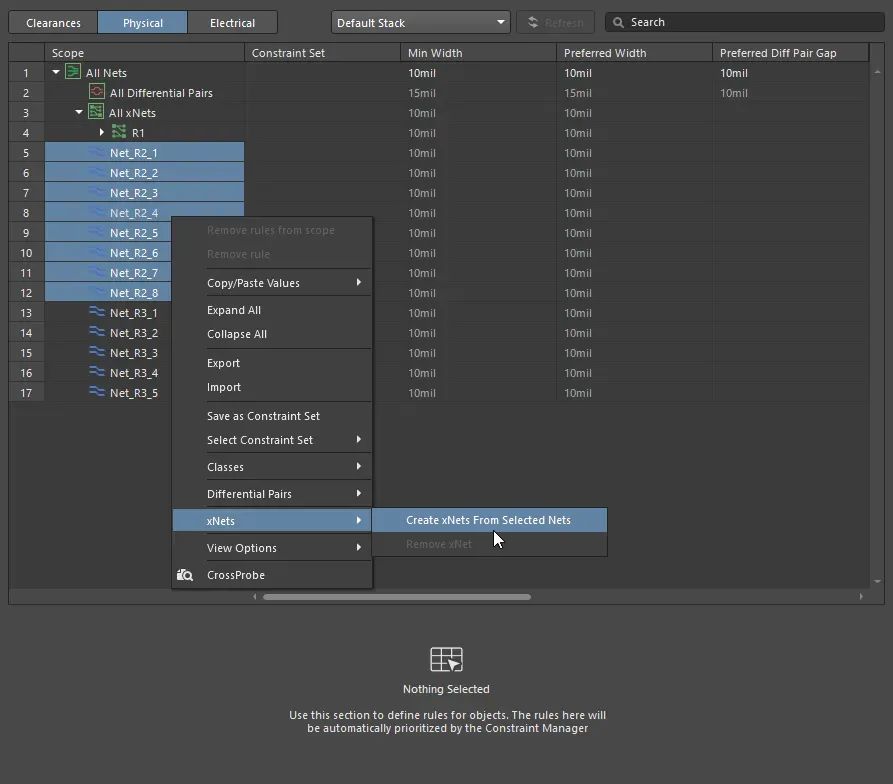

当在约束管理器中选择这些网络时,将创建xNet。

对于单列直插式元件,xNet是根据相应的成对网络生成的。

奇数引脚元件 – 从连接到元件所有引脚的网络生成xNet。

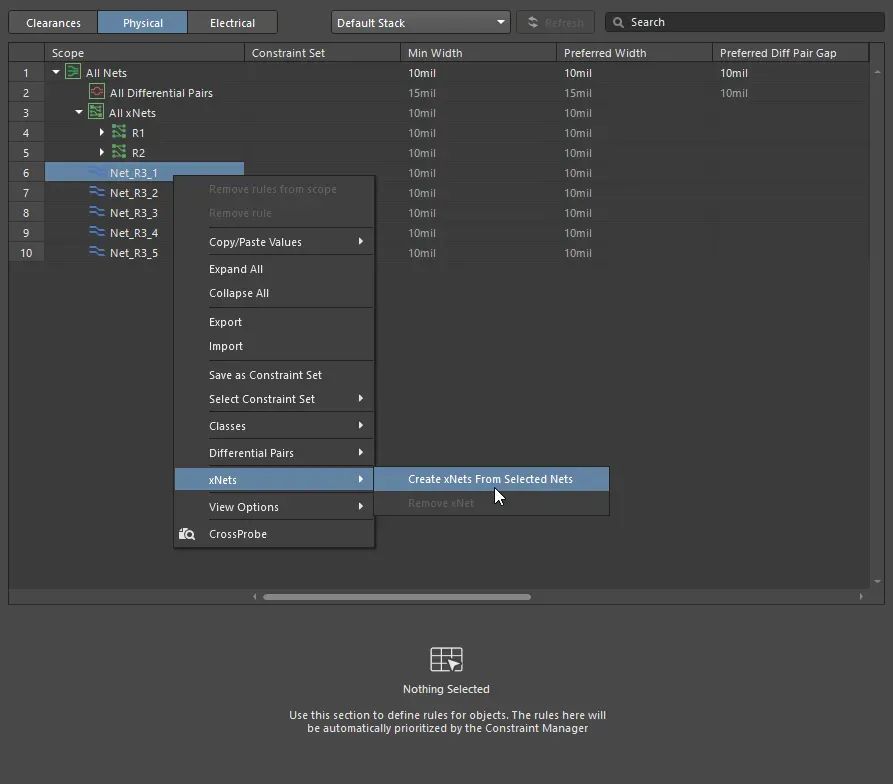

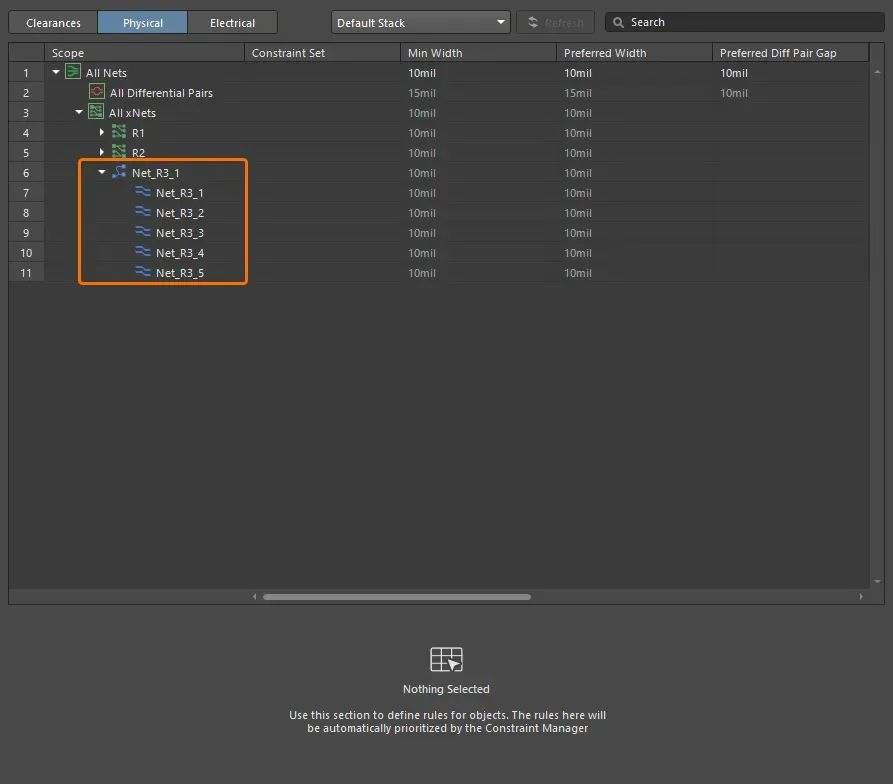

奇数引脚元件及其连接网络的示例。

在约束管理器中选择这些网络中的一个时,将创建xNet。

这些网络都用于生成xNet。

更多信息,请参阅使用约束管理器定义设计要求页面。

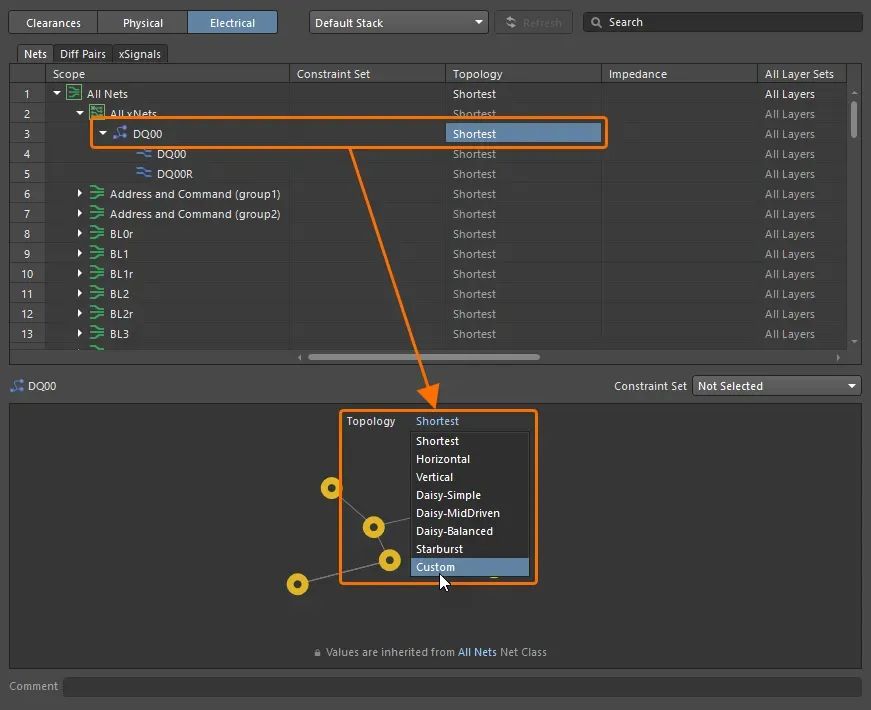

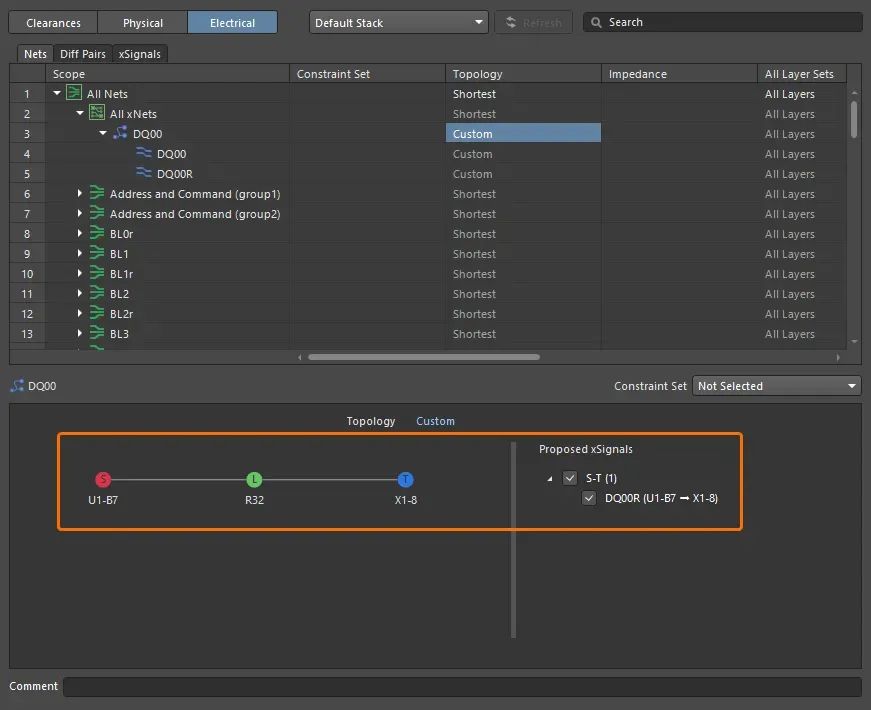

简单情况下xSignal的自动创建

对于简单的xNet(每对网络之间有一个源、一个目标和一个离散元件),现在在约束管理器中选择自定义布线拓扑类型后,将自动创建自定义拓扑和xSignal。

xNet通过单个离散元件从单个源传输到单个目标。

在约束管理器中为此xNet选择了自定义拓扑类型。

从xNet中自动创建了自定义拓扑(以及基于该拓扑的xSignal)。

更多信息,请参阅使用约束管理器定义设计要求页面。

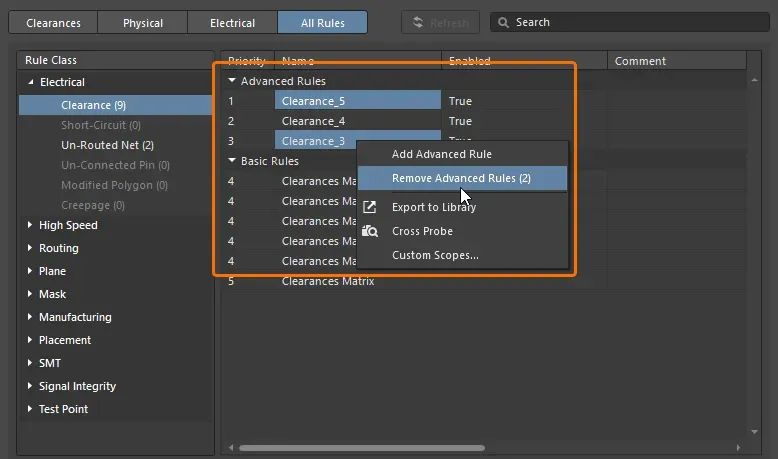

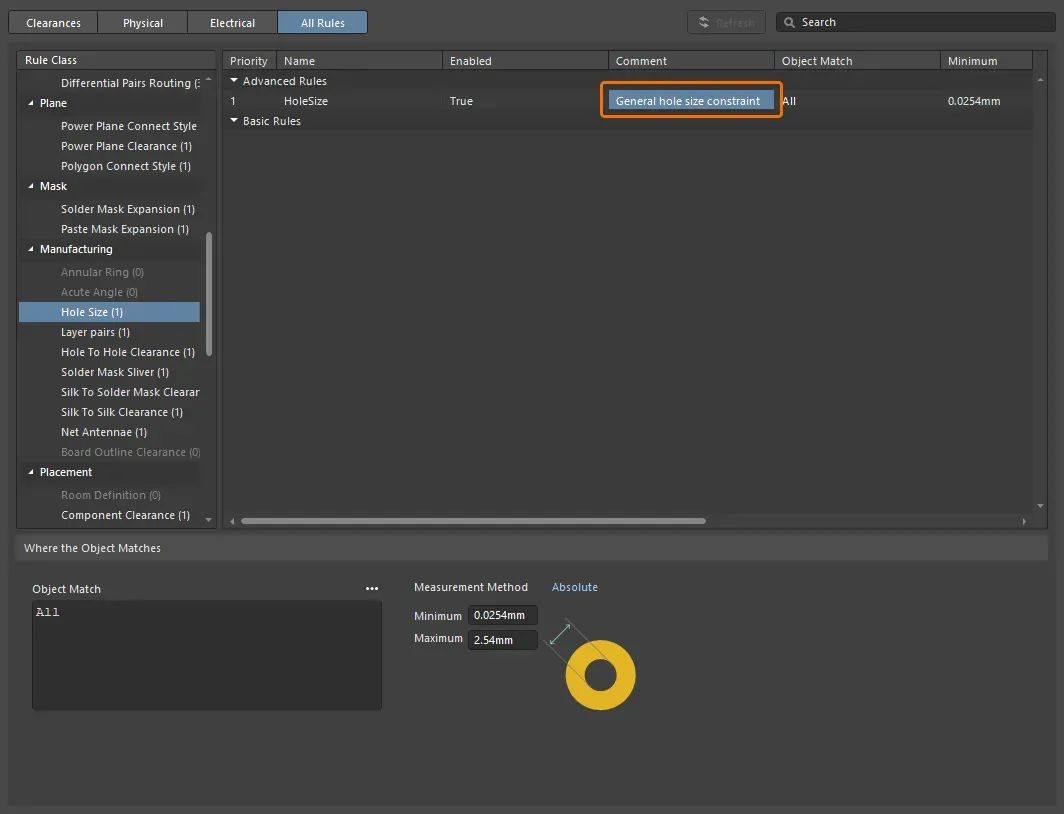

高级规则的删除

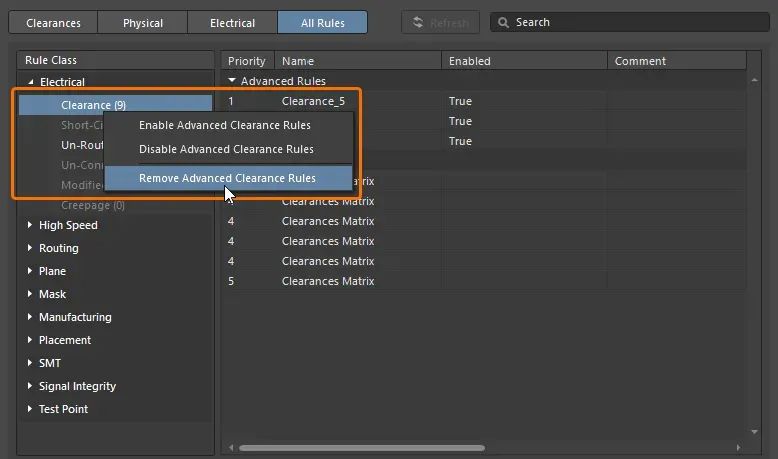

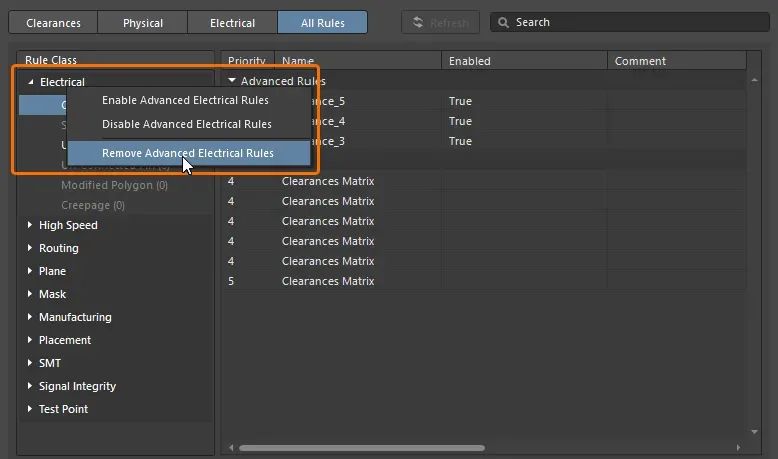

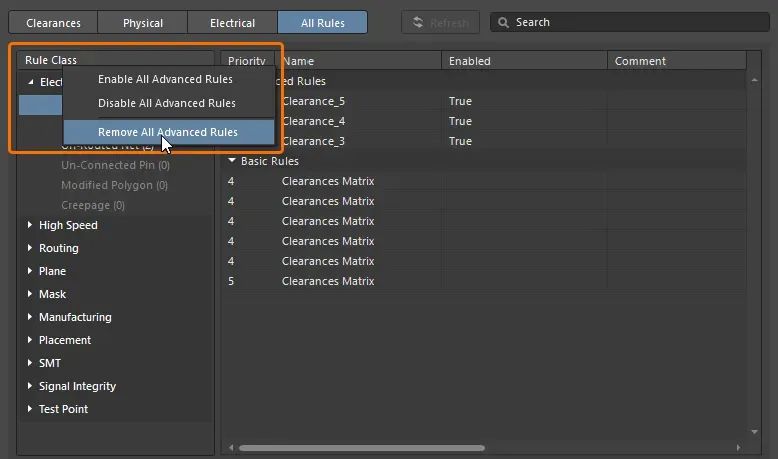

现在,当从PCB访问约束管理器的“所有规则”视图时,可以一次删除多个高级规则。使用Ctrl+单击、Shift+单击或单击并拖动来选择多个高级规则,然后右键单击并选择“删除高级规则(x)”。'x'表示将要删除的规则数量。还可以通过右键单击规则类树中相应条目的上下文菜单中的命令,删除特定类型、类别或所有高级规则。规则将立即删除,无需确认。

右键单击多个选中的规则以删除它们。

右键单击规则类树中的规则类型条目以删除此类型的高级规则。

右键单击规则类树中的规则类别条目以删除此类别中的高级规则。

右键单击规则类标题以删除所有高级规则。

更多信息,请参阅使用约束管理器定义设计要求页面。

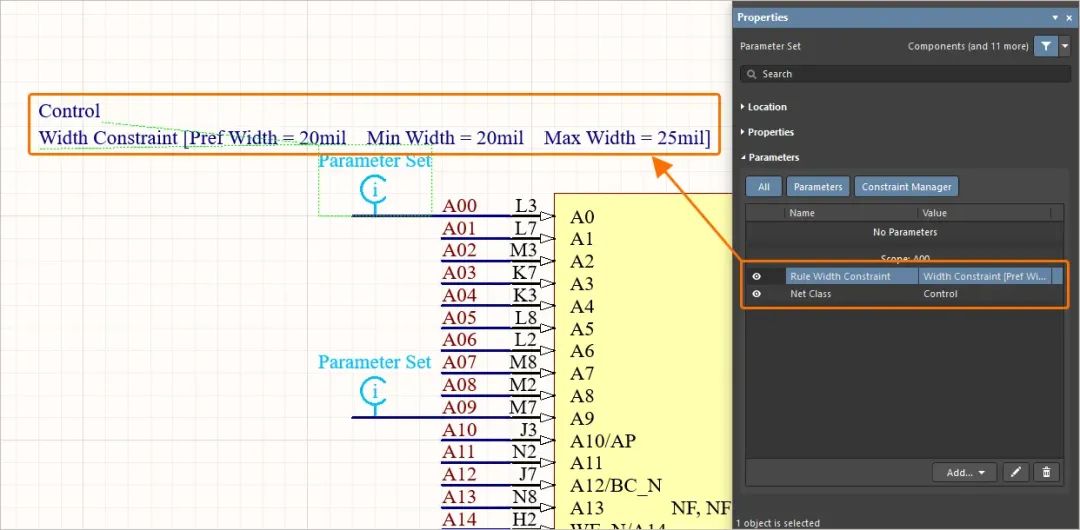

显示参数集指令数据

对于附加到单根导线的参数集指令,增加了在原理图图纸上该指令附近显示来自约束管理器(网络/差分对类名称和规则设置)的相关数据的能力。此外,对于包括已定义网络类且附加到覆盖层的参数集指令,在与约束管理器同步/导入后,现在可以在设计空间中切换网络类指令信息的显示。选择指令时,使用属性面板中相应数据条目左侧的可见性控制( )来执行此操作。

)来执行此操作。

更多信息,请参阅使用约束管理器定义设计要求页面。

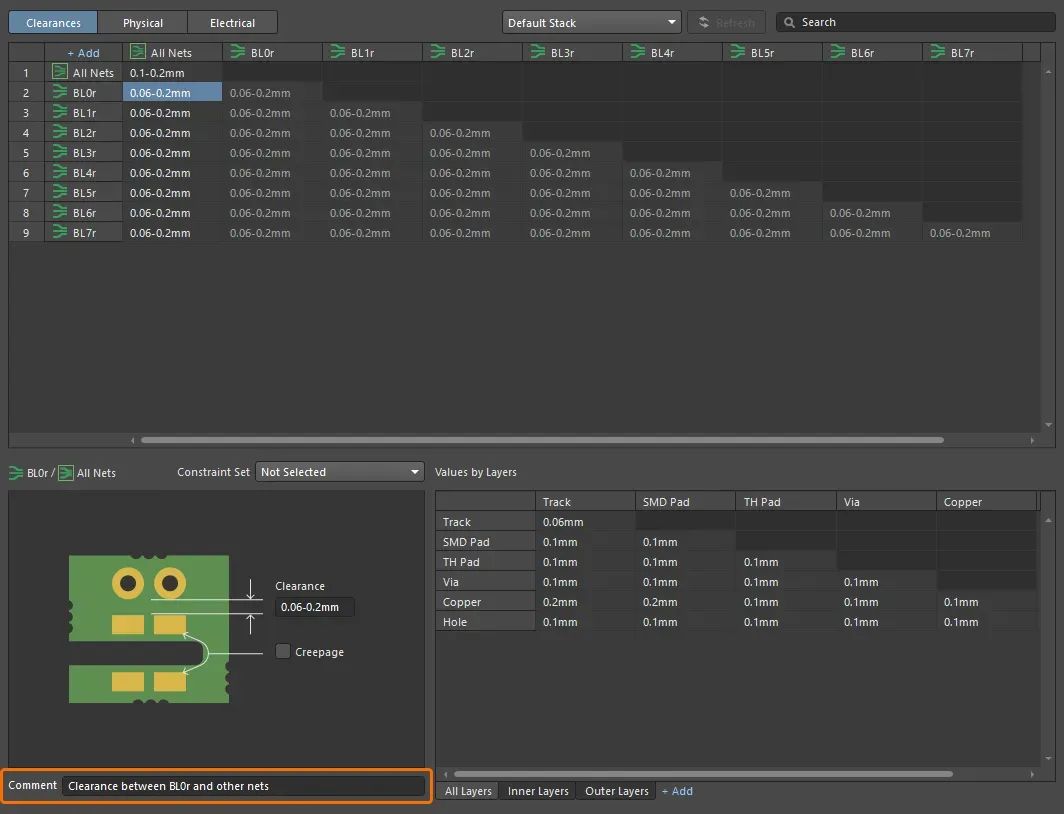

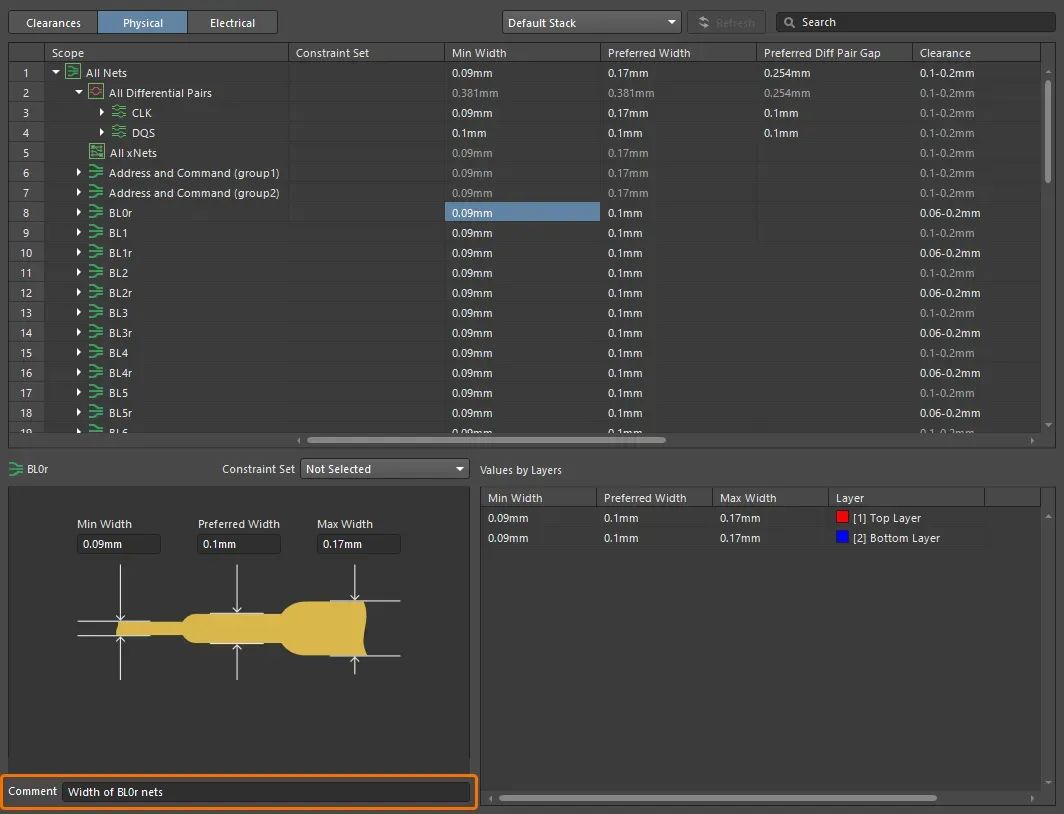

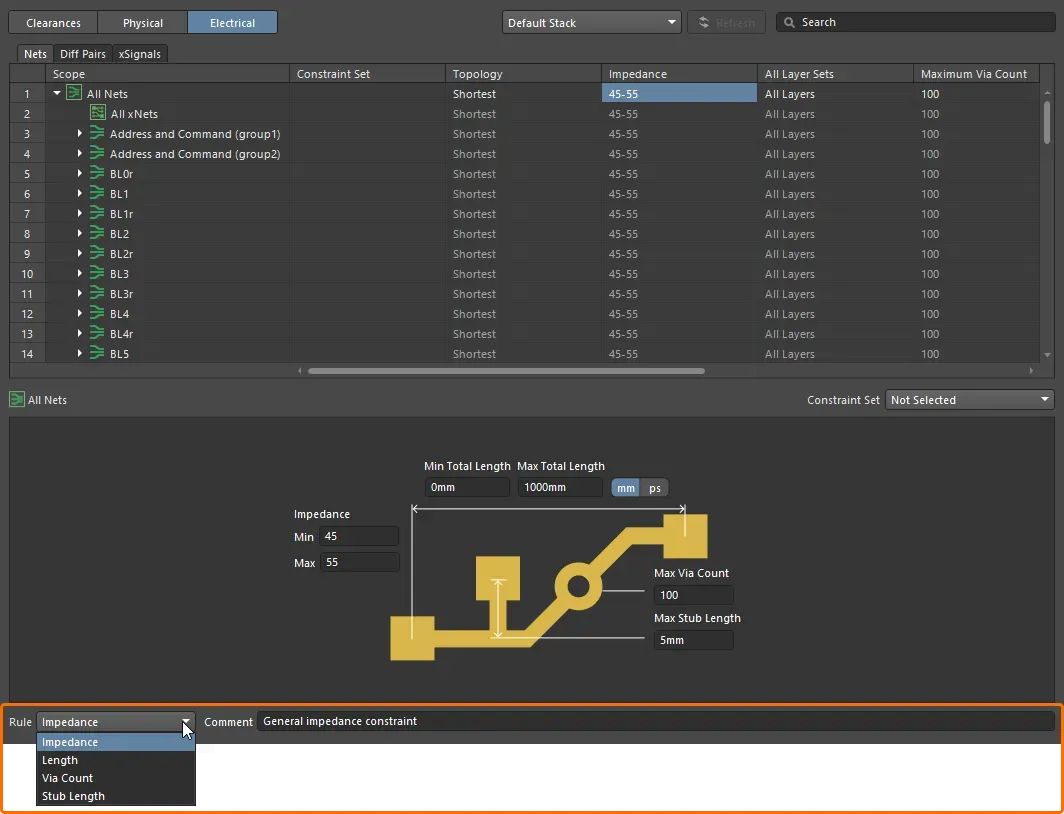

所有视图中的注释支持

现在,您可以在约束管理器的任何视图中的约束/规则中添加注释。在“间距”、“物理”或“电气”视图底部的约束管理器“注释”字段中,或在“所有规则”视图的“注释”列中输入所需注释。

在间距视图、物理视图和电气视图中为约束添加注释。

在间距视图中为约束添加注释。

在电气视图中为约束添加注释。请注意,在上面显示的示例中,约束管理器的下半部分允许为不同的规则(阻抗、长度、过孔数和Stub长度)定义约束,并且您可以通过使用“规则”下拉菜单切换当前规则来为每个规则定义单独的注释。

在所有规则视图中为约束添加注释。

Wire Bonding 改进

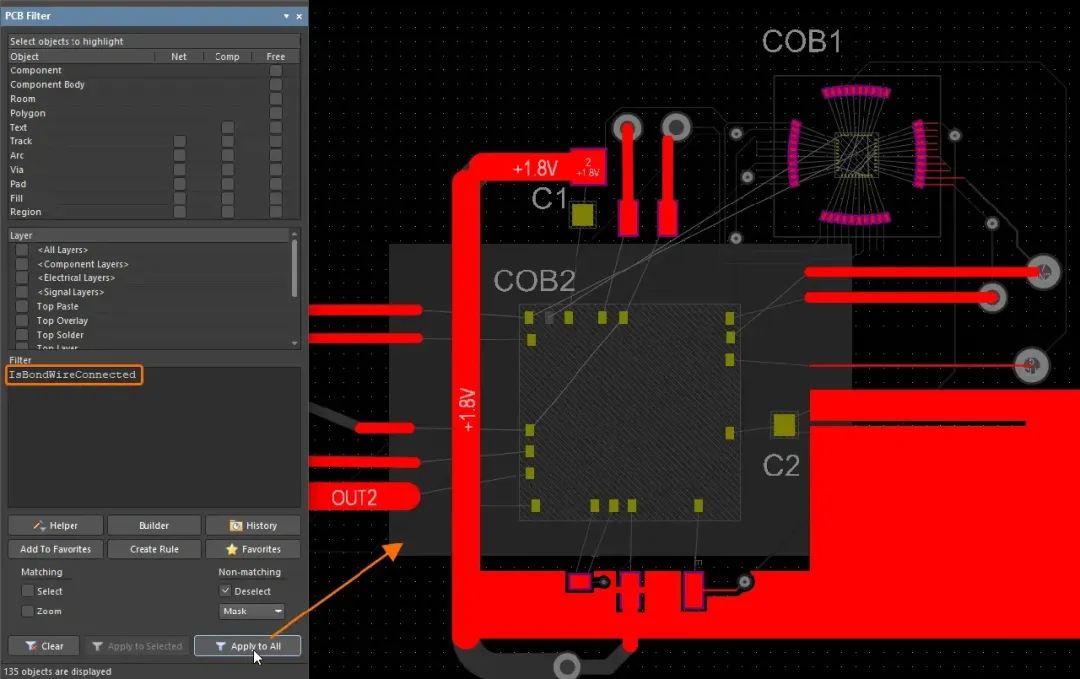

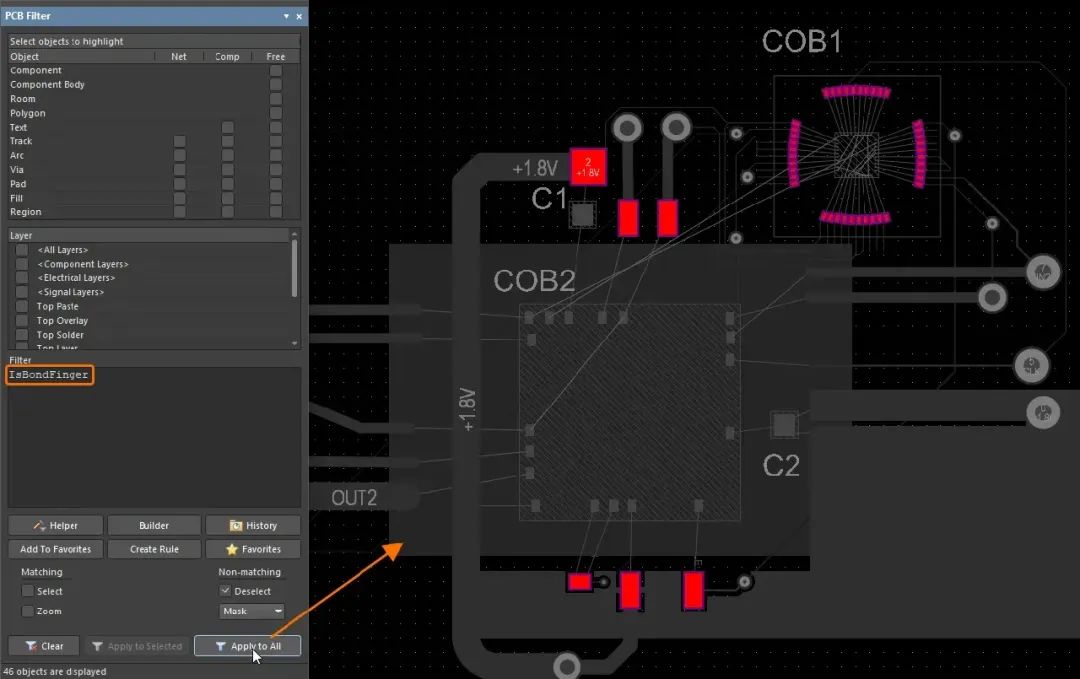

Wire Bonding查询关键字功能的扩展

在构建用于在PCB或PCB库中过滤对象的查询表达式时,现在可以使用两个查询语言关键字—— IsBondWireConnected 和 IsBondFinger。

更多信息,请参阅Wire Bonding 页面。

裸片焊盘与3D实体的绑定增强

裸片焊盘与重叠3D实体的绑定已得到增强。现在,裸片焊盘仅与放置在裸片层(称为裸片实体)上的3D实体链接。裸片焊盘现在将与这个重叠的裸片实体链接,并继承其高度。对裸片焊盘或裸片实体(位置、大小等)的任何几何修改都会更新链接,使裸片焊盘的高度与其链接的裸片实体保持同步。

如果裸片焊盘下有多个重叠的裸片实体,裸片焊盘将与来自与裸片焊盘相同元件的裸片实体链接。如果同一元件中有多个裸片实体(或裸片焊盘重叠多个自由裸片实体),裸片焊盘将与最大高度的裸片实体链接。

请注意,如果在使用Altium Designer的旧版本中,裸片焊盘与除裸片层之外的其他层上的3D实体链接,则在新版本中打开文档时将不支持此绑定。需要为3D实体选择正确的裸片层。

更多信息,请参阅Wire Bonding 页面。

数据管理改进

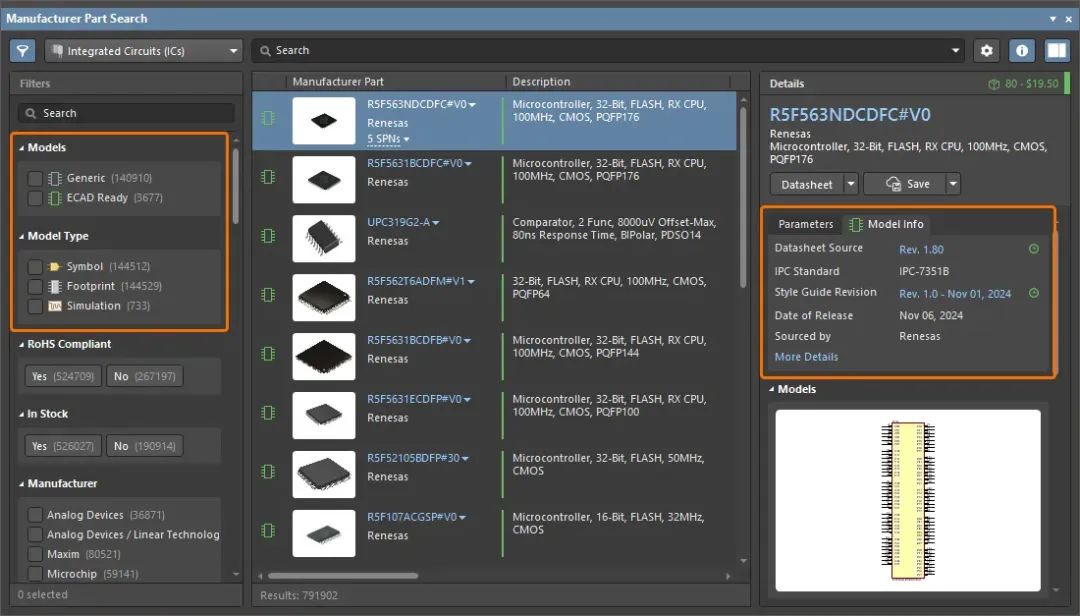

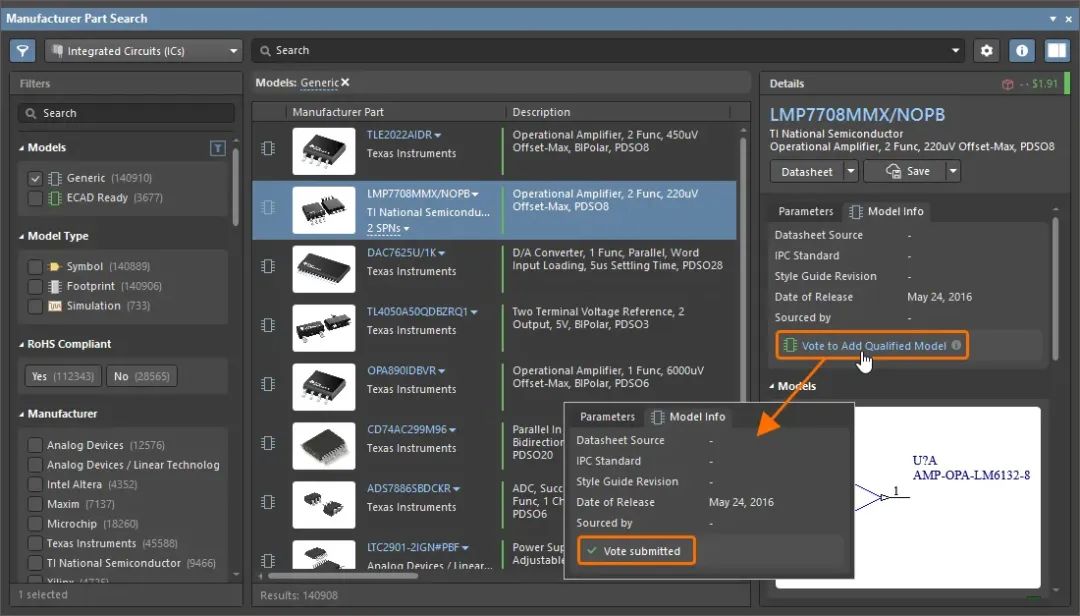

支持合格模型

此版本引入了合格模型的概念。制造商部件搜索面板中可用的制造商部件信息已得到增强,包括有关部件模型(原理图符号、PCB封装和/或仿真模型)的详细信息,以及它们是否被视为“通用” ( ) 或“ECAD就绪” (

) 或“ECAD就绪” ( )。在后一种情况下,这些模型已根据数据表、IPC标准和相关样式指南修订版进行了“合格”评定。

)。在后一种情况下,这些模型已根据数据表、IPC标准和相关样式指南修订版进行了“合格”评定。

使用制造商部件搜索面板的“筛选器”窗格中的“模型”筛选器,将列表限制为具有相应级别模型的部件。此外,您还可以使用“模型类型”筛选器将列表限制为具有相应类型模型的部件。

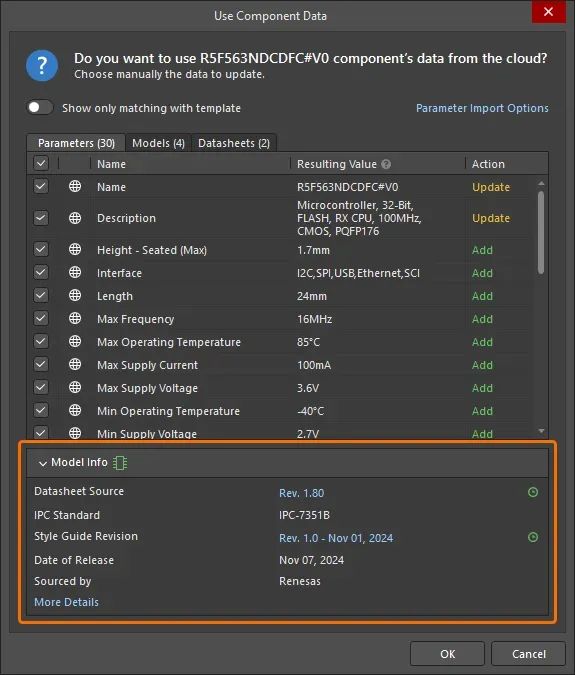

当将具有ECAD就绪模型的元件保存到连接的Workspace时,此相同信息将显示在“使用元件数据”对话框中。

对于具有通用模型的元件,您有权投票以获得/添加合格模型。

当在“高级设置”对话框中启用EDMS.QualifiedModels选项时,此功能可用。

更多信息,请参阅搜索制造商部件页面。

导入/导出改进

xDX Designer自定义连接器支持(开放测试版)

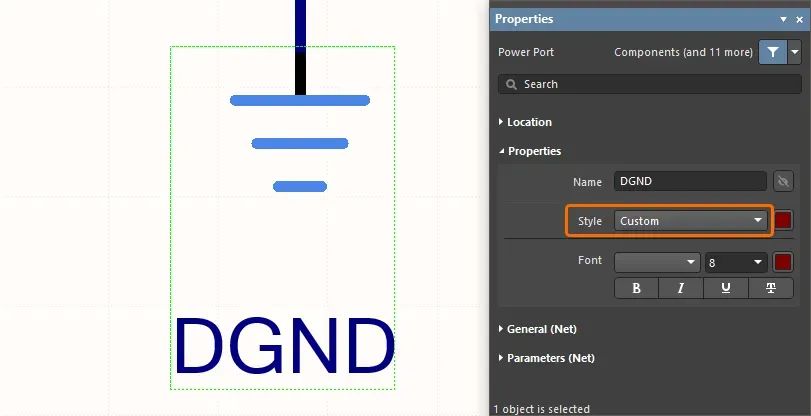

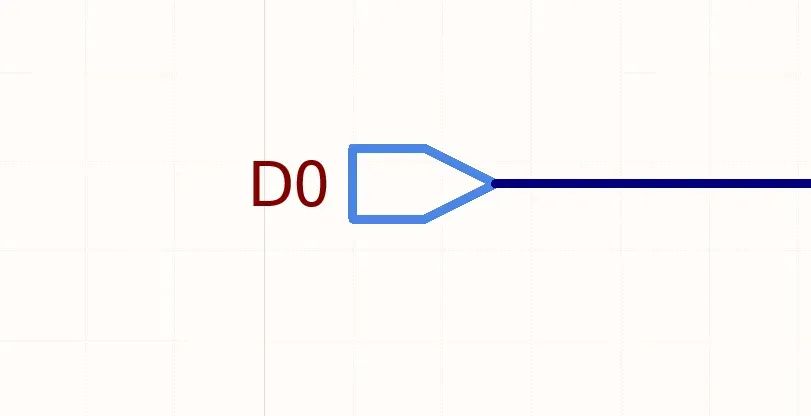

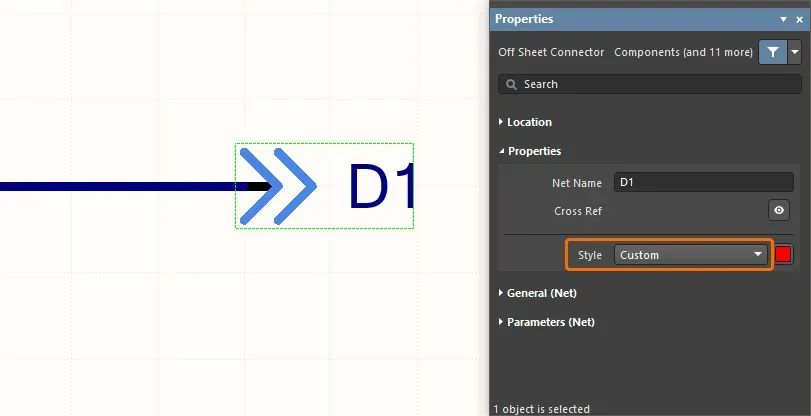

当通过导入向导导入xDX Designer项目时,生成的原理图文档现在支持自定义端口、自定义电源端口和自定义表外连接器,因此它们具有与原始设计中相同的图形。

从xDX Designer项目中导入的自定义电源端口。请注意,其“样式”属性设置为“自定义”值。

从xDX Designer项目中导入的自定义端口。

从xDX Designer项目中导入的自定义表外连接器。请注意,其“样式”属性设置为“自定义”值。

此功能处于开放测试版阶段,并在 “高级设置”对话框中启用Importer.UseCustomConnectors选项时可用。

更多信息,请参阅从xDX Designer或DxDesigner导入设计页面。

Altium Designer 25.2中完全公开的功能

以下功能现在随着此版本的发布而正式公开:

布线缩颈规则 – 自24.8版本起可用

布线自动收缩 –自24.8版本起可用

差分对的动态相位匹配 – 自24.10版本起可用

更多版本发布说明

-

Altium Designer 24.7.2版本新功能图解说明2024-08-05 5927

-

原创Altium Designer 17全程安装及新功能视频教程2016-11-20 13029

-

Altium Designer®18新功能先睹为快2017-06-13 10986

-

无私分享,Altium Designer 18 最新18.1.7版本2018-09-07 12576

-

Altium Designer 20 新功能官方直播2019-12-27 4192

-

Altium Designer 6.3 新功能教程2009-09-28 776

-

Altium Designer 6.8的新功能介绍2011-02-13 1584

-

ALTIUM DESIGNER15以下版本下载2015-08-17 5219

-

Altium designer Draftsman的使用2016-12-09 2406

-

Altium Designer14版本下载入口2017-01-05 1276

-

altium_designer_16.1.11_软件下载2018-04-03 1660

-

SOLIDWORKS 2023新功能揭秘!SOLIDWORKS Simulation 2023版本2022-12-08 4611

-

altium designer哪个版本稳定2024-01-04 38158

-

Altium Designer 24.10.1版本新功能解析2024-10-18 3856

-

Altium Designer 25.7.1 版本发布,Altium Designer 25.7.1新功能说明2025-06-20 3009

全部0条评论

快来发表一下你的评论吧 !