鳍式场效应晶体管制造工艺流程

描述

文章来源:半导体与物理

原文作者:jjfly686

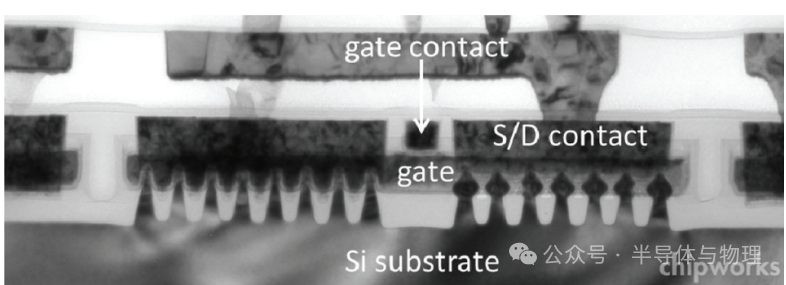

FinFET(鳍式场效应晶体管)从平面晶体管到FinFET的演变是一种先进的晶体管架构,旨在提高集成电路的性能和效率。它通过将传统的平面晶体管转换为三维结构来减少短沟道效应,从而允许更小、更快且功耗更低的晶体管。本文将从硅底材开始介绍FinFET制造工艺流程,直到鳍片(Fin)的制作完成。

1. 初始准备与表面处理

晶圆清洗

在开始任何加工之前,硅晶圆必须经过彻底的清洗过程,以确保其表面没有杂质或污染物。这一步骤对于获得高质量的FinFET器件至关重要。

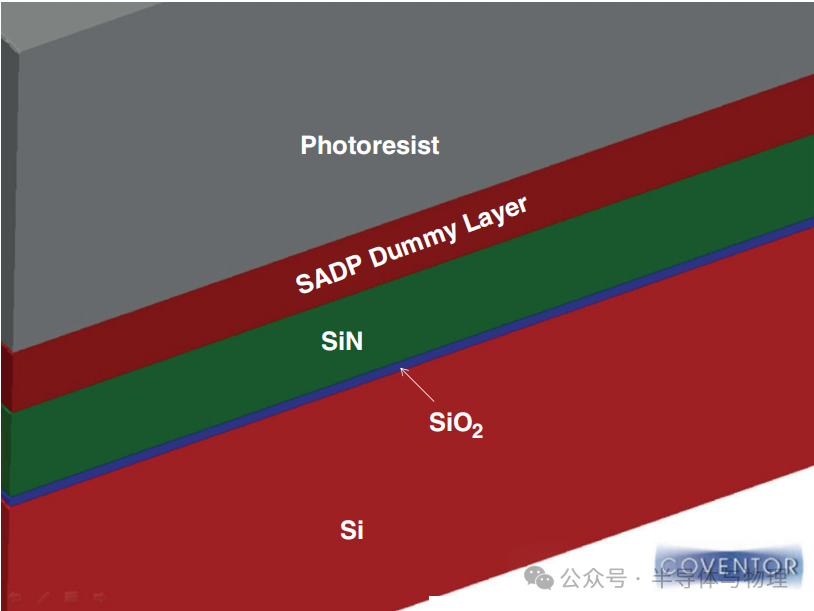

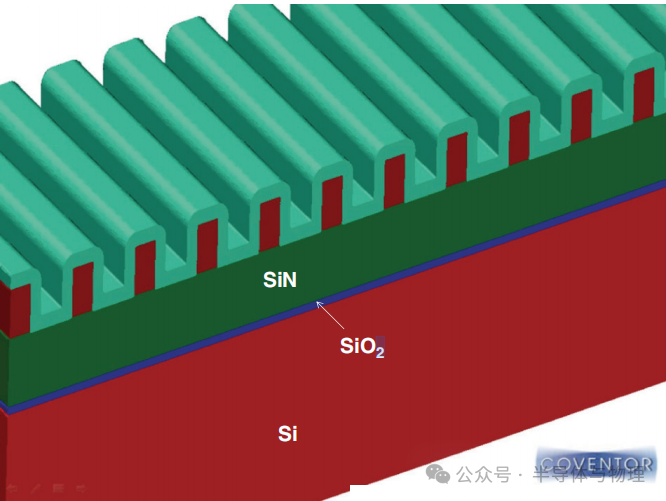

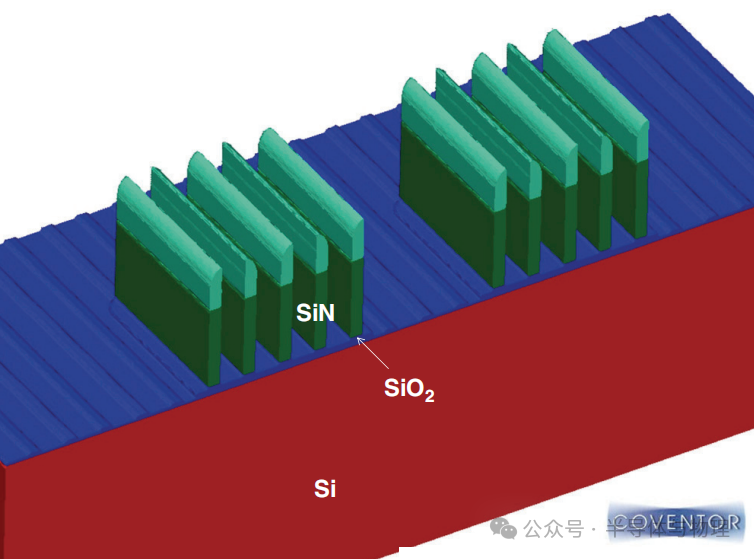

垫氧化层生长

接下来,在硅表面热生长一层非常薄的二氧化硅(SiO2),作为垫氧化层。这一层不仅保护了硅基板免受后续处理的影响,而且为之后的氮化硅沉积提供了良好的界面。

氮化硅沉积

随后,通过化学气相沉积(CVD)或其他方法,在垫氧化层之上沉积一层氮化硅(SiN)。氮化硅在这里扮演双重角色:它既作为硬掩膜(HM),用于指导硅刻蚀以形成鳍片;又作为CMP(化学机械抛光)停止层,确保STI氧化物平坦化过程中不会过度侵蚀下面的材料。

2. SADP技术的应用

由于鳍片间距在先进节点(如22nm或14nm)下非常小,单次193nm浸没式光刻无法实现所需的精细度,因此引入了自对准双重图案化(SADP)技术来增加图案密度。

SADP假图案层沉积

首先,在氮化硅硬掩膜上沉积一层临时材料(例如非晶硅a-Si),用作“假”图案层。这种材料需要具备高选择性蚀刻特性,以便于后续步骤中与下面的氮化硅及侧壁间隔物材料区分开来。

光刻胶涂覆与曝光

在整个堆叠结构上均匀地涂覆一层光刻胶,并使用特定的线-空(line-space)图案掩模进行曝光,定义出鳍片的大致位置。这个图案将指下来的蚀刻过程做铺垫。

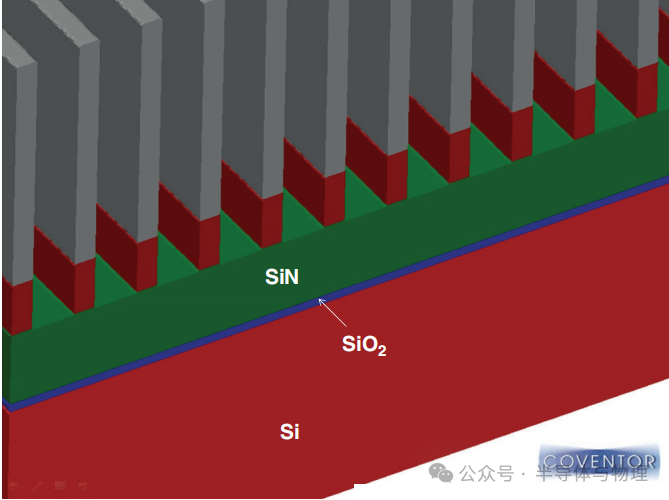

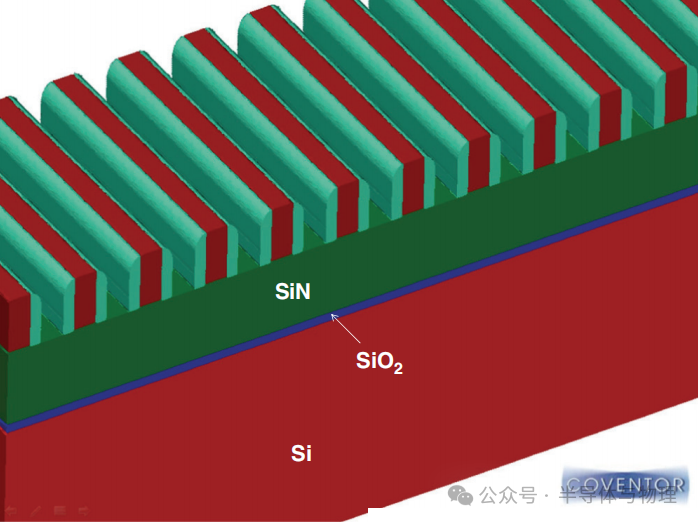

图案转移至假图案层

曝光后的光刻胶经过显影处理后形成鳍片的初始“假”图案。然后,通过等离子体蚀刻将这些图案转移到下面的非晶硅层,直至到达氮化硅表面为止。

移除光刻胶

蚀刻完成后,必须清除光刻胶,通常包括剥离(strip)和清洁两个步骤,以准备下一步操作。此步骤确保了没有任何残留物影响后续的工艺。

保形间隔物沉积

使用ALD沉积一层均匀覆盖所有表面的保形介电层(如SiOx),该层将在之后的蚀刻回退步骤中形成侧壁间隔物。这一层的选择对于最终形成的鳍片形状至关重要。

蚀刻回退形成间隔物

对保形介电层执行各向异性干法蚀刻,仅保留垂直于晶圆表面的侧壁上的介电层,从而形成间隔物。这些间隔物最终会成为实际鳍片的图案模板。如果使用非晶硅作为假图案材料,则可以使用KOH溶液来移除非晶硅,同时几乎不影响硅氧化物间隔物或下方的氮化硅硬掩膜。

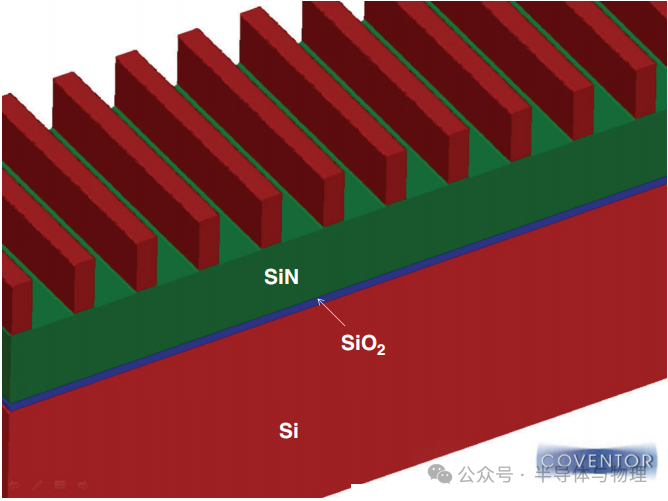

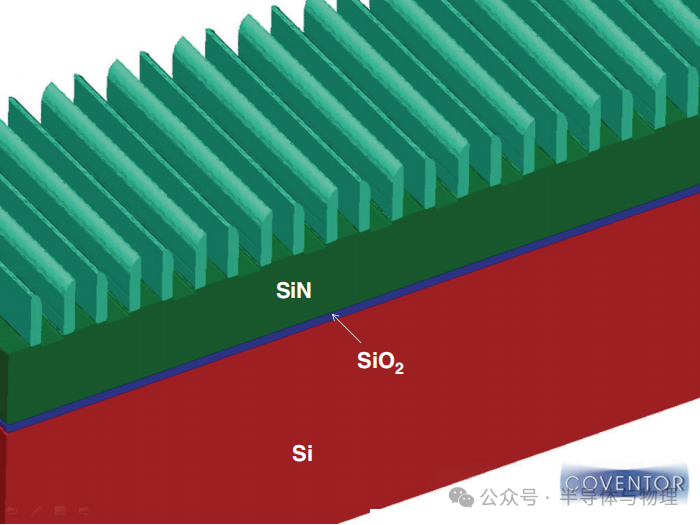

移除假图案

使用选择性高的蚀刻剂移除非晶硅假图案,而不损害硅氧化物间隔物或下方的氮化硅硬掩膜。这样就留下了光刻双倍密度的间隔物图案,对应于之后的鳍。

3. 鳍片图案细化

切割掩模应用

再次涂覆光刻胶并光刻,目的是定义哪些区域将被保留作为鳍片,哪些区域需要去除。这一步骤决定了鳍片的具体布局。

间隔物图案化

使用反应等离子体蚀刻技术,有选择性地移除不需要的间隔物,同时尽量减少对氮化硅硬掩膜的影响。

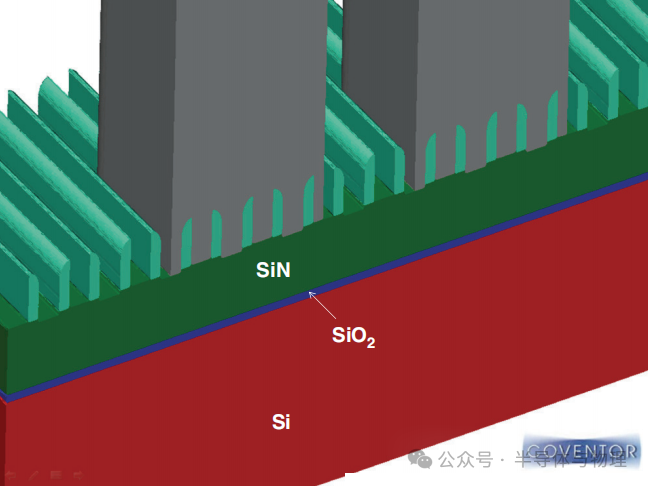

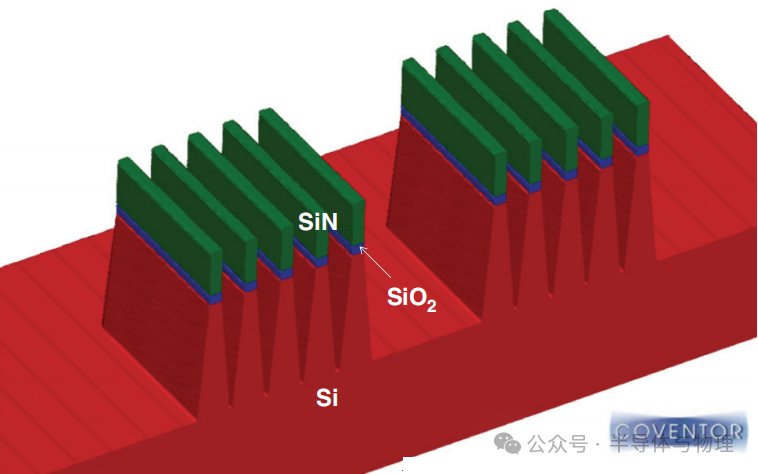

鳍片刻蚀

利用剩余的间隔物作为掩膜,进行主要的硅刻蚀步骤。这一步直接决定了鳍片的形状和尺寸,因此必须严格控制蚀刻参数以获得理想的鳍片结构。在蚀刻过程中,首先移除垫氧化物,然后根据氮化硅硬掩膜的图案蚀刻出硅鳍片。对于14nm 制程芯片来说,鳍片的最小间距可以小至42nm。

上述步骤构成了从硅底材到Fin形成的典型FinFET工艺流程的一部分。整个过程涉及多个精密的工程设计和技术挑战,旨在实现高性能、低功耗的集成电路。随着技术的进步,FinFET工艺也在不断发展,以适应更小的特征尺寸和更高的集成度需求。每一步都精心设计,以确保最终产品的质量和性能达到最优。

-

互补场效应晶体管点火和只用一个场效应晶体管点火与PWM的区别?2024-05-21 524

-

场效应晶体管的作用2023-05-16 3563

-

MOSFET和鳍式场效应晶体管的不同器件配置及其演变2023-02-24 13729

-

场效应晶体管的选用经验分享2021-05-13 1945

-

如何进行场效应晶体管的分类和使用2020-07-02 2092

-

功率场效应晶体管的工作特性2019-10-11 13448

-

场效应晶体管的分类及作用2019-05-08 4252

-

场效应晶体管在电路中的特别应用,你未必全都清楚2019-04-16 3502

-

MOS管与场效应晶体管背后的联系,看完后就全明白了2019-04-15 3305

-

一文让你秒懂场效应晶体管的所有参数2019-04-04 4200

-

如何判断场效应晶体管方向,学会这几步轻松搞定2019-03-29 3867

-

功率场效应晶体管(MOSFET)原理2012-08-20 5404

-

场效应晶体管的分类及使用2010-01-13 975

-

什么是场效应晶体管2009-05-24 7683

全部0条评论

快来发表一下你的评论吧 !